总线与半导体静态存储器实验原理及电路分析

需积分: 10 21 浏览量

更新于2024-08-05

1

收藏 462KB DOCX 举报

"实验三 总线、半导体静态存贮器实验"

本次实验主要涉及计算机组成原理中的两个核心概念:总线传输和半导体静态存储器的使用。实验旨在让学生深入理解这两种技术的工作原理,并掌握实际操作方法。

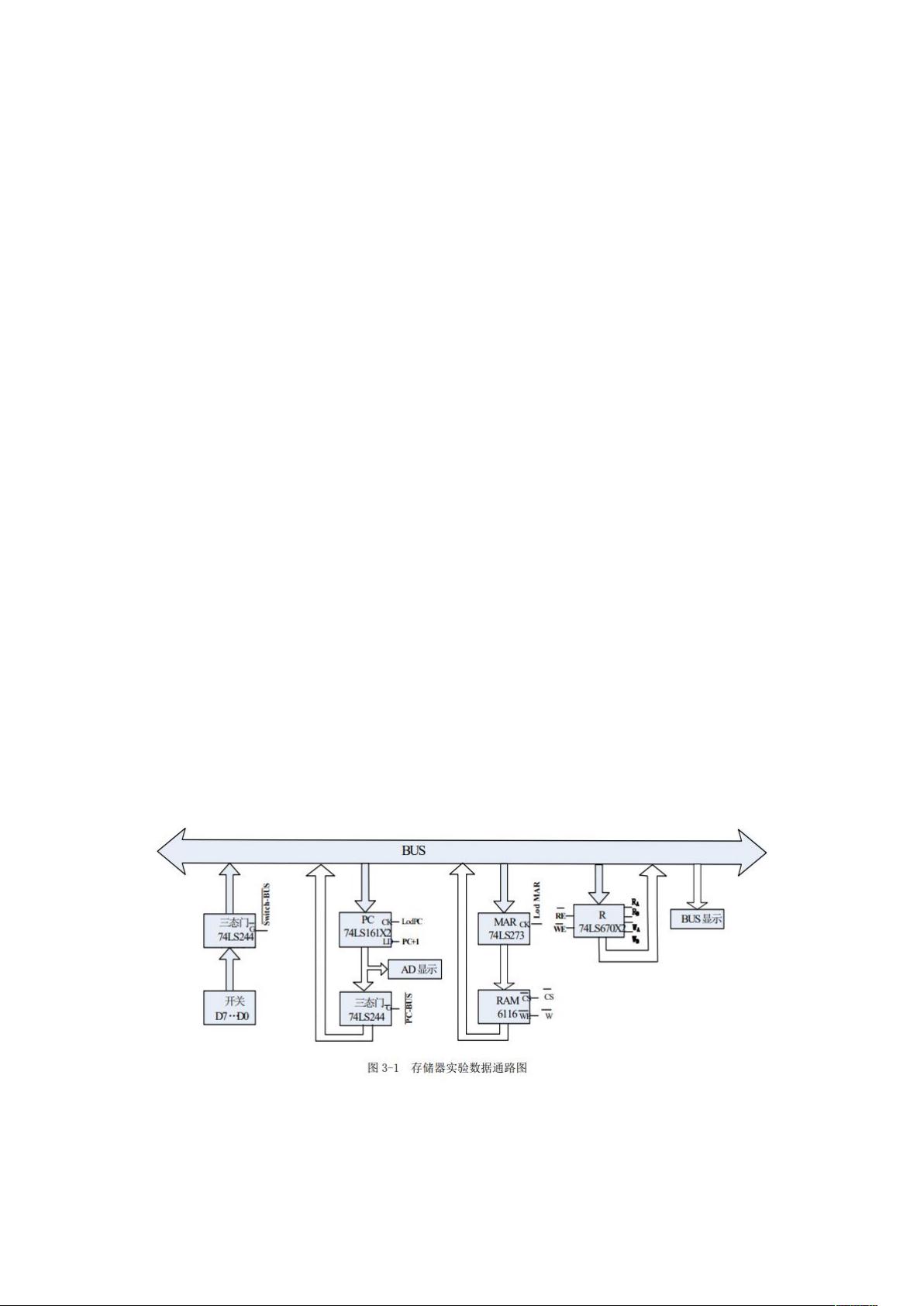

首先,我们讨论总线传送。总线是计算机系统中的一种关键通信机制,它允许不同组件之间共享信息。总线的采用减少了内部连线,提高了系统的可靠性与效率。在实验中,我们重点关注了OC门和三态门,它们是构建总线系统的基础元件。OC门由于其负载能力和阻抗匹配限制,适用于小型总线系统,而三态门则广泛应用于各类总线设计,例如74LS244和74LS373等。建立总线时,需要遵循两个基本原则:互斥性和一致性。互斥性确保同一时刻总线上只有一个信息源发送数据,而一致性则意味着所有挂载在总线上的器件应保持类型一致,本实验中均采用三态门。

接下来,实验介绍了半导体静态存储器的存取方法。静态存储器(SRAM)以其高速度和非易失性特点被广泛应用。实验电路采用了单总线结构,地址和数据都通过三态传输门共享同一组数据开关。通过精确的操作时序控制,可以区分总线上传输的是地址还是数据。计数器,如74LS161和74LS244的组合,不仅能够接收信息,还能将数据发送到总线上。地址寄存器和输出缓冲器则只负责接收总线信息。存储器部分,实验使用了HM6116这种2K×8位的静态存储器,它包含地址线、数据线、读写控制线以及片选信号。地址寄存器由74LS161组成,而74ls670用于构建寄存器堆。74ls244驱动总线数据灯,74ls273则为存储器送地址并驱动地址灯。

实验电路图显示了34个插孔和17根连接导线,这表明实验电路设计的复杂性。同步四位计数器74LS161通过字长扩展可以实现更高级别的地址计算,其数据输入端D、C、B、A和输出端QD、QC、QB、QA,以及使能端PT和操作模式控制端LD,为实验提供了丰富的操作可能性。

通过这个实验,学生不仅可以了解总线传输的基本原理和实现,还可以实际操作半导体静态存储器,加深对存储器读写过程的理解。这种实践经验对于学习计算机组成原理至关重要,有助于提升学生的理论知识与实践技能。

2024-08-31 上传

151 浏览量

2024-08-31 上传

2024-08-31 上传

2024-12-21 上传

2024-08-31 上传

出云coding

- 粉丝: 68

最新资源

- 火星任务数据分析与Web抓取挑战

- Shiro框架快速入门教程与实例演示

- Calm Wallpaper HD新标签页扩展:个性化壁纸体验

- Redic:Ruby轻量级Redis客户端入门指南

- C语言实战项目:电话号码识别源码解析

- 打造虚拟现实:3D展厅展览模型设计与应用

- UCEMA 计算机基础教程介绍

- 掌握kmeans聚类:Python与Matlab代码模板解析

- React应用测试指南:酶和moxios实践教程

- 深入研究 KotlinSpringBoot REST API开发

- C语言实战项目:结合OpenCV与MFC的Hook技术源码分享

- STM32F103综合实验程序:TFTLCD与温湿度传感器控制

- 《制度汇总调查表》:一致性与社会性的管理资源

- mdf文件修复工具:有效恢复sqlserver数据

- 微信小程序开发: Persona性格测试应用

- 木桥3D结构模型:设计3D桥模型的应用