Lattice FPGA DDR3控制器用户指南

需积分: 10 44 浏览量

更新于2024-07-17

收藏 4.74MB PDF 举报

"本文档是Lattice Semiconductor公司关于Double Data Rate (DDR3) SDRAM Controller IP Core的用户指南,详细介绍了如何在Lattice FPGA中实现DDR3内存的读写控制。作者通过实践验证,该方法已在板卡上成功运行。"

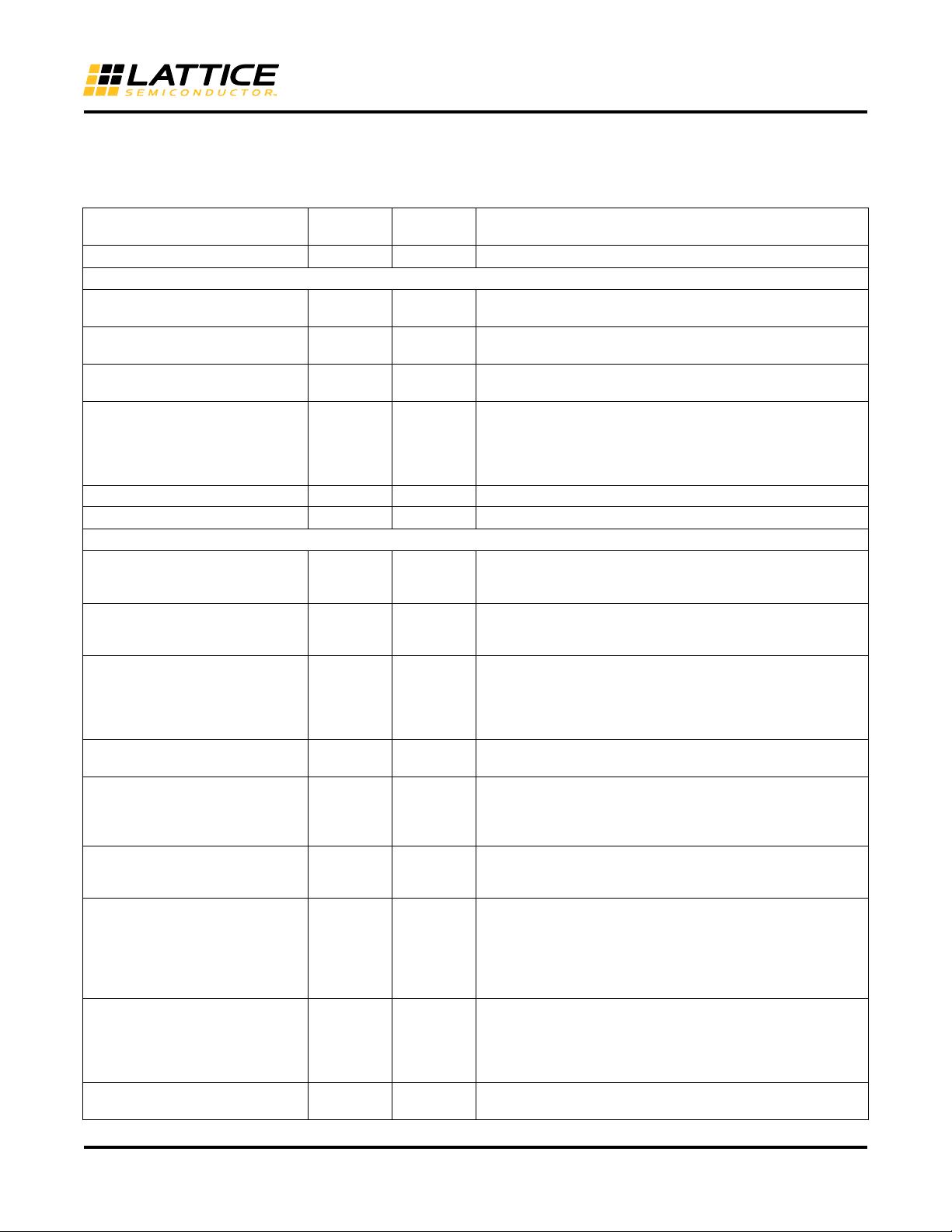

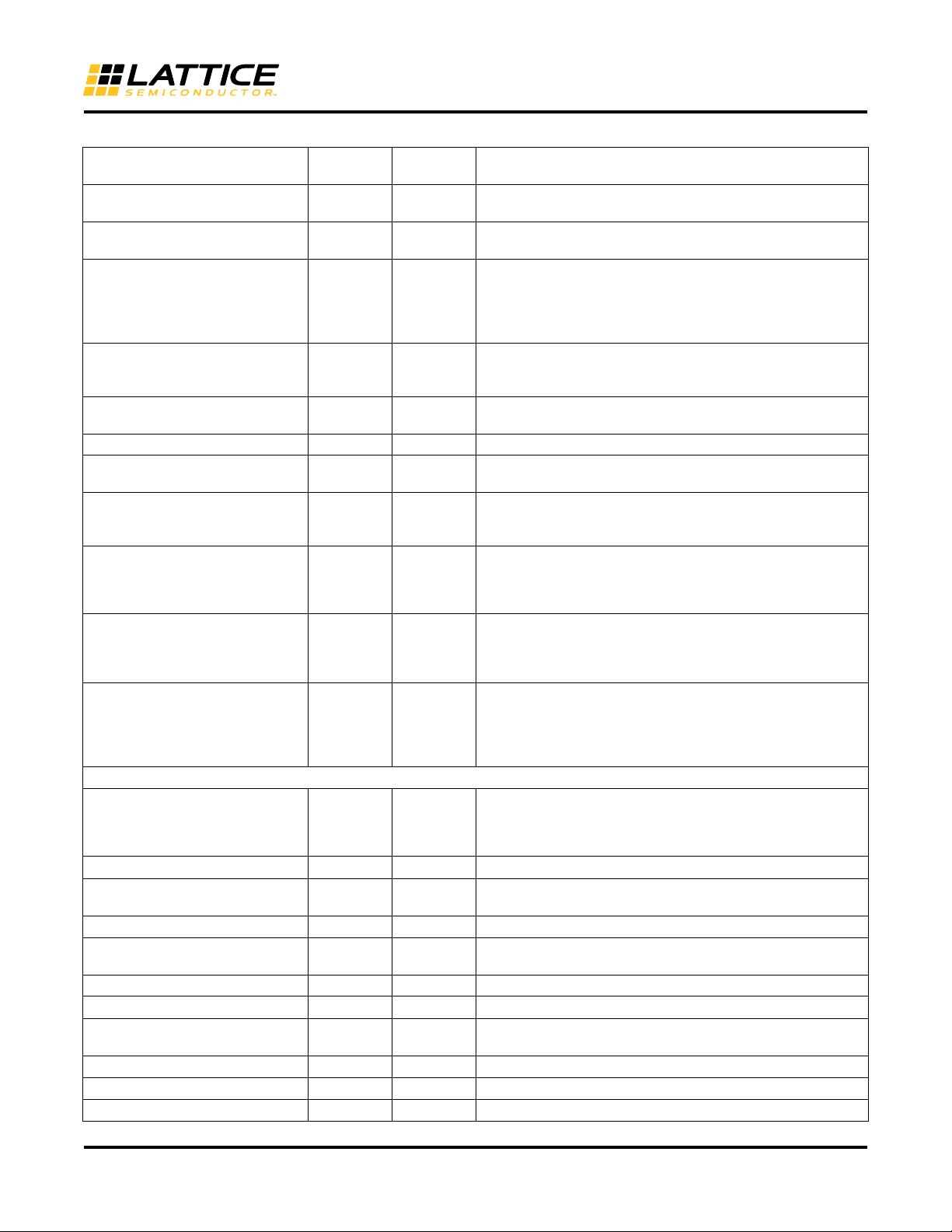

DDR3 SDRAM Controller IP Core是Lattice FPGA设计中用于高效管理DDR3内存模块的关键组件。这个IP核提供了一套完整的解决方案,涵盖了DDR3内存控制器的所有功能,包括命令解码、命令应用、片上终结(On-Die Termination, ODT)、初始化、写入校准、读取训练以及模式寄存器编程等。

1. **快速事实(Quick Facts)**:这部分可能包含有关DDR3 SDRAM Controller IP Core的一些关键特性或性能指标,但具体内容未在摘要中给出。

2. **功能描述(Functional Description)**:

- **概述(Overview)**:概述了IP核在FPGA中的作用,如何与DDR3内存颗粒进行通信,以及其在系统中的位置。

- **DDR3 MC Module**(Memory Controller):这是IP核的核心部分,负责管理和协调所有与DDR3内存的交互。

- **命令解码逻辑(Command Decode Logic)**:这部分解析来自FPGA的内存访问请求,并转换成DDR3内存可以理解的命令。

- **命令应用逻辑(Command Application Logic)**:将解码后的命令正确地应用到DDR3内存总线上。

- **片上终结(On-Die Termination, ODT)**:是DDR3内存的一种特性,用于减少信号反射,提高信号质量。

- **DDR3 PHY Module**:物理层模块,处理与DDR3内存颗粒的物理接口,包括数据路径逻辑和信号描述。

- **初始化模块(Initialization Module)**:负责设置DDR3内存的初始状态,如时钟调整、模式寄存器配置等。

- **写入校准(Write Leveling)**:确保数据在写入内存时与内存的时钟同步。

- **读取训练(Read Training)**:仅适用于ECP5设备,用于优化读取数据的准确性。

- **选择READ_PULSE_TAP值(Selecting READ_PULSE_TAP Value)**:仅适用于Lattice ECP3设备,是读取训练的一部分,调整读取脉冲以提高读取性能。

- **数据路径逻辑(Data Path Logic)**:处理数据的传输,包括读取和写入操作。

3. **用户界面(Using the Local User Interface)**:用户可以通过本地接口设置和控制DDR3控制器,如初始化控制、命令和地址映射等。

4. **初始化控制(Initialization Control)**:在开始使用DDR3内存之前,需要进行必要的初始化设置,如时钟设置、模式寄存器编程等。

5. **命令和地址(Command and Address)**:IP核支持用户定义的内存访问命令,如标准的WRITE、WRITEA、READ、READA命令。

6. **用户命令(User Commands)**:

- **WRITE**:执行向DDR3内存写入数据的操作。

- **WRITEA**:可能是带附加信息的写命令。

- **READ**:从DDR3内存读取数据。

- **READA**:可能是指带有附加信息的读命令。

7. **刷新支持(REFRESH Support)**:DDR3内存需要定期刷新以保持数据的完整性,IP核提供了相应的支持。

8. **本地到内存地址映射(Local-to-Memory Address Mapping)**:解释如何将FPGA内部的地址映射到DDR3内存的地址空间。

9. **模式寄存器编程(Mode Register Programming)**:DDR3内存有多个模式寄存器,用来设置内存的各种工作参数,IP核提供了编程这些寄存器的功能。

这份用户指南为开发者提供了详尽的指导,帮助他们在Lattice FPGA平台上有效地集成和使用DDR3 SDRAM Controller IP Core,实现高效、可靠的内存访问。

2024-11-19 上传

2024-11-19 上传

2024-11-19 上传

2024-11-19 上传

DXD_xiaoding

- 粉丝: 0

- 资源: 2

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析