SystemVerilog断言(SVA)详解与应用

"SystemVerilog+Assertions应用指南"

SystemVerilog是一种强大的硬件描述语言,它引入了SystemVerilog Assertions (SVA) 功能,用于增强设计验证的效率和准确性。SVA是专门为了验证目的设计的,它弥补了传统Verilog在断言实现上的不足。

断言(Assertion)在设计中扮演着关键角色,它定义了设计应遵循的属性。如果在模拟过程中,断言所描述的属性未按预期执行,即表示设计出现了问题,断言会失败。断言可以是设计功能的直接反映,它们在功能仿真中持续监控,也可用于形式验证。传统的Verilog断言通常通过过程语言实现,如示例中的`ifdefma结构,但这种方法存在限制,例如对时序控制的不足,代码冗长且难以维护,以及并行事件处理的复杂性。

SystemVerilog断言(SVA)解决了这些问题。SVA是一种非过程性的、描述性的语言,它擅长处理时序相关的问题,提供对时间的精细控制。SVA的代码简洁且易于维护,特别适合大规模设计的断言。此外,SVA内建了功能,可以方便地测试特定设计场景,并自动收集功能覆盖数据,这是传统Verilog不具备的。

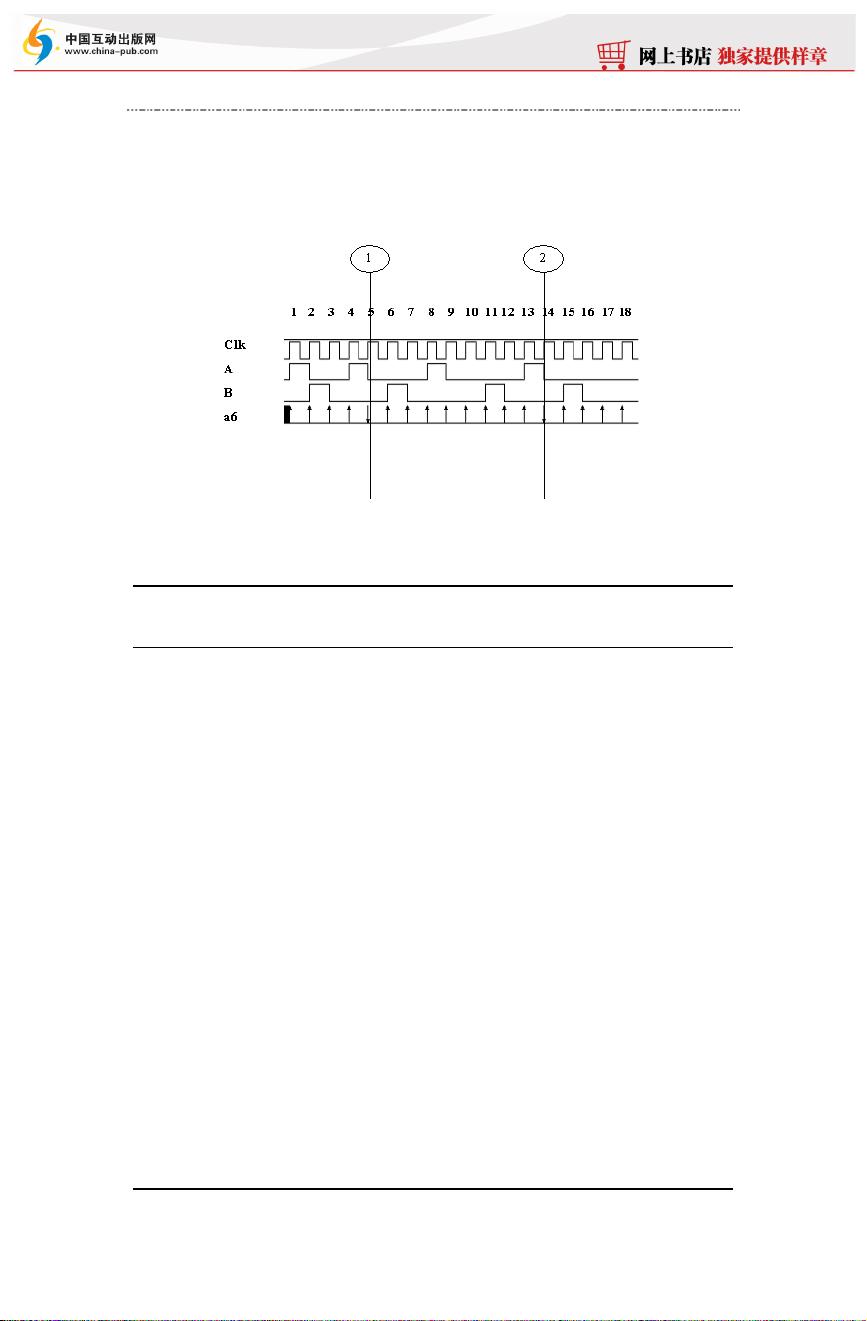

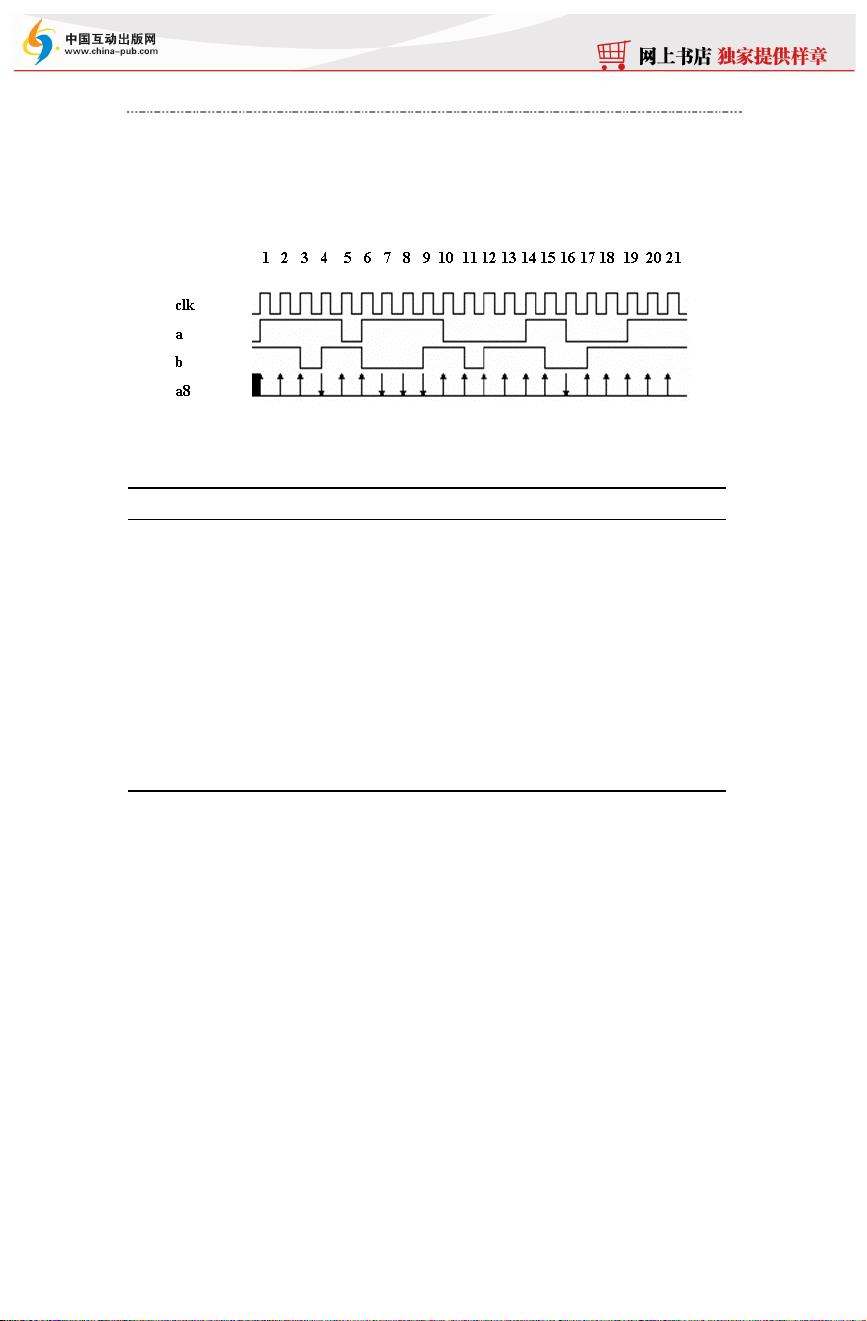

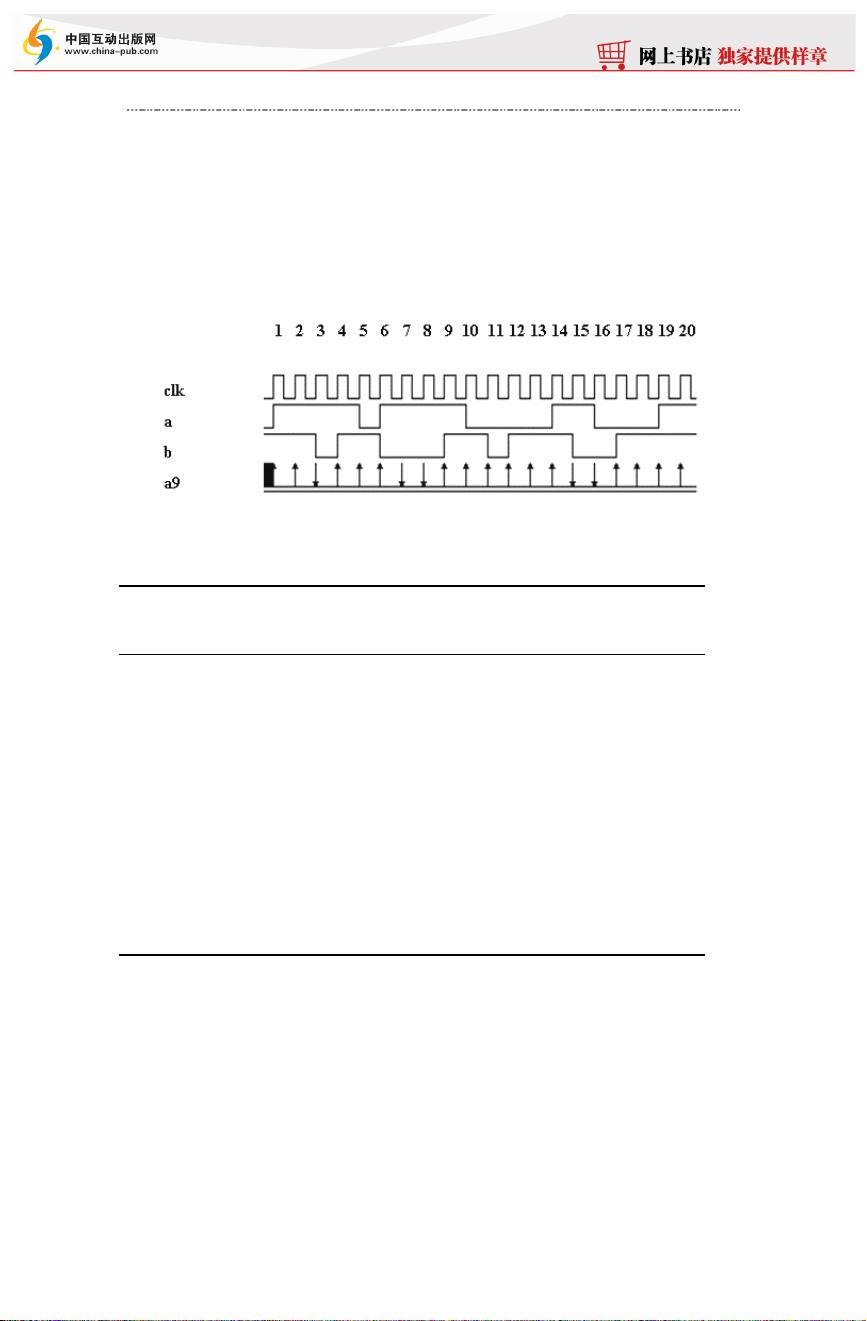

例子1.1比较了Verilog和SVA实现的检验器。在Verilog实现中,检验器可能只能简单地检查即时事件,如信号a为高时,信号b是否在随后的周期变为低。然而,SVA能够更优雅地表达这种时序关系,同时提供更丰富的条件和复杂性,如脉冲宽度检查、延迟检查等。

SVA的其他优势还包括其强大的表达能力,例如使用序列操作符(序列匹配如‘seq’和‘followed_by’),条件表达式,以及定时控制(如‘#’和‘after’)。这些特性使得设计者可以准确地描述复杂的时序行为,而无需编写复杂的Verilog过程代码。

SystemVerilog Assertions 提供了一种高效、灵活和可扩展的方式来验证硬件设计,确保其满足预定的行为规范。通过利用SVA,设计者可以提高验证覆盖率,减少错误,并简化维护工作,从而提高整个设计流程的质量和效率。

367 浏览量

211 浏览量

132 浏览量

576 浏览量

785 浏览量

571 浏览量

137 浏览量

279 浏览量

674 浏览量

天山懒人

- 粉丝: 99

- 资源: 17

最新资源

- 负载均衡性能深度分析

- Zend+Framework+入门指南v0.12.pdf

- latex:传说中的lnotes

- ArcGIS二次开发编程实例

- 主板知识 电脑主板 知识

- spring2.5.4+hibernate3.2.6+struts2+jbpm3.2.2收藏

- 精通Spring--JAVA轻量级架构开发实践

- 《Struts+Web设计与开发大全》.pdf

- 计算机三级等级考试网络技术上机

- 网络与信息安全――具有安全权限的微内核操作系统模型

- TOPSEC 认证客户端安装指南

- Effective STL-revised.pdf

- UsingFlashpaper_EN.pdf

- 高质量C++编程指南

- TOPSEC防火墙安装指南

- jbpm用户手册帮您实现第一个helloworld