边沿触发器与触发器功能变换讲解

版权申诉

114 浏览量

更新于2024-07-17

收藏 596KB PPT 举报

"该资源是一份关于数字逻辑电路的第13讲教学材料,主题是边沿触发器及其功能变换,主要涵盖了边沿触发器的概念、类型和应用,特别是D、JK、T、T'触发器的逻辑功能。"

在数字逻辑电路中,边沿触发器是一种关键的时序电路元件,它的主要特点是能够有效地克服同步触发方式中的空翻问题,提高电路的稳定性和抗干扰性。空翻是指在时钟脉冲作用下,电路状态在预期改变之前短暂不稳定的现象。边沿触发器通过只在时钟脉冲的上升沿或下降沿对输入信号作出响应,确保了电路状态的准确转换,从而消除了空翻。

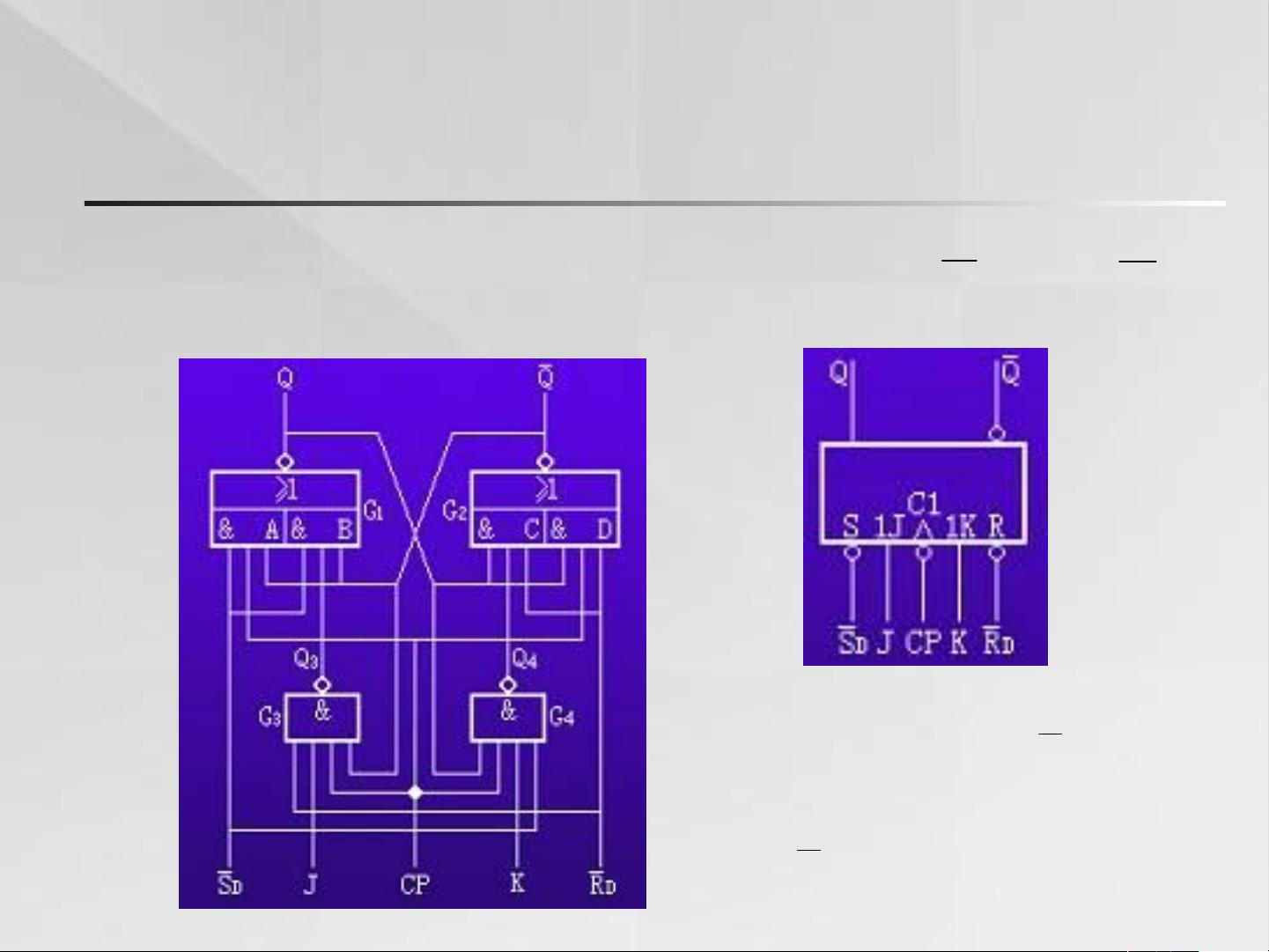

边沿触发器的种类包括维持阻塞D触发器、边沿JK触发器以及CMOS边沿触发器等。D触发器以其简单的特性方程(Qn+1=D)而著名,其特征是没有前一状态Qn的参与,直接由当前输入D决定下一状态。JK触发器则提供了更丰富的逻辑功能,可以通过J和K输入实现置位、复位、保持以及翻转四种状态转换。T和T'触发器主要用于频率分频,T触发器使得Q状态翻转,T'触发器则使Q状态反转。

TTL边沿JK触发器是其中的一种具体实现,电路结构中,"^"标记指示边沿触发输入,而小圆圈的有无则决定了是上升沿还是下降沿有效。其逻辑功能通常由特性方程描述,如JCPK→QQ,表示在CP下降沿到来后的新状态Qn+1由J、K的值决定。

在学习和应用这些触发器时,重要的是理解和掌握它们的逻辑功能、触发方式以及特性方程。特性表、驱动表和状态转换图是分析和设计时序电路的关键工具。虽然具体电路的工作原理在此不作深入分析,但了解这些基础概念对于理解和使用集成触发器至关重要,因为实际工程中,触发器的应用通常是基于其提供的逻辑功能和性能参数。

2021-09-16 上传

2023-04-21 上传

2021-12-21 上传

2022-06-02 上传

2022-06-02 上传

2021-09-19 上传

2021-09-18 上传

Dambulla

- 粉丝: 7

- 资源: 3万+

最新资源

- 新代数控API接口实现CNC数据采集技术解析

- Java版Window任务管理器的设计与实现

- 响应式网页模板及前端源码合集:HTML、CSS、JS与H5

- 可爱贪吃蛇动画特效的Canvas实现教程

- 微信小程序婚礼邀请函教程

- SOCR UCLA WebGis修改:整合世界银行数据

- BUPT计网课程设计:实现具有中继转发功能的DNS服务器

- C# Winform记事本工具开发教程与功能介绍

- 移动端自适应H5网页模板与前端源码包

- Logadm日志管理工具:创建与删除日志条目的详细指南

- 双日记微信小程序开源项目-百度地图集成

- ThreeJS天空盒素材集锦 35+ 优质效果

- 百度地图Java源码深度解析:GoogleDapper中文翻译与应用

- Linux系统调查工具:BashScripts脚本集合

- Kubernetes v1.20 完整二进制安装指南与脚本

- 百度地图开发java源码-KSYMediaPlayerKit_Android库更新与使用说明