基于VHDL的4-MPSK调制解调器设计与实现

需积分: 9 48 浏览量

更新于2024-12-19

收藏 123KB DOC 举报

本资源是一份基于VHDL(Very High Speed Integrated Circuit Hardware Description Language)的MPSK(Multiple Phase Shift Keying,多相移键控)调制与解调程序。MPSK是一种数字调制技术,它通过改变载波信号的相位来表示数据比特,其中在这个案例中,M取值为4,意味着有四个不同的相位状态用于编码。

该程序名为"PL_MPSK",其主要功能是将输入的基带信号(x)通过VHDL硬件描述转化为MPSK调制信号(y)。程序结构包括一个实体(entity)PL_MPSK,定义了输入时钟(clk)、开始信号(start)、基带信号输入(x)和调制信号输出(y)端口。实体内部还定义了几个信号变量,如计数器q、中间寄存器xx、并行码寄存器yy以及载波信号f。

在行为级(architecture)的实现部分,程序利用了一个进程(process),这个进程根据系统时钟(clk)的变化来控制程序的执行流程。当系统时钟上升沿触发时,根据计数器q的状态,程序执行不同的操作,如设置载波信号的相位,更新中间寄存器和并行码寄存器,以及将最终的载波相位映射到输出的调制信号上。

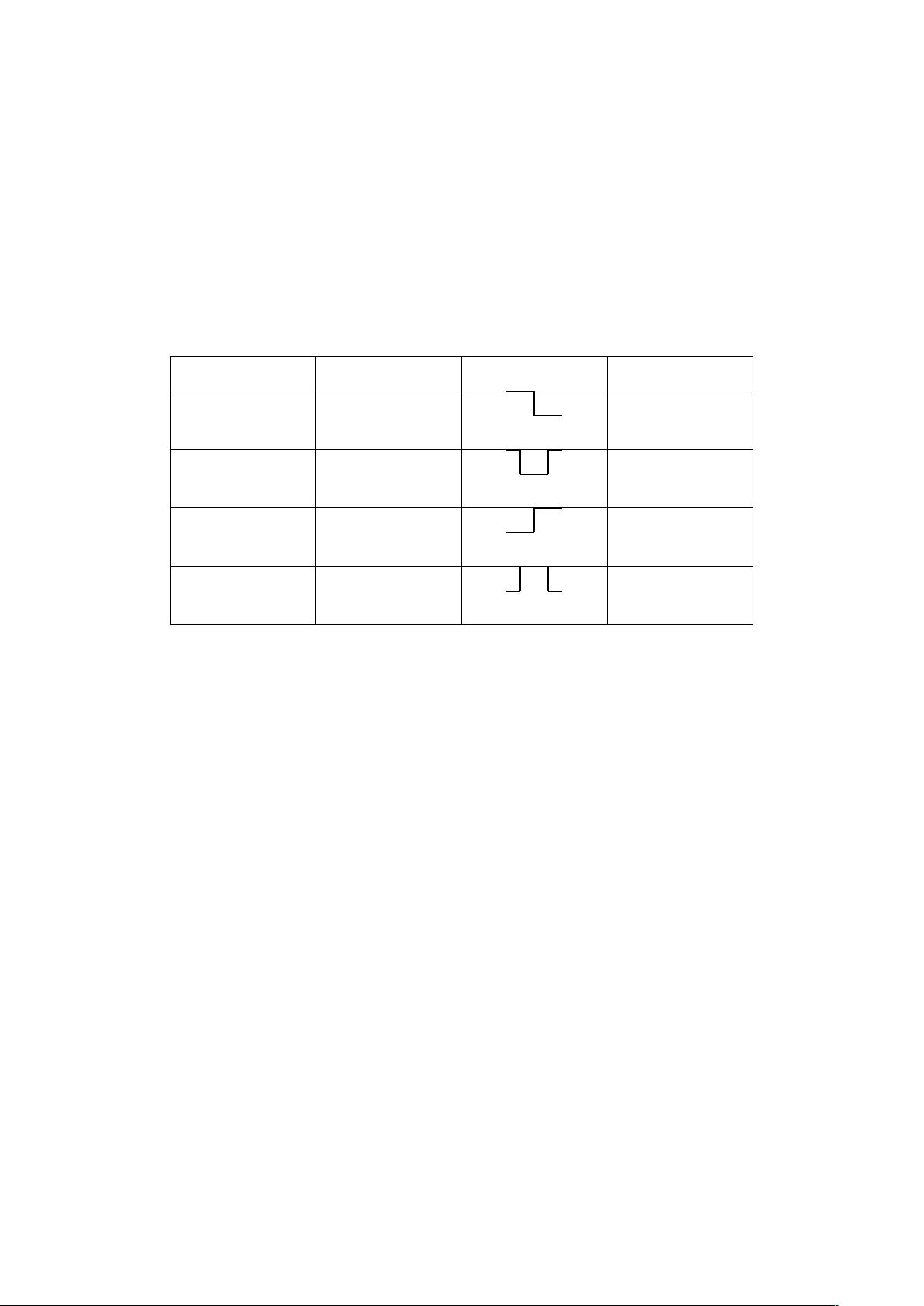

具体来说,计数器q的值决定了载波的四个不同相位,对应于基带信号的“00”、“01”、“10”和“11”这四种状态。每一步的相位变化都是通过调整载波信号f的二进制表示来实现的,例如,当q等于0或4时,f的最低两位分别置为1和0,表示0相位;而当q等于1或5时,它们的值会反转,表示90度相位变化。

值得注意的是,表8.14.2给出了具体的调制信号说明,列出了每个信号组合对应的载波相位、载波波形和符号。这个表格对于理解和实现MPSK调制至关重要,因为它明确了信号之间的对应关系。

整个程序设计体现了VHDL语言的基本结构,包括数据类型定义、信号声明、过程流程控制等,是学习和实践VHDL在数字通信系统中的MPSK调制应用的良好实例。通过此程序,用户可以深入理解MPSK调制原理,并将其应用于实际的硬件设计中。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-06-04 上传

2023-06-06 上传

2024-06-19 上传

2022-09-14 上传

2021-10-04 上传

2022-09-24 上传

perfectzhi

- 粉丝: 1

- 资源: 23

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成