FPGA实现的UART接口模块设计详解

PDF格式 | 394KB |

更新于2024-09-01

| 77 浏览量 | 举报

本文主要探讨了基于FPGA的UART接口模块设计,一种在现代电子系统中广泛应用的串行通信协议。UART,即通用异步收发器,由于其简单、灵活且广泛被微处理器支持的特点,即使在USB等高性能协议普及的今天,仍占据着重要地位,特别是在资源有限或成本敏感的应用中。

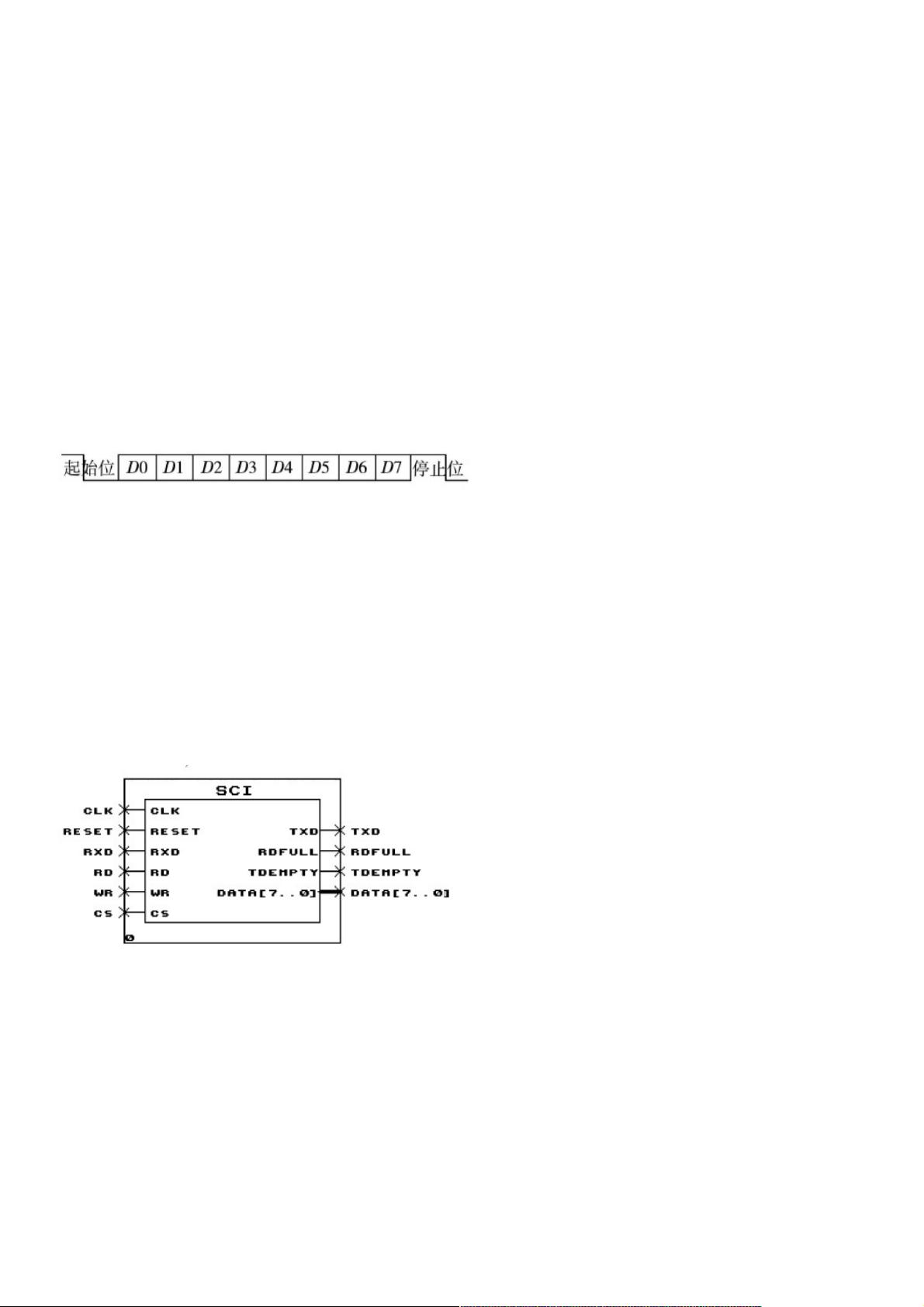

首先,文章对UART进行了简要介绍。UART利用两条线(RXD接收和TXD发送)进行全双工通信,数据帧由起始、数据、校验和停止位组成。发送者通过起始位标识数据传输的开始,数据位通常为8位(也可根据需要定制),校验位用于检测错误,而停止位则表示帧的结束。这种协议具有清晰的电气定义和同步特性,使得它易于实现和理解。

其次,文章重点讲述了如何在FPGA中实现UART功能。FPGA的优势在于可以灵活配置,针对实际需求定制功能,无需使用复杂的专用UART集成电路,如8250或8251,这可以避免资源浪费和提高成本。设计者通过VHDL硬件描述语言编写代码,构建波特率发生器模块、发送模块和接收模块这三个核心部分,以实现UART的数据收发功能。这些模块构成了编译后的图元SCI,其中包括了数据输入/输出(DATA)、片选(CS)、读写控制(RD/WR)以及状态指示(RDFULL/TDEMPTY)等接口,确保了与外部数字系统之间的高效通信。

总结来说,本文提供了基于FPGA的UART接口模块设计的关键技术细节,包括UART协议的工作原理、FPGA如何利用其灵活性实现UART功能,以及接口设计的组成部分。这种设计方法不仅简化了系统电路,降低了成本,还提高了系统的可靠性和灵活性,对于需要在FPGA上集成串行通信功能的工程项目具有重要的参考价值。

相关推荐

weixin_38636577

- 粉丝: 4

- 资源: 935