• The PADRESETn (system reset): this reset is built through several sources:

– PORESETn

– Reset due to the watchdog

The BlueNRG-LP device embeds a watchdog timer, which may be used to recover from software

crashes

– Reset due to CPU Lockup

The Cortex-M0+ generates a lockup to indicate the core is in the lock-up state resulting from an

unrecoverable exception. The lock-up reset is masked if a debugger is connected to the Cortex-M0+

– Software system reset

The system reset request is generated by the debug circuitry of the Cortex®-M0+. The debugger sets

the SYSRESETREQ bit of the application interrupt and reset control register (AIRCR). This system

reset request through the AIRCR can also be done by the embedded software (into the hardfault

handler for instance)

– Reset from the RSTN external pin

The RSTN pin toggles to inform that a reset has occurred

This PADRESETn resets all resources of the BlueNRG-LP, except:

• Debug features

• Flash controller key management

• RTC timer

• Power controller unit

• Part of the RCC registers

The pulse generator guarantees a minimum reset pulse duration of 20 μs for each internal reset source. In case

of reset from the RSTN external pad, the reset pulse is generated when the pad is asserted low.

1.9

Clock management

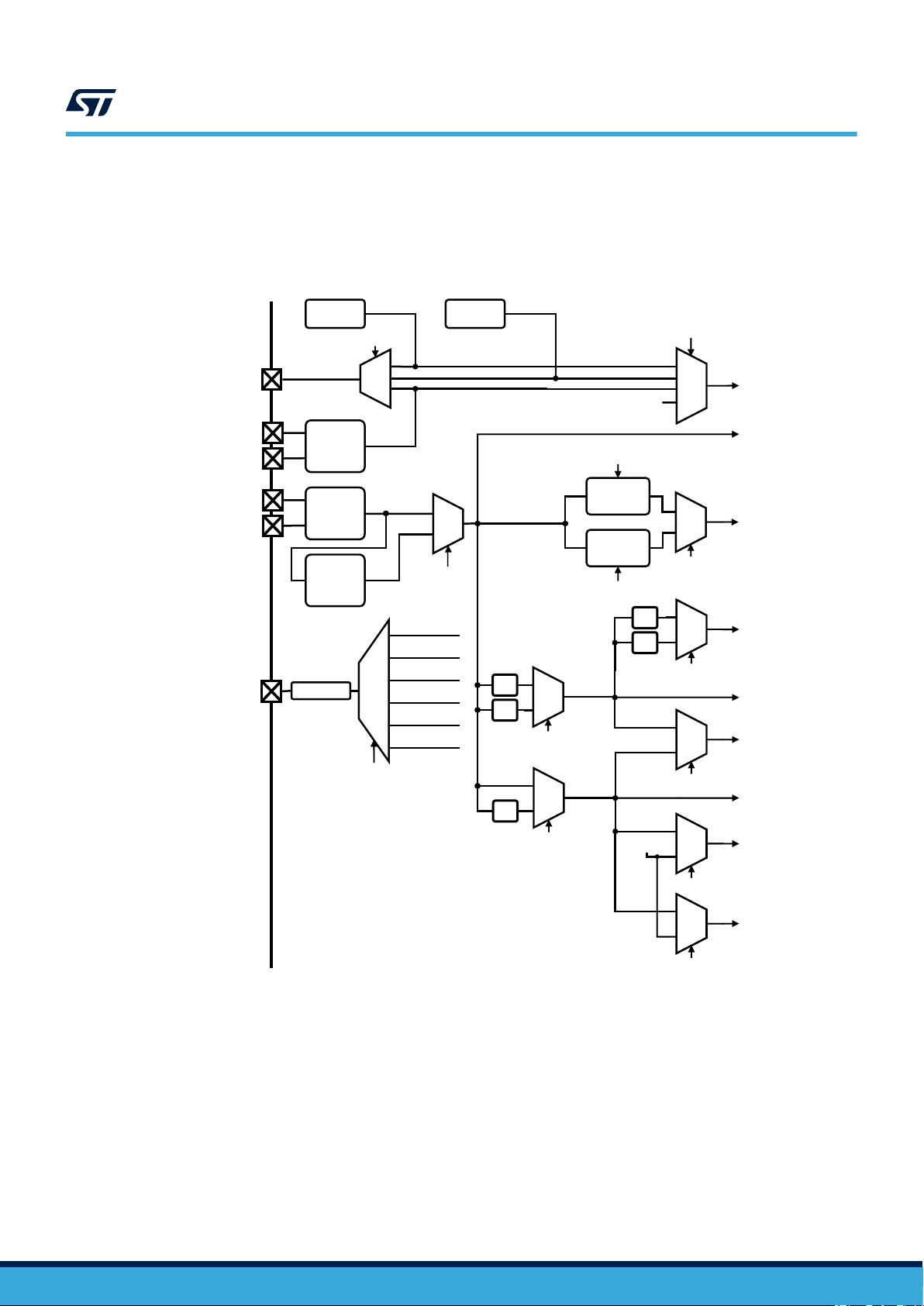

Three different clock sources may be used to drive the system clock of the BlueNRG-LP:

• HSI: high speed internal 64 MHz RC oscillator

• PLL64M: 64 MHz PLL clock

• HSE: high speed 32 MHz external crystal

The BlueNRG-LP has also a low speed clock tree used by some timers in the radio, RTC and IWDG.

Four different clock sources can be used for this low speed clock tree:

• Low speed internal (LSI): low speed and low drift internal RC with a fixed frequency between 24 kHz and 49

kHz depending on the sample

• Low speed external (LSE) from:

– An external crystal 32.768 kHz

– A single-ended 32.738 kHz input signal

• A 32 kHz clock (CLK_16 MHz/512 in Figure 6. Clock tree) obtained by dividing HSI or HSE. In this case, the

slow clock is not available in DEEPSTOP low power mode

• LSI_LPMU: 32 kHz clock used by the low power management unit (LPMU) analog block.

By default, after a system reset, all low speed sources are OFF.

Both the activation and the selection of the slow clock are relevant during the DEEPSTOP mode and at wakeup

as slow clock generates a clock for the timers involved in wake-up event generation.

The HSI and the PLL64M clocks are provided by the same analog block called RC64MPLL. The 64 MHz clock

output by this block can be:

• A non-accurate clock when no external XO provides an input clock to this block (HSI)

• An accurate clock when the external XO provides the 32 MHz and once its internal PLL is locked (PLL64M)

This fast clock source is used to generate all the fast clock of the device through dividers. After reset, the

CLK_SYS is divided by four to provide a 16 MHz to the whole system (CPU, DMA, memories and peripherals).

This fast clock source is also used to generate several internal fast clocks in the system:

• Always 32 MHz requested by a few peripherals like the radio

BlueNRG-LP

Clock management

DS13282 - Rev 2

page 14/72