Xilinx EDK实验:基于PLB的Atlys嵌入式开发入门

需积分: 16 56 浏览量

更新于2024-07-24

收藏 7.21MB PDF 举报

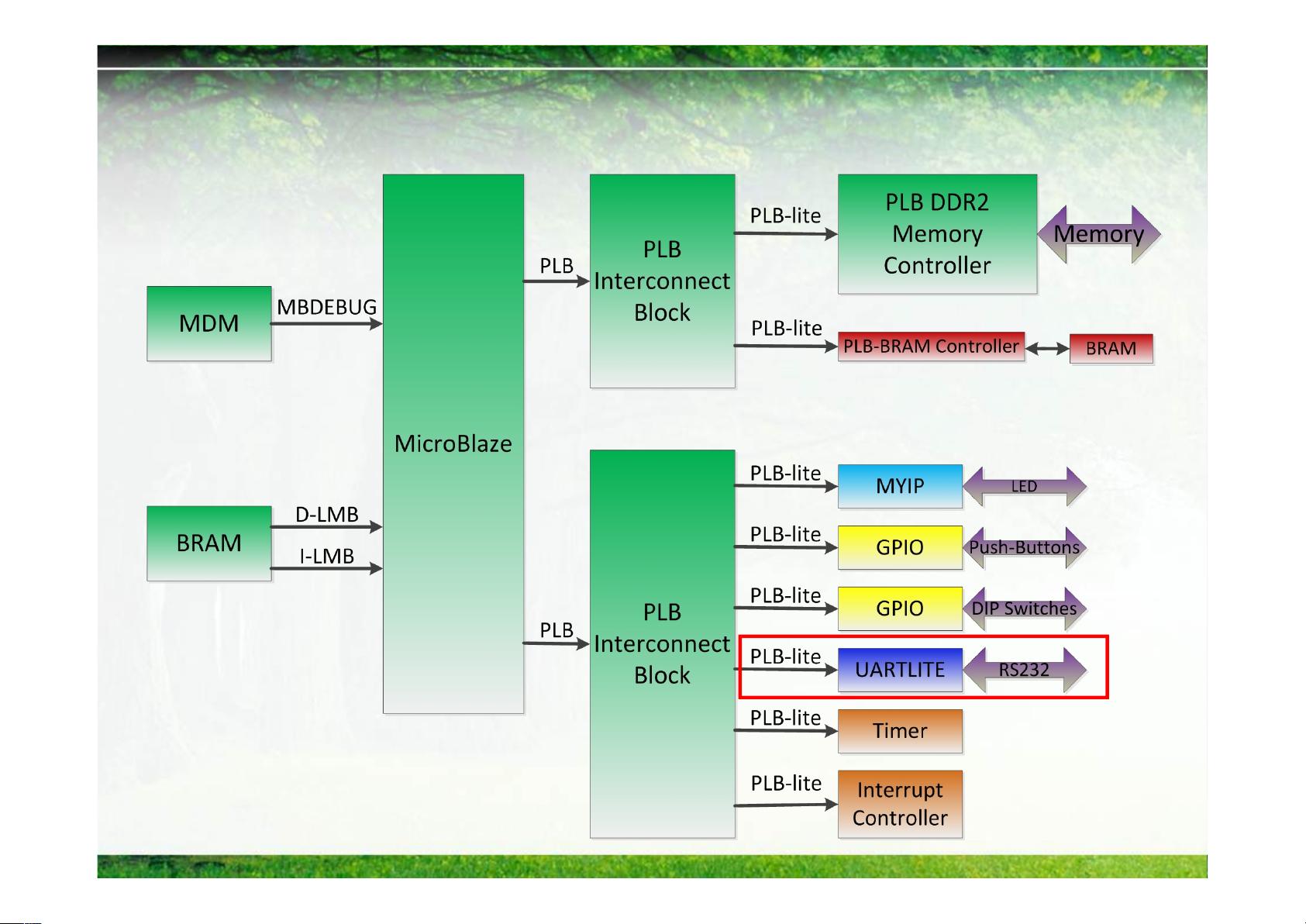

FPGA嵌入式开发实验1是针对初学者的一门课程,主要使用Xilinx的Embedded Development Kit (EDK)和Xilinx Platform Studio (XPS)进行实践。该实验着重于基于PLB总线接口的简单硬件电路设计,通过创建一个包含MicroBlaze处理器系统的设计项目来熟悉工具和流程。

实验目标有两个关键部分:首先,使用BaseSystemBuilder (BSB)向导构建一个XPS工程,这涉及到配置必要的组件,如MicroBlaze 8.20.b版本的处理器,PLB_V46 Interconnect Blocks,用于存储的LMB BRAM控制器,以及BRAM、UART串行通信和外部DDR2_SDRAM内存。其次,学习如何在嵌入式开发套件EDK中利用IP核创建硬件电路,并通过MemoryTestApp进行功能验证。

实验流程分为四个步骤:

1. 使用BSB创建工程:

- 启动XPS并打开BSB。

- 选择工程存放位置并配置互连类型为PLBSystem,确保添加Atlys_BSB_Support_v_3_6的支持库。

- 在Board对话框中选择Digilent作为厂商,Atlys作为板子名称,确认板子修订版为C。

- 进入System对话框进行系统配置。

2. 分析工程:

- 在创建工程后,需要理解工程架构和各个组件之间的连接关系,这有助于后续的设计和调试。

3. 在SDK中创建MemoryTestApp:

- 使用Xilinx SDK创建一个简单的应用程序,如MemoryTestApp,用于测试硬件电路的功能,如内存访问和数据传输。

4. 硬件上测试:

- 将设计下载到Atlys板上,通过实际运行MemoryTestApp来验证硬件电路的正确工作,包括处理器与外设交互、内存访问是否正常等。

整个实验过程中,学习者将亲自动手实践,从软件配置到硬件应用,逐步掌握FPGA嵌入式开发的基础技能,这对于理解和运用FPGA技术进行系统级设计非常有价值。

489 浏览量

点击了解资源详情

2016-11-21 上传

2009-12-11 上传

152 浏览量

2010-04-09 上传

panlei666

- 粉丝: 0

最新资源

- 探索Eclipse下的SWT:跨平台GUI开发的解决方案

- 探索程序问题:echo、@、Goto等工具在垃圾信息中的应用与注意事项

- JasperReports终极指南:报表设计与开发

- 基于微分几何理论的混沌同步研究

- 微分几何驱动的飞机登机策略优化

- C# 将 DataTable 数据导出为 DBF 文件

- Eclipse教程:详解如何使用WTP开发Web服务

- GCC中文手册:Linux开发必备

- 揭秘嵌入式操作系统:必备知识点与应用优势

- PHP初学者指南:简易分页实现

- ExtJS2.0入门与实战教程:提升Web应用体验

- EasyJWeb:企业级Java Web开发框架解析

- 华为网络实验手册:打造计算机网络实战能力

- 理解IoC与Dependency Injection:控制反转与组件装配

- 主题重要性与专题搜索策略:魏本洁的研究

- Adobe Flex工作原理与首个应用开发简介