Quartus II下7人表决电路设计与8位全加器实验详解

下载需积分: 9 | DOC格式 | 448KB |

更新于2024-09-16

| 92 浏览量 | 举报

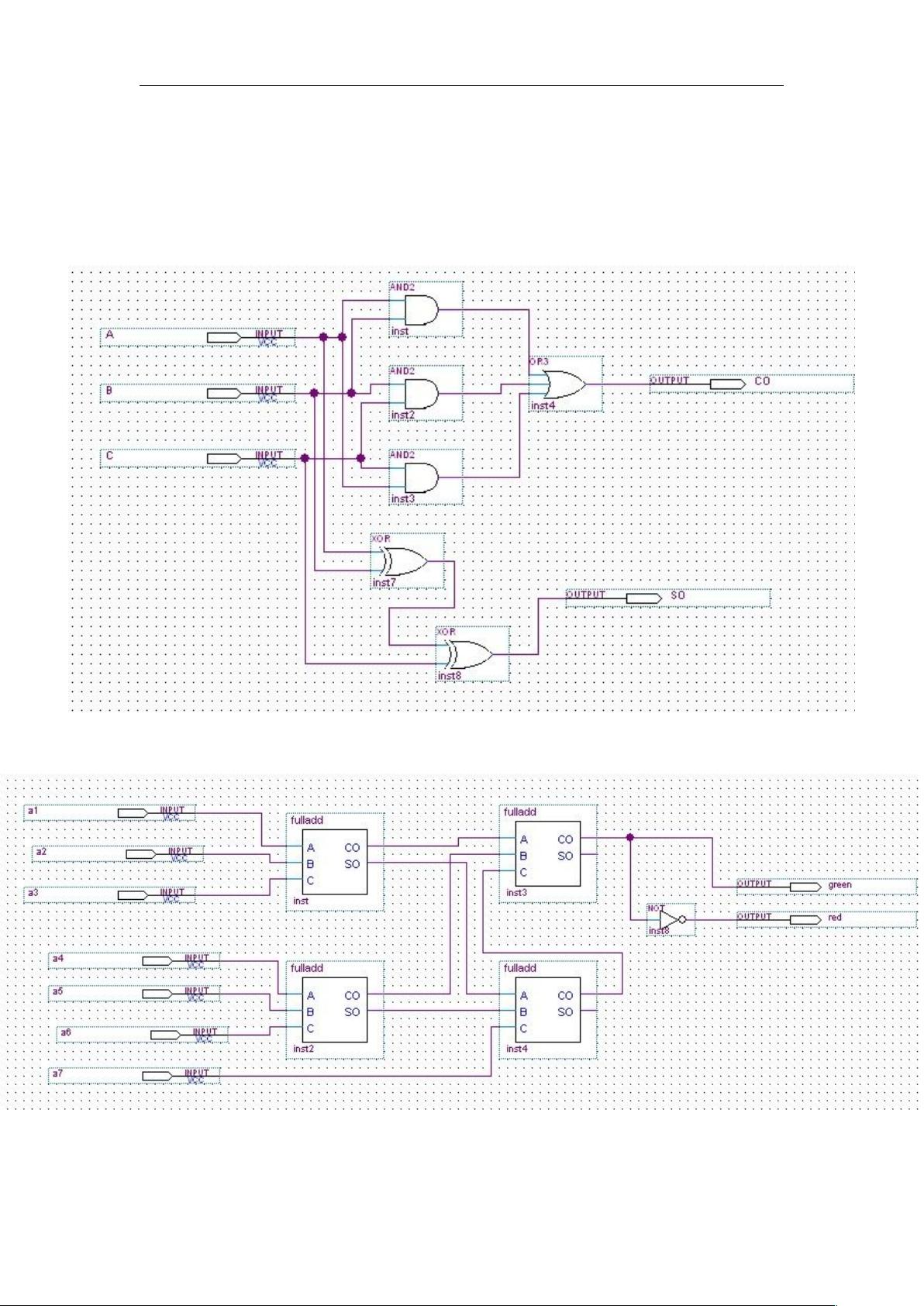

在本次EDA作业5-6中,主要任务涉及Quartus II应用向导下的电路设计,具体是一个7人表决电路的构建。该电路的目标是根据参与者的投票结果进行决策,如果超过半数人同意,绿色指示灯亮起,表示表决通过;反之,红色指示灯亮起,表示不通过。设计的关键是利用全加器作为基础组件。

全加器在这里扮演了核心角色,全加器是一种逻辑电路,能够实现两个二进制数相加的功能,同时输出进位信号。在题目中,给出了两种全加器的描述:半加器和一位全加器。半加器负责处理单个二进制位的加法,而一位全加器则可以处理两个二进制位的加法,并同时输出进位和和。为了实现8位并行全加器,需要将一位全加器作为子模块,通过级联和复制的方式构建,这涉及到组合逻辑设计中的案例化和模块化思想。

实验与设计部分要求学生利用1位二进制全加器作为基本元件,编写一个8位并行二进制全加器的顶层文件。这不仅需要理解全加器的结构和工作原理,还需要熟练掌握如何在VHDL或Verilog等硬件描述语言中使用CASE语句来表示输入的不同情况,以及如何组织和连接这些子模块以实现整个电路的功能。

在这个过程中,学生将学习到以下知识点:

1. 全加器和半加器的理解:了解它们的工作原理、输入输出信号以及在加法运算中的作用。

2. VHDL或Verilog设计:如何使用这些高级硬件描述语言来定义和实现电路模块,包括端口声明、实体和架构的定义。

3. 模块化和组合逻辑设计:学会如何通过模块化的方法设计复杂电路,如将一个全加器扩展为8位并行全加器。

4. 逻辑门级仿真和验证:使用Quartus II工具,学生需要验证电路的行为是否符合预期,确保正确实现了表决电路的功能。

本项作业要求学生运用理论知识,实际操作Quartus II工具,并通过编程实现电路设计,提升了他们对数字逻辑设计和分析的能力,同时也锻炼了他们的问题解决和逻辑思维技巧。

相关推荐