Vivado2015.4完整工程建立教程:从创建到仿真

需积分: 17 74 浏览量

更新于2024-07-17

收藏 2.22MB DOCX 举报

"Vivado2015.4使用教程,介绍如何建立一个完整的工程,包括创建项目、添加源文件、编写Verilog代码、进行仿真、添加约束文件以及进行综合操作。"

在Xilinx FPGA开发中,Vivado 2015.4是一款强大的集成设计环境,它支持从设计输入、逻辑综合、仿真到硬件编程的全流程。本教程以建立一个简单的流水灯工程为例,详细讲解Vivado的使用步骤。

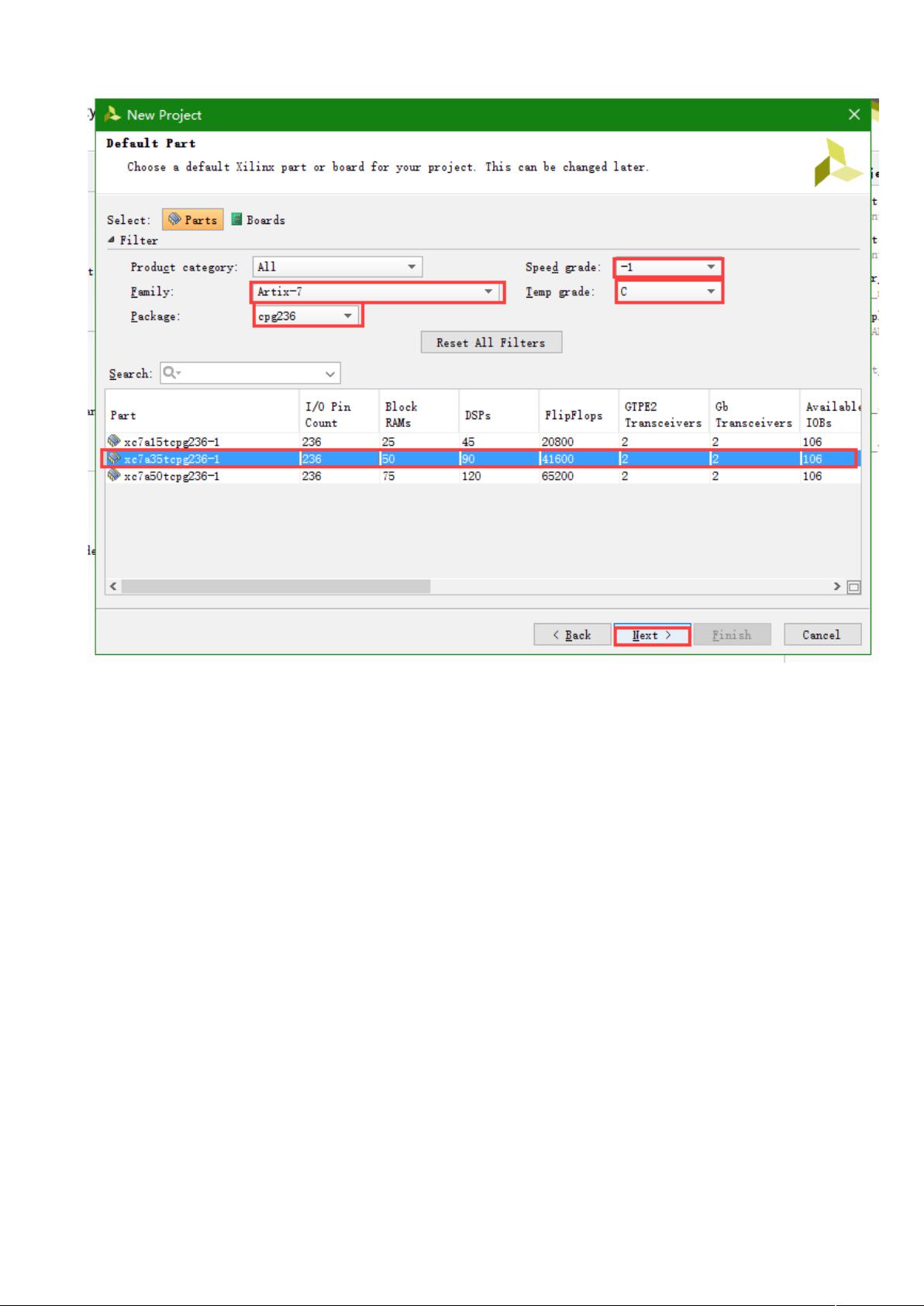

首先,启动Vivado,创建新项目。双击Vivado图标打开软件,进入主菜单界面,选择“Create New Project”。在向导中,依次设定工程名称和保存位置,接着选择项目类型为“RTL Project”,并指定目标硬件平台,例如A-7系列的Basys3开发板。

接下来,添加源文件。在左侧的导航栏中点击“Add Source”,选择“New Source”来创建新的Verilog HDL文件。输入文件名(例如:led_water),选择Verilog作为文件类型,然后点击“Finish”。打开新创建的文件,编写Verilog代码实现流水灯的设计。

代码完成后,可以进行编译和查看RTL图。点击文件,选择“Compile”来编译代码,编译无误后,可以通过查看“Design”视图中的RTL图来理解逻辑结构。双击RTL图的某个模块可以放大查看。

为了验证设计,需要添加测试文件。再次点击“Add Source”,选择“New Testbench Source”,创建一个新的Verilog测试文件(例如:tb_led_water)。编写测试代码,例如包含一个26位的计数器,并设置合适的时钟周期。在进行仿真前,可以调整参数以加快仿真速度。

进行仿真,点击“Run Simulation”,然后选择“Run Behavioral Simulation”。在测试文件中,观察流水灯数值的变化以确认设计是否正确。

接下来,需要为硬件配置约束。点击“Add Source”,选择“New Constraints File”来创建XDC约束文件。在约束文件中,定义输入输出引脚的分配,确保硬件连接正确。完成后,点击“Synthesize - XST”进行综合操作,这一步将把Verilog代码转换成适合FPGA的门级网表。

综合完成后,可以准备下载到硬件板上。点击“Open Target”,选择“Auto Connect”来连接硬件设备。确保测试时修改的代码已恢复原样,然后进行硬件编程,至此,一个完整的Vivado工程建立和运行流程就完成了。

通过这个教程,初学者可以了解到Vivado的基本操作,包括项目的创建、源代码编写、仿真验证和硬件部署,为后续的FPGA开发打下坚实的基础。

1193 浏览量

2025-01-08 上传

158 浏览量

355 浏览量

313 浏览量

157 浏览量

214 浏览量

188 浏览量

木由名

- 粉丝: 3

最新资源

- 掌握Ember.js用户活跃度跟踪,实现高效交互检测

- 如何在Android中实现Windows风格的TreeView效果

- Android开发:实现自定义标题栏的统一管理

- DataGridView源码实现条件过滤功能

- Angular项目中Cookie同意组件的实现与应用

- React实现仿Twitter点赞动画效果示例

- Exceptionless.UI:Web前端托管与开发支持

- 掌握Ruby 1.9编程技术:全面英文指南

- 提升效率:在32位系统中使用RamDiskPlus创建内存虚拟盘

- 前端AI写作工具:使用AI生成内容的深度体验

- 综合技术源码包:ASP学生信息管理系统

- Node.js基础爬虫教程:入门级代码实践

- Ruby-Vagrant:简化虚拟化开发环境的自动化工具

- 宏利用与工厂模式实践:驱动服务封装技巧

- 韩顺平Linux学习资料包:常用软件及数据库配置

- Anime-Sketch-Colorizer:实现动漫草图自动化上色