使用NIOS II FPGA嵌入式处理器实现LCD控制方法

103 浏览量

更新于2024-08-31

收藏 133KB PDF 举报

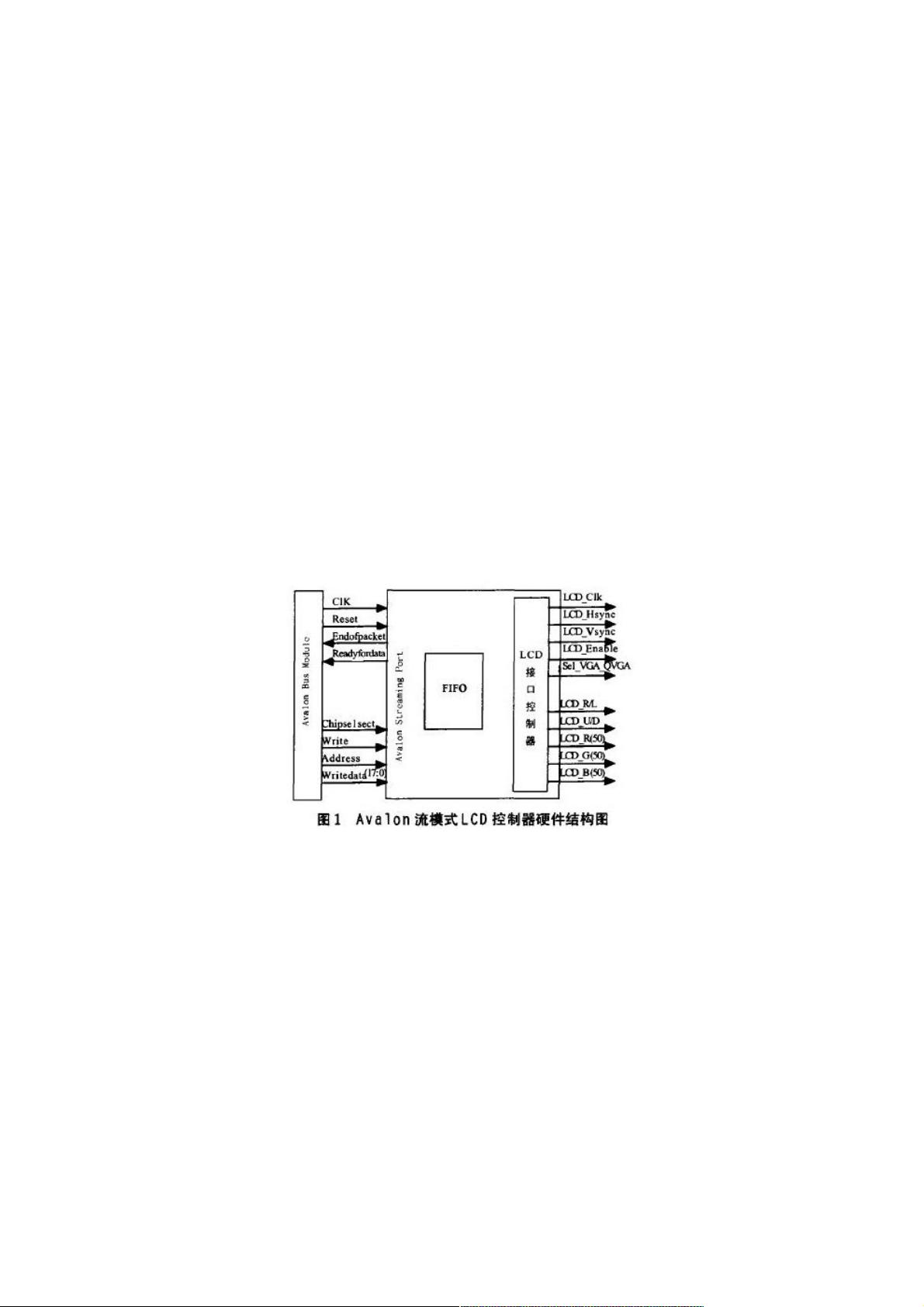

"基于NIOS II嵌入式处理器实现LCD的控制,利用FPGA中的NIOS II处理器来高效地管理LCD显示,通过DMA传输图像数据,并根据需求定制系统模块,提高系统的灵活性。采用软硬件结合的方式,使得在调试过程中可以通过调整软件来优化硬件功能。本文以SHARP的5.7英寸LCD-LQ057Q3DC02为例,描述了其选型和主要特性,包括18位色度信号和多种显示模式。设计了一个Avalon流模式的LCD控制器,由LCD接口控制器、FIFO存储器和Avalon Streaming Port接口组成,确保图像数据与控制信号的同步。"

在嵌入式系统中,使用NIOS II处理器作为FPGA(Field-Programmable Gate Array)中的核心,可以提供高度定制的解决方案,尤其适用于控制LCD显示。这种方案的优势在于,通过Direct Memory Access (DMA) 技术,能够高效地传输图像数据到LCD,减轻CPU的负担。系统可以根据具体应用需求选择不同的模块,增强了系统的可扩展性和适应性。

LCD选型上,SHARP的LCD-LQ057Q3DC02是一款具备320x240分辨率和18位颜色深度的显示屏,支持多种显示模式,如逐行扫描。其扫描过程是从左上角开始,水平扫描一行到右侧,然后回到左侧开始下一行,直至完成240行的扫描,形成一帧图像。

为了实现LCD的实时显示控制,设计了Avalon流模式的LCD控制器。Avalon是一种开放的片上系统(SoPC,System-on-a-Chip)互连架构,允许不同组件之间高效通信。控制器由三部分组成:LCD接口控制器负责与LCD的物理连接和信号处理,FIFO存储器用于缓存图像数据,以确保数据传输的连续性,而Avalon Streaming Port接口则作为控制器与系统其余部分交互的桥梁。

控制流程的关键在于行同步(LCD_Hsync)和场同步(LCD_Vsync)信号的精确配置,它们必须与从SDRAM中读取的图像数据保持同步。控制时序流程确保了这一点,保证图像的正确显示。在代码实现中,控制器通常包含多个模块,例如LCD_interface.vhd处理接口信号,LCD_pixel_fifo.v管理FIFO,而LCD_controller_stream.v作为顶层模块整合所有功能。

通过这样的设计,可以实现对LCD的精细控制,同时利用NIOS II的灵活性,可以快速调整控制策略,优化系统性能。这种软硬件结合的方法在嵌入式系统中非常常见,因为它提供了调试便利性和设计灵活性,同时降低了硬件更改的成本。

144 浏览量

116 浏览量

2009-04-06 上传

2021-09-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38701952

- 粉丝: 5

- 资源: 977

最新资源

- 通用3C电商网站左侧弹出菜单导航

- 的github

- 智睿企业视频版网站系统 v4.6.0

- 根据vo生成yapi文档:YapiFileGenerattor.zip

- install.zip

- CodeSoft 条形码标签打印开发指南

- GPT-too-AMR2text:复制“ GPT太”的代码

- counterspell:反咒诅咒的 Chrome 扩展

- CodingTestPractice

- 点文件

- 企业文化竞争(6个文件)

- pytorch-pruning.zip

- 天猫左侧导航菜单分类列表

- torch_sparse-0.6.1-cp36-cp36m-win_amd64whl.zip

- SiamSE:“比例等方差可改善连体跟踪”的代码

- BakedModpack:冒雨风险的modpack 2