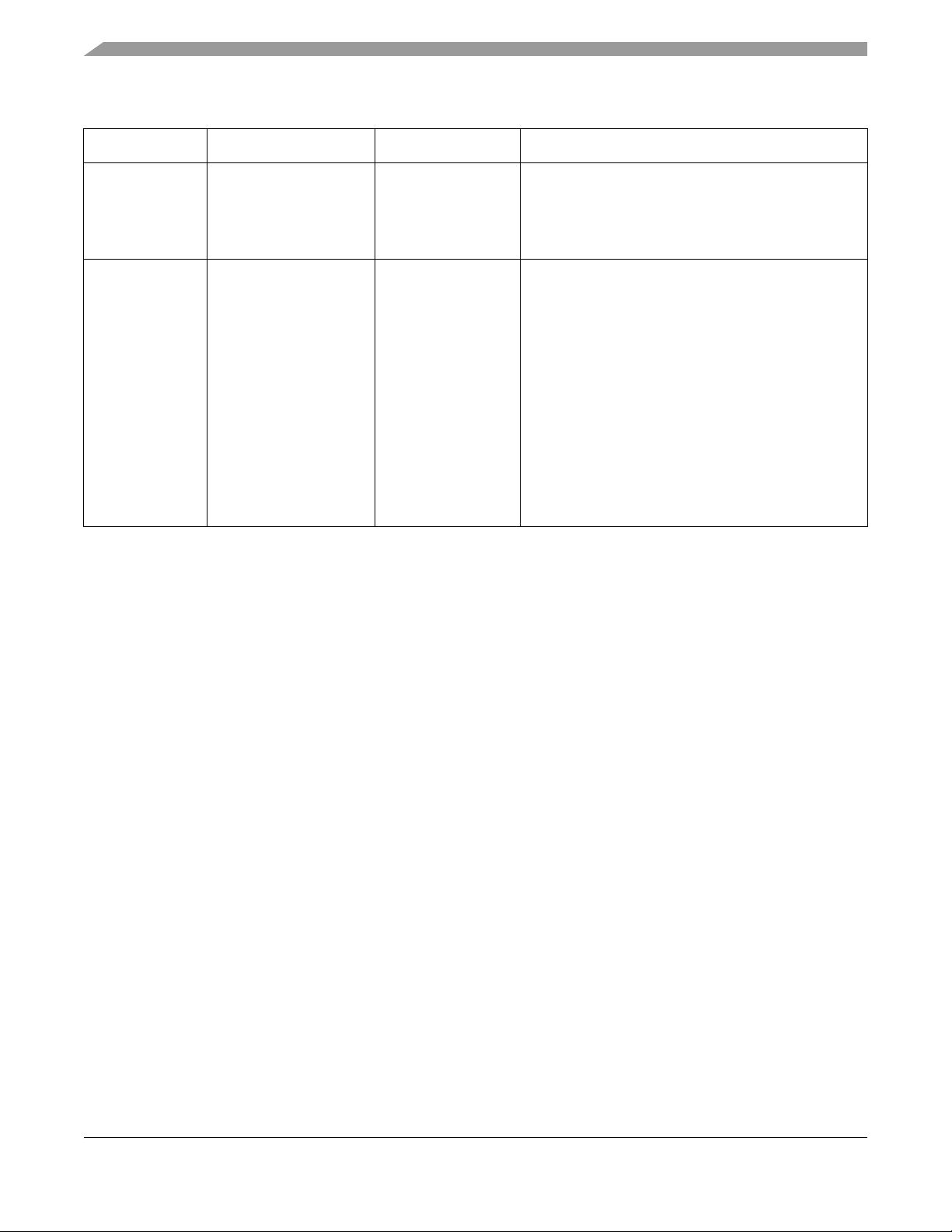

Modules list

i.MX 7Dual Family of Applications Processors Datasheet, Rev. 6, 02/2019

NXP Semiconductors18

DRAM_VREF When using DDR_VREF with DDR I/O, the nominal reference voltage must be half of the

NVCC_DRAM supply. The user must tie DDR_VREF to a precision external resistor divider. Use

a 1 kΩ 0.5% resistor to GND and a 1 kΩ 0.5% resistor to NVCC_DRAM. Shunt each resistor with

a closely-mounted 0.1 µF capacitor.

To reduce supply current, a pair of 1.5 kΩ 0.1% resistors can be used. Using resistors with

recommended tolerances ensures the ± 2% DDR_VREF tolerance (per the DDR3 specification)

is maintained when four DDR3 ICs plus the i.MX 7Dual are drawing current on the resistor divider.

It is recommended to use regulated power supply for “big” memory configurations (more than

eight devices)

ZQPAD DRAM calibration resistor 240 Ω 1% used as reference during DRAM output buffer driver

calibration should be connected between this pad and GND.

PCIE_VPH/PCIE_VPH_TX/

PCIE_VPH_RX

Short these pins to VDDA_PHY1P8 if using PCIe. User can tie these pins to ground if not using

PCIe.

PCIE_VP/PCIE_VP_TX/PC

IE_VP_RX

Short these pins to VDDD_1P0CAP if using PCIe. User can tie these pins to ground with a 10 KΩ

resistor if not using PCIe.

VDDA_MIPI_1P8 Short these pins to VDDA_PHY_1P8 if using MIPI. User can leave these pins floating or grounded

if not using MIPI.

VDD_MIPI_1P0 Short these pins to VDDD_1P0_CAP if using MIPI. User can leave these pins floating or grounded

if not using MIPI.

GPANAIO This signal is reserved for manufacturing use only. User must leave this connection floating.

JTAG_

nnnn

The JTAG interface is summarized in Table 4. Use of external resistors is unnecessary. However,

if external resistors are used, the user must ensure that the on-chip pull-up/down configuration is

followed. For example, do not use an external pull down on an input that has on-chip pull-up.

JTAG_TDO is configured with a keeper circuit such that the floating condition is eliminated if an

external pull resistor is not present. An external pull resistor on JTAG_TDO is detrimental and

should be avoided.

JTAG_MOD is referenced as SJC_MOD in the

i.MX 7Dual Application Processor Reference

Manual

(IMX7DRM). Both names refer to the same signal. JTAG_MOD must be externally

connected to GND for normal operation. Termination to GND through an external pull-down

resistor (such as 1 kΩ) is allowed. JTAG_MOD set to high configures the JTAG interface to a

mode compatible with the IEEE 1149.1 standard. JTAG_MOD set to low configures the JTAG

interface for common SW debug adding all the system TAPs to the chain.

NC Do not connect. These signals are reserved and should be floated by the user.

POR_B This cold reset negative logic input resets all modules and logic in the IC.

May be used in addition to internally generated power on reset signal (logical AND, both internal

and external signals are considered active low).

ONOFF In Normal mode, may be connected to ON/OFF button (De-bouncing provided at this input).

Internally this pad is pulled up. Short connection to GND in OFF mode causes internal power

management state machine to change state to ON. In ON mode short connection to GND

generates interrupt (intended to SW controllable power down). Long above ~5s connection to

GND causes “forced” OFF.

TEST_MODE TEST_MODE is for factory use. This signal is internally connected to an on-chip pull-down device.

The user must tie this signal to GND.

Table 3. Special signal considerations(continued)

Signal Name Remarks

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功

评论0