DSP芯片低功耗总线设计:新型编码算法与译码器结合

34 浏览量

更新于2024-09-02

收藏 215KB PDF 举报

"一种降低DSP芯片总线功耗的设计方案,通过新的编码算法和低功耗译码器,显著降低了数据总线和地址总线的功耗,平均减少21.56%的数据总线功耗和40.29%的地址总线功耗。"

在数字信号处理(DSP)领域,低功耗设计已经成为关键,特别是在移动设备中,如手机、掌上电脑和GPS系统,这些设备依赖于高效能且功耗低的DSP芯片。为了实现这一点,除了优化存储器设计,如采用Divided-Word-Line(DWL)译码技术降低内存功耗,还需要关注总线功耗,因为总线功耗在SoC(系统级芯片)中占据了相当大的比例,有时甚至高达总功耗的50%。

传统的低功耗设计策略往往忽略了总线功耗的问题,但随着集成电路工艺的不断进步,这个问题变得越来越突出。文献中的研究,如PaulP.Sotiriadis和AnanthaP.Chandrakasan的工作,提出了针对总线功耗的编码算法和译码器,例如Bus2InvertCode和T0Code等,已经在RISC架构处理器上显示出了良好的效果。

Bus2InvertCode译码器是一种常用的低功耗解码策略。在这个系统中,总线宽度设为N,原始数据b(t)经过编码变为B(t),然后传输到总线上。解码器J(t)的任务是将B(t)还原为b(t),确保数据的正确传递。这种译码器通过改变数据编码方式,减少了总线状态的切换,从而降低了因切换产生的动态功耗。

然而,对于DSP芯片来说,总线不仅需要承载数据,还有地址信息。因此,新的设计方案结合了特定的编码算法,旨在同时降低数据总线和地址总线的功耗。在实验中,这种方法针对常用的DSP算法进行测试,结果显示可以平均降低21.56%的数据总线功耗和40.29%的地址总线功耗。这表明,该设计方案对优化总线功耗具有显著的效果,对于提高DSP芯片的能效和延长设备电池寿命具有重要意义。

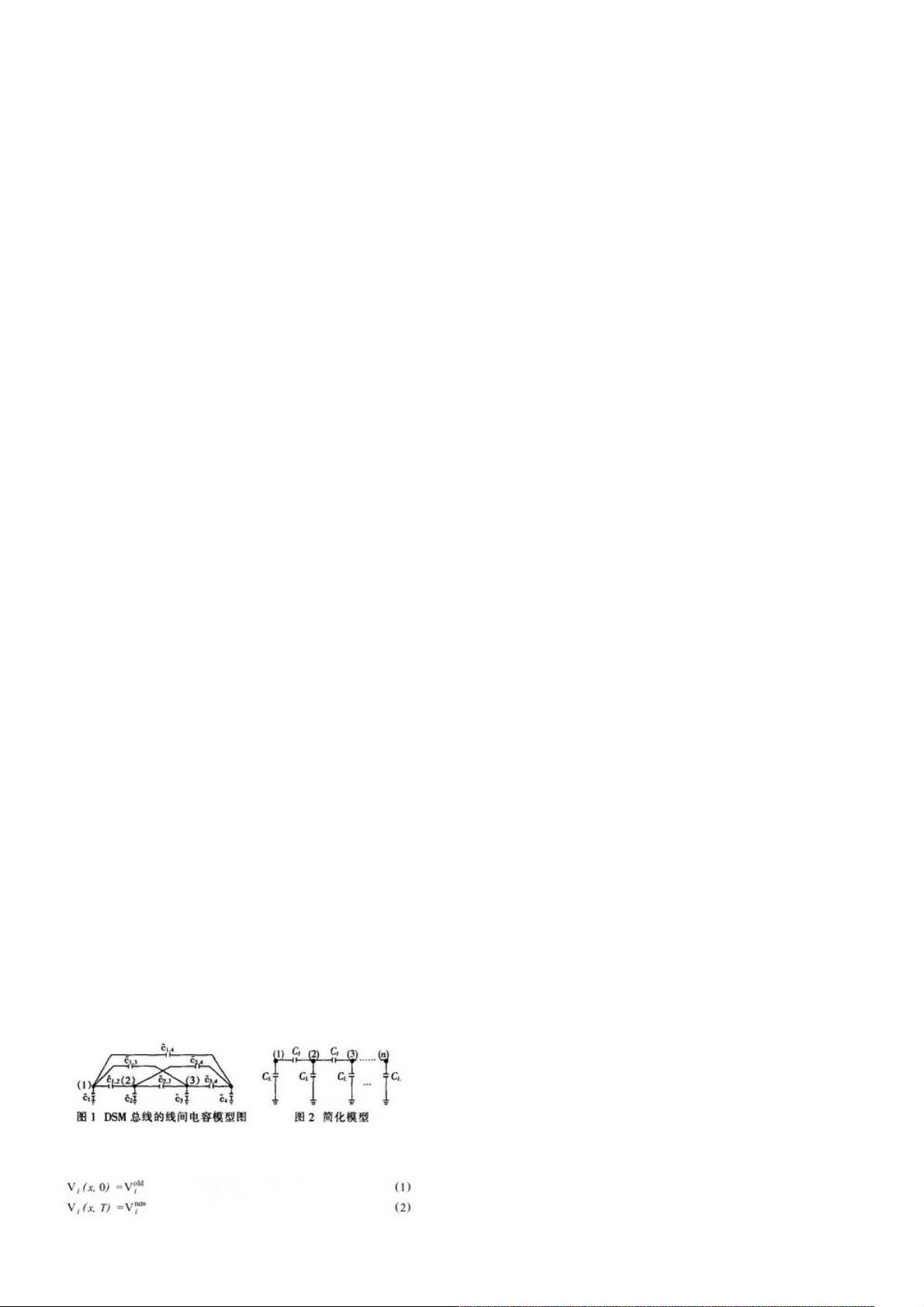

降低DSP芯片总线功耗的设计方案不仅涉及到创新的编码算法和低功耗译码器,还需要考虑总线与外部设备交互时的电容负载问题。通过这样的技术,可以有效地减少总线功耗,从而提升整个SoC系统的整体性能和效率。未来的研究可能会进一步探索更高级的编码技术,以适应更宽的总线宽度和更复杂的系统需求,持续推动低功耗DSP设计的进步。

2019-07-22 上传

2020-10-21 上传

2021-07-26 上传

2009-10-23 上传

2020-08-26 上传

2019-09-05 上传

2008-11-10 上传

2020-07-30 上传

2008-11-10 上传

weixin_38692666

- 粉丝: 6

- 资源: 914

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全