PRELIMINARY

VS1005g Datasheet

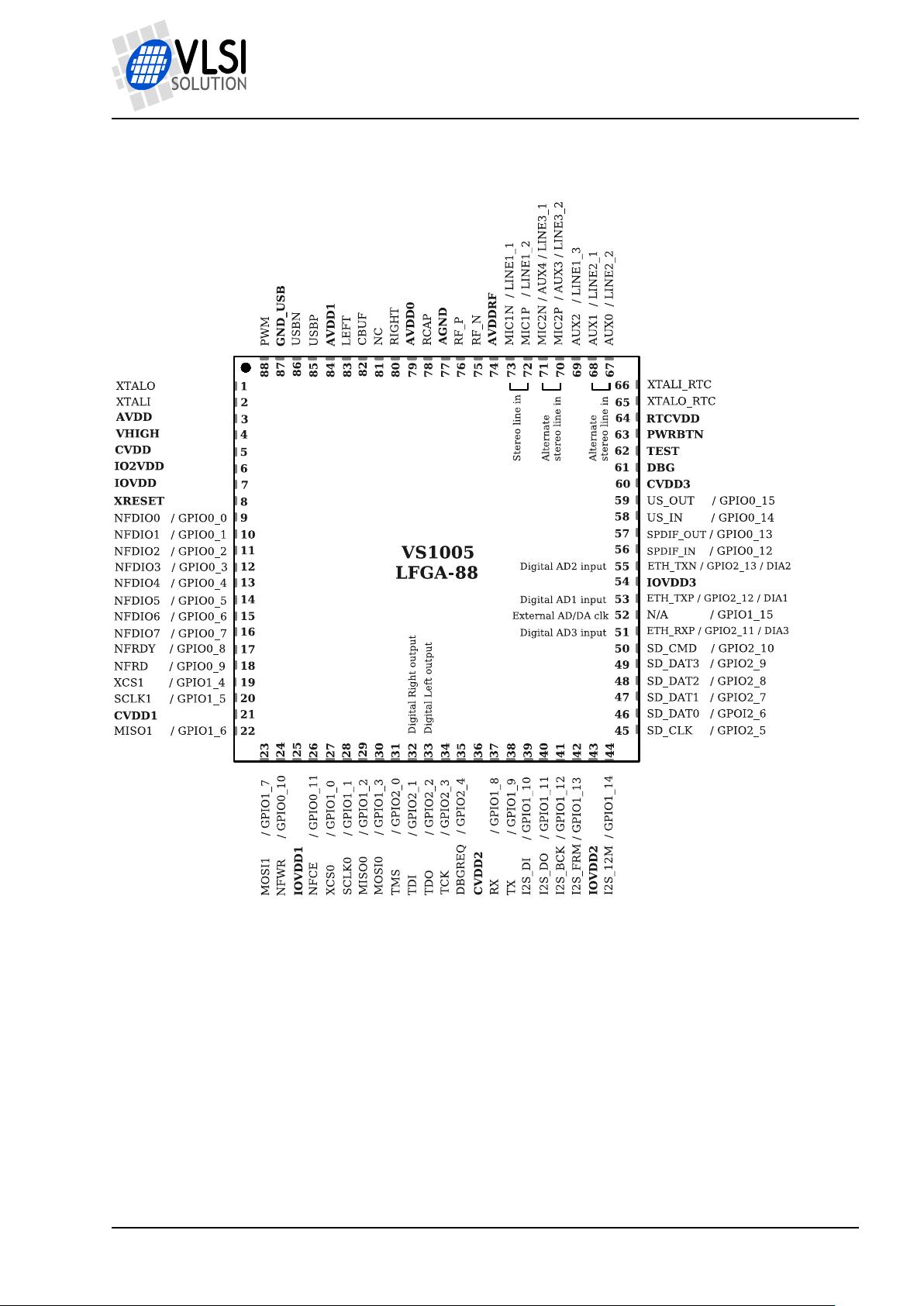

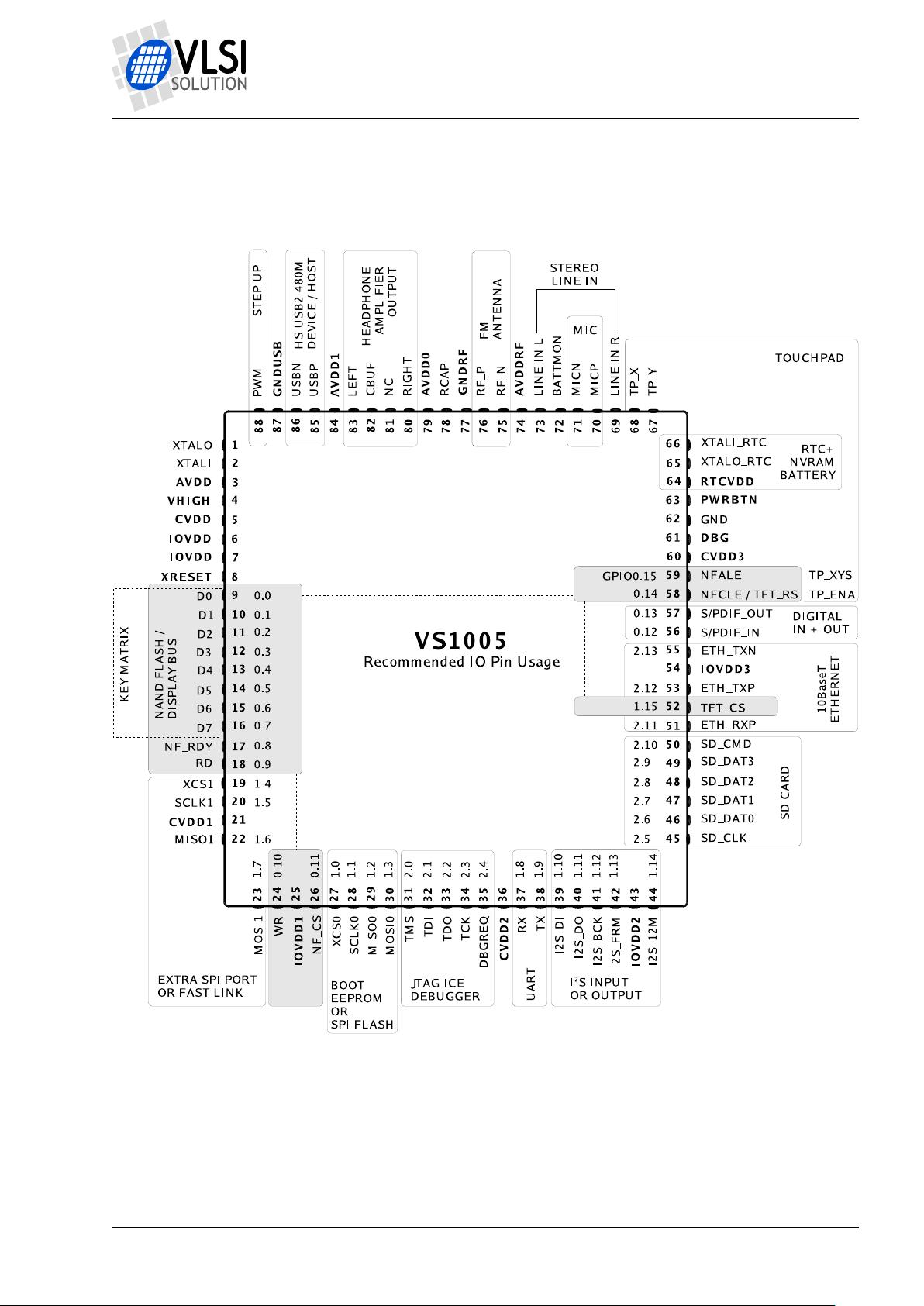

6 PACKAGE AND PIN DESCRIPTIONS

6.3 VS1005g Pin Descriptions

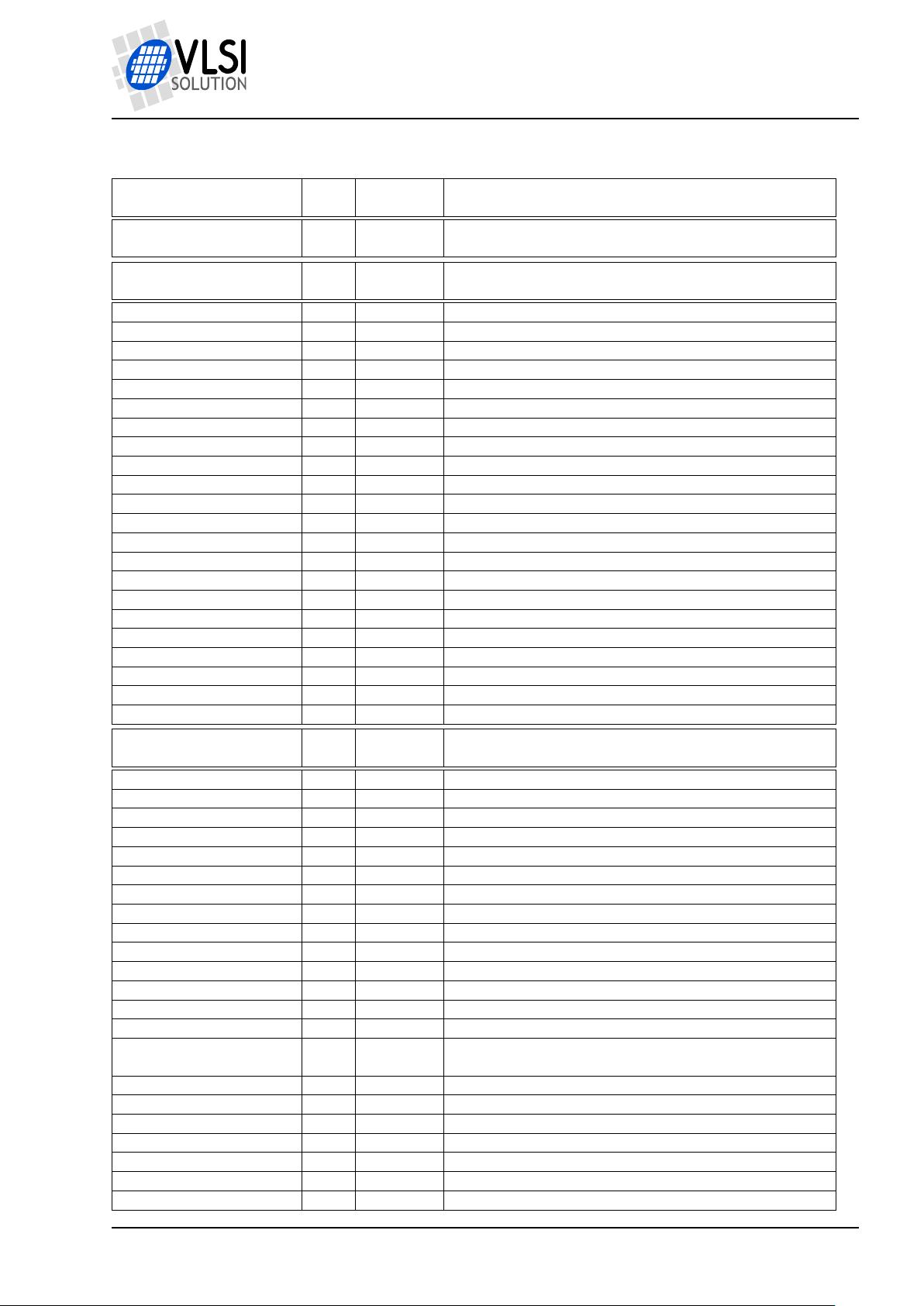

Pin Name LFGA

Pin

Pin Type Function

GPLATE (0) PWR Center ground plate, use multiple vias to create low-

impedance connection to ground network on PCB!

Pin Name LFGA

Pin

Pin Type Function

XTALO 1 AO Crystal output

XTALI 2 AI Crystal input

AVDD 3 APWR Analog power supply, Regulator output

VHIGH 4 PWR Power supply, Regulator input

CVDD 5 CPWR Core power supply, Regulator output

IO2VDD 6 IO2PWR Serial Flash power supply, Regulator output

IOVDD 7 IOPWR I/O power supply, Regulator output

XRESET 8 DI Active low asynchronous reset, schmitt-trigger input

NFDIO0 / GPIO0_0 9 DIOPD Nand-flash IO0 / General-purpose IO Port 0, bit 0

NFDIO1 / GPIO0_1 10 DIOPD Nand-flash IO1 / General-purpose IO Port 0, bit 1

NFDIO2 / GPIO0_2 11 DIOPD Nand-flash IO2 / General-purpose IO Port 0, bit 2

NFDIO3 / GPIO0_3 12 DIOPD Nand-flash IO3 / General-purpose IO Port 0, bit 3

NFDIO4 / GPIO0_4 13 DIOPD Nand-flash IO4 / General-purpose IO Port 0, bit 4

NFDIO5 / GPIO0_5 14 DIOPD Nand-flash IO5 / General-purpose IO Port 0, bit 5

NFDIO6 / GPIO0_6 15 DIOPD Nand-flash IO6 / General-purpose IO Port 0, bit 6

NFDIO7 / GPIO0_7 16 DIOPD Nand-flash IO7 / General-purpose IO Port 0, bit 7

NFRDY / GPIO0_8 17 DIO Nand-flash READY / General-purpose IO Port 0, bit 8

NFRD / GPIO0_9 18 DIO Nand-flash RD / General-purpose IO Port 0, bit 9

XCS1 / GPIO1_4 19 DIOPD SPI1 XCS / General-Purpose I/O Port 1, bit 4

SCLK1 / GPIO1_5 20 DIOPD SPI1 CLK / General-Purpose I/O Port 1, bit 5

CVDD1 21 CPWR Core power supply, connect to regulator CPWR

MISO1 / GPIO1_6 22 DIOPD SPI1 MISO / General-Purpose I/O Port 1, bit 6

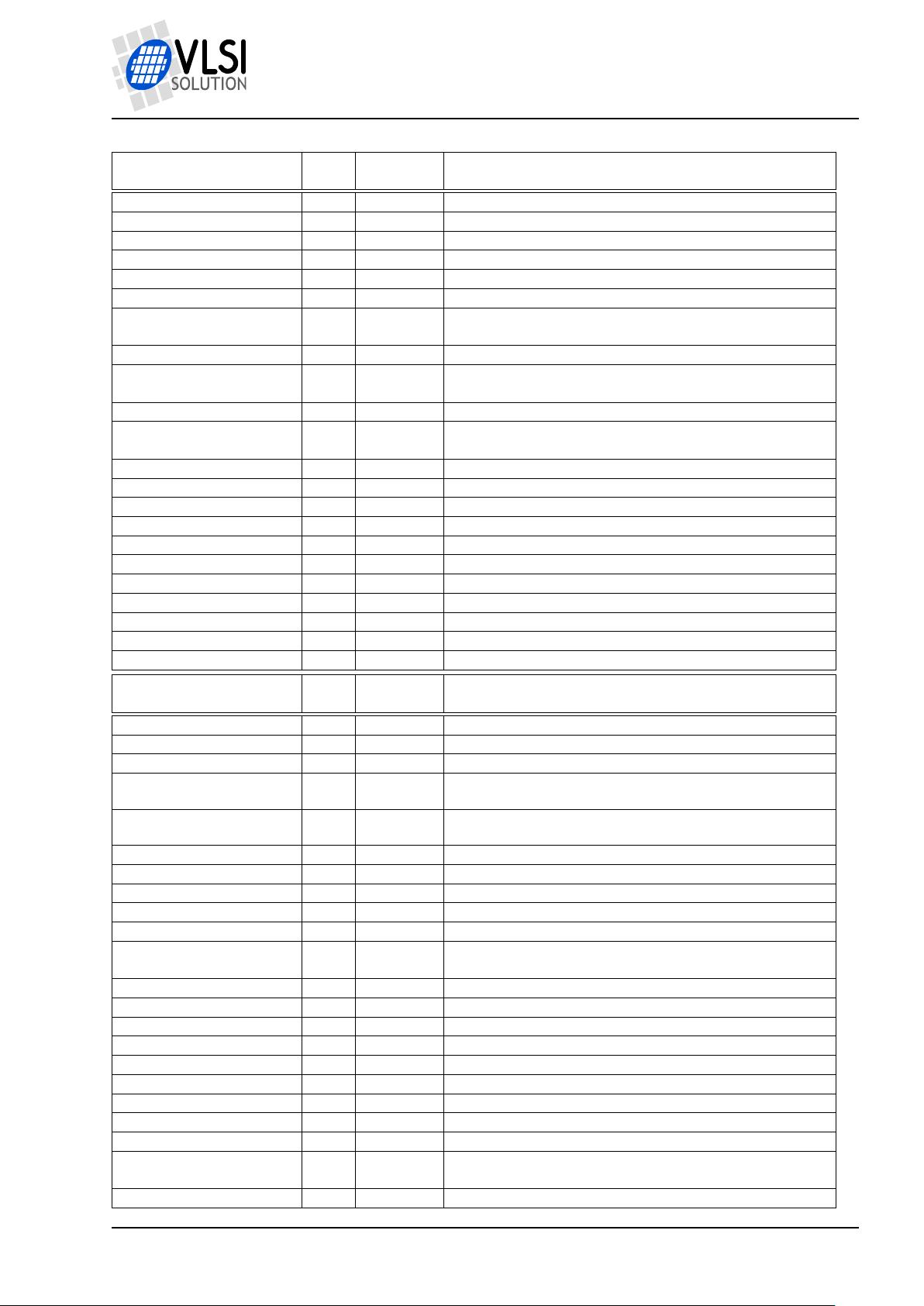

Pin Name LFGA

Pin

Pin Type Function

MOSI1 / GPIO1_7 23 DIOPD SPI1 MOSI / General-Purpose I/O Port 1, bit 7

NFWR / GPIO0_10 24 DIO Nand-flash WR / General-purpose IO Port 0, bit 10

IOVDD1 25 IOPWR I/O power supply, connect to regulator IOPWR

NFCE / GPIO0_11 26 DIOPD Nand-flash CE / General-purpose IO Port 0, bit 11

XCS0 / GPIO1_0 27 DIOPD SPI0 XCS / General-Purpose I/O Port 1, bit 0

SCLK0 / GPIO1_1 28 DIOPD SPI0 CLK / General-Purpose I/O Port 1, bit 1

MISO0 / GPIO1_2 29 DIOPD SPI0 MISO / General-Purpose I/O Port 1, bit 2

MOSI0 / GPIO1_3 30 DIOPD SPI0 MOSI / General-Purpose I/O Port 1, bit 3

TMS / GPIO2_0 31 DIOPD JTAG TMS / General-Purpose I/O Port 2, bit 0

TDI / GPIO2_1 32 DIOPD JTAG TDI / General-Purpose I/O Port 2, bit 1

TDO / GPIO2_2 33 DIOPD JTAG TDO / General-Purpose I/O Port 2, bit 2

TCK / GPIO2_3 34 DIOPD JTAG TCK / General-Purpose I/O Port 2, bit 3

DBGREQ / GPIO2_4 35 DIOPD Debug interrupt / General-Purpose I/O Port 2, bit 4

CVDD2 36 CPWR Core power supply, connect to regulator CPWR

RX / GPIO1_8 37 DIO UART RX / General-Purpose I/O Port 1, bit 8

(connect with 100 kΩ to IOVDD if not used for UART)

TX / GPIO1_9 38 DIO UART TX / General-Purpose I/O Port 1, bit 9

I2S_DI / GPIO1_10 39 DIOPD I2S data in / General-Purpose I/O Port 1, bit 10

I2S_DO / GPIO1_11 40 DIOPD I2S data out / General-Purpose I/O Port 1, bit 11

I2S_BCK / GPIO1_12 41 DIOPD I2S bit clock / General-Purpose I/O Port 1, bit 12

I2S_FRM / GPIO1_13 42 DIOPD I2S frame sync / General-Purpose I/O Port 1, bit 13

IOVDD2 43 IOPWR I/O power supply, connect to regulator IOPWR

I2S_12M / GPIO1_14 44 DIOPD I2S XTALI clock output / General-Purpose I/O Port 1, bit 14

Version: 0.52, 2012-11-07 17