FPGA实战:10种Verilog设计电路实验详解

需积分: 0 192 浏览量

更新于2024-07-15

3

收藏 987KB DOC 举报

在FPGA系统的设计实验中,涵盖了多个核心的数字电路模块,使用Verilog语言进行实现,这些模块包括:

1. **4位半加法器**:这是实验一的基础,通过Verilog代码设计一个可以执行加法运算的电路,接收两个4位输入(a和b),输出结果存储在sum,进位信号cout通过逻辑运算直接生成。例如,当A=0101和B=1010时,会计算出sum=1111(15),由于超过4位,产生了cout=0的溢出。

2. **138译码器**:该部分实验将学习如何设计一个多路选择器,用于解码138个不同的输入组合,实现多种功能。

3. **并行输入串行输出移位寄存器**:通过Verilog实现一个能将并行输入逐位串行输出的电路,这对于数据的序列处理和存储非常有用。

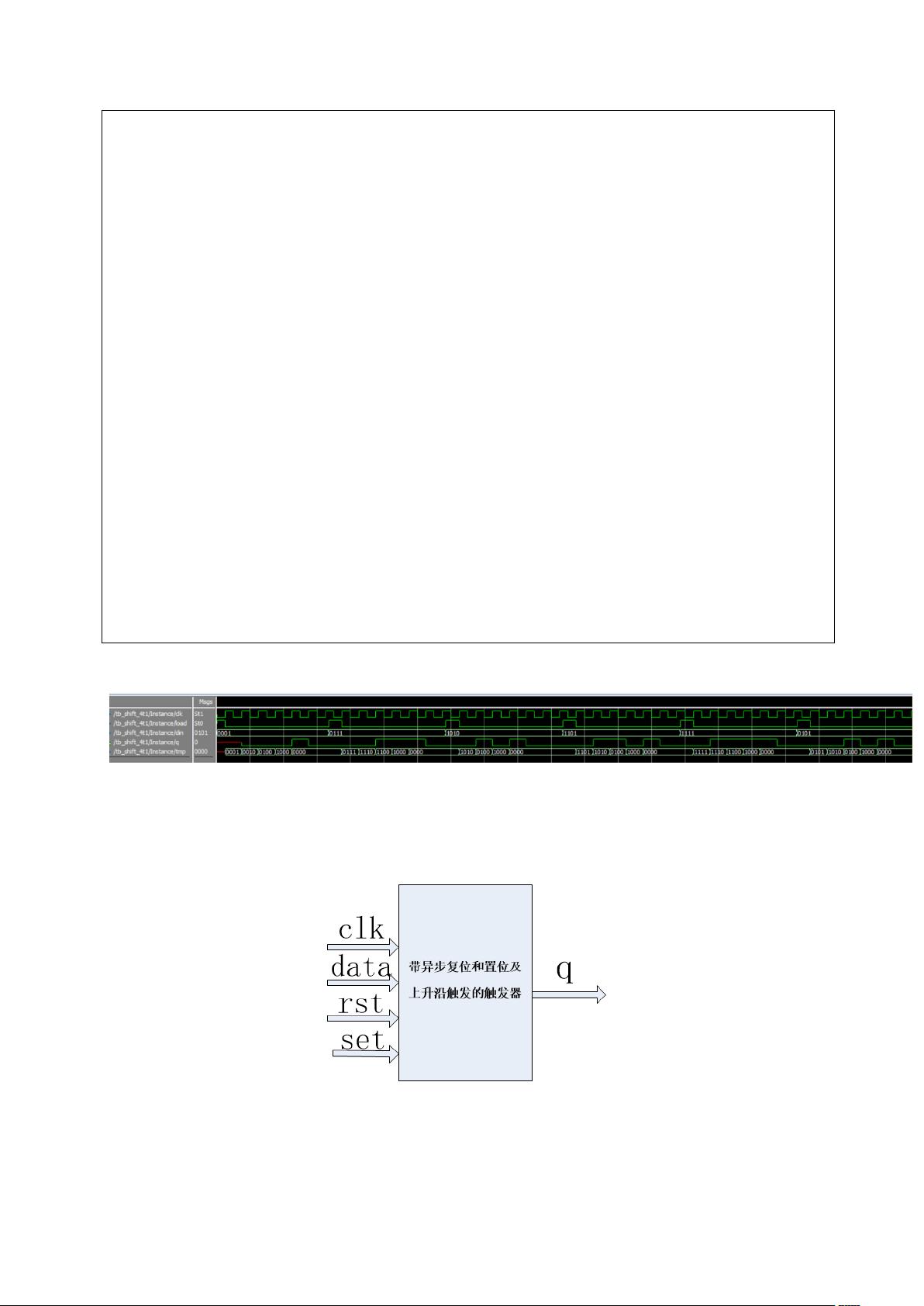

4. **触发器**:实验涉及带有异步复位和置位功能的触发器,理解触发器的时序特性以及它们在系统中的作用。

5. **模10计数器**:用于实现循环计数,当计数值达到10时重置,常用于显示或周期性操作的控制。

6. **停车位剩余计数显示牌**:这可能是一个更复杂的数字系统,它结合了计数器和显示功能,用于模拟停车场的剩余车位信息。

7. **银行排号机系统电路**:涉及实时排队系统的硬件设计,可能包括计数器、选择器等模块。

8. **分频器**:实验包括不同类型的分频器,如2的偶数分频、16分频(占空比为2:14)和5分频,这有助于理解时钟管理在系统中的应用。

9. **四选一数据选择器**:通过编写TB(Testbench)进行仿真,测试数据选择器的正确性和灵活性。

10. **ASK调制、FSK调制**:实验可能涉及到数字信号处理技术,使用Verilog实现模拟幅度键控(ASK)和频率键控(FSK)调制,用正弦波作为载波信号。

以上内容均是《EDA技术与FPGA系统开发》课程中的实践项目,旨在让学生深入理解数字电路的原理和Verilog编程在实际硬件设计中的运用,通过动手实践提高理论知识与实际操作的结合能力。每个模块的实现都需要对电路原理有清晰的认识,并能熟练运用Verilog语言进行描述和仿真验证。

179 浏览量

点击了解资源详情

点击了解资源详情

147 浏览量

1186 浏览量

2022-09-24 上传

2015-06-06 上传

2022-11-07 上传

171 浏览量

夜半少年

- 粉丝: 6971

最新资源

- ASP.NET集成支付宝即时到账支付流程详解

- C++递推法在解决三道经典算法问题中的应用

- Qt_MARCHING_CUBES算法在面绘制中的应用

- 传感器原理与应用课程习题解答指南

- 乐高FLL2017-2018任务挑战解析:饮水思源

- Jquery Ui婚礼祝福特效:经典30款小型设计

- 紧急定位伴侣:蓝光文字的位置追踪功能

- MATLAB神经网络实用案例分析大全

- Masm611: 安全高效的汇编语言调试工具

- 3DCurator:彩色木雕CT数据的3D可视化解决方案

- 聊天留言网站开发项目全套资源下载

- 触摸屏适用的左右循环拖动展示技术

- 新型不连续导电模式V_2控制Buck变换器研究分析

- 用户自定义JavaScript脚本集合分享

- 易语言实现非主流方式获取网关IP源码教程

- 微信跳一跳小程序前端源码解析

已收录资源合集

已收录资源合集