直接序列扩频系统(DS-SS)数字相关器设计与实现

需积分: 9 79 浏览量

更新于2024-08-12

收藏 248KB PDF 举报

"直接序列扩频系统(DS-SS)中数字相关器的研究,通过匹配滤波器在FPGA上实现,应用于无线接力机。"

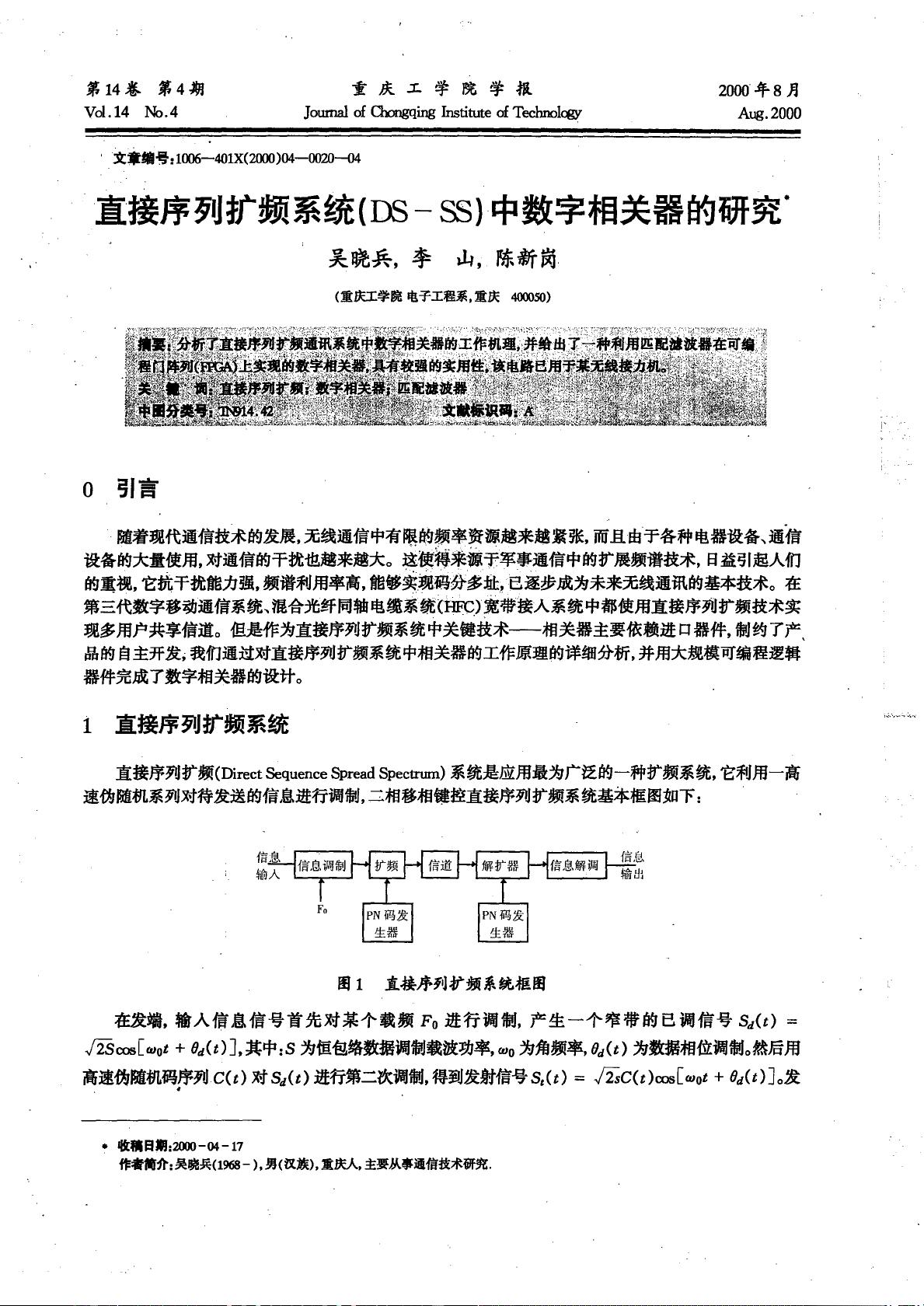

本文深入探讨了直接序列扩频(DS-SS)系统中的关键组件——数字相关器的工作原理和设计方法。直接序列扩频是一种扩展频谱技术,其在现代通信中发挥着重要作用,特别是在解决频率资源紧张、抵抗干扰和实现码分多址通信方面。随着无线通信技术的发展,DS-SS已成为第三代数字移动通信系统、混合光纤同轴电缆系统以及宽带接入系统等多用户共享信道的关键技术。

在DS-SS系统中,信息信号首先经过载频调制,生成窄带已调信号。接着,高速伪随机码序列(通常称为扩频码或PN码)对已调信号进行二次调制,形成发射信号。这个过程增加了信号的频谱宽度,增强了抗干扰能力。在接收端,接收到的信号包含信号和干扰,通过匹配滤波器实现的数字相关器与本地扩频码同步,完成解扩,恢复原始信息。

数字相关器在FPGA上实现的优势在于其灵活性和可编程性,可以针对不同的通信需求进行定制。文中提到的具体设计利用了匹配滤波器的特性,这种滤波器的频率响应与扩频码的自相关函数相匹配,能够在最佳时间点产生最大的输出信号,从而准确地检测和提取信息。

设计中的一个重要环节是估计传输延迟`t"d`,这是通过比较接收到的信号与本地扩频码相位关系来完成的。当两者相位匹配时,相关器的输出将达到最大,从而确定最佳的延迟值,进而解扩并还原原始信息。

文章作者通过详细分析DS-SS系统的运作机制,设计并实现了基于FPGA的数字相关器,这一设计在实际的无线接力机中得到了应用,表明了其在实际通信系统中的实用性和有效性。采用国产化器件对于推动自主产品的开发具有重要意义,降低了对外部进口器件的依赖。

这篇2000年的论文研究了DS-SS系统中的数字相关器,强调了其在通信抗干扰、频谱利用率和码分多址通信中的核心地位,同时提供了基于FPGA的实现方案,为后续的通信系统设计提供了理论和技术支持。

2021-06-01 上传

2022-09-19 上传

2022-11-03 上传

2021-08-12 上传

2022-09-21 上传

2022-09-23 上传

2021-09-04 上传

点击了解资源详情

点击了解资源详情

weixin_38705558

- 粉丝: 4

- 资源: 943

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用