DDR3硬件与Layout设计指南

需积分: 0 153 浏览量

更新于2024-08-04

1

收藏 814KB PDF 举报

"DDR3硬件设计和Layout设计中为电子科技工作室. 飞思卡尔官方文档 HardwareandLayoutDesignConsiderationsforDDR3SDRAMMemoryInterfaces"

DDR3内存系统的设计涉及多个关键方面,包括硬件设计检查、终端匹配电阻的计算、VREF电压、VTT电压轨、布线策略以及仿真验证。以下是对这些知识点的详细说明:

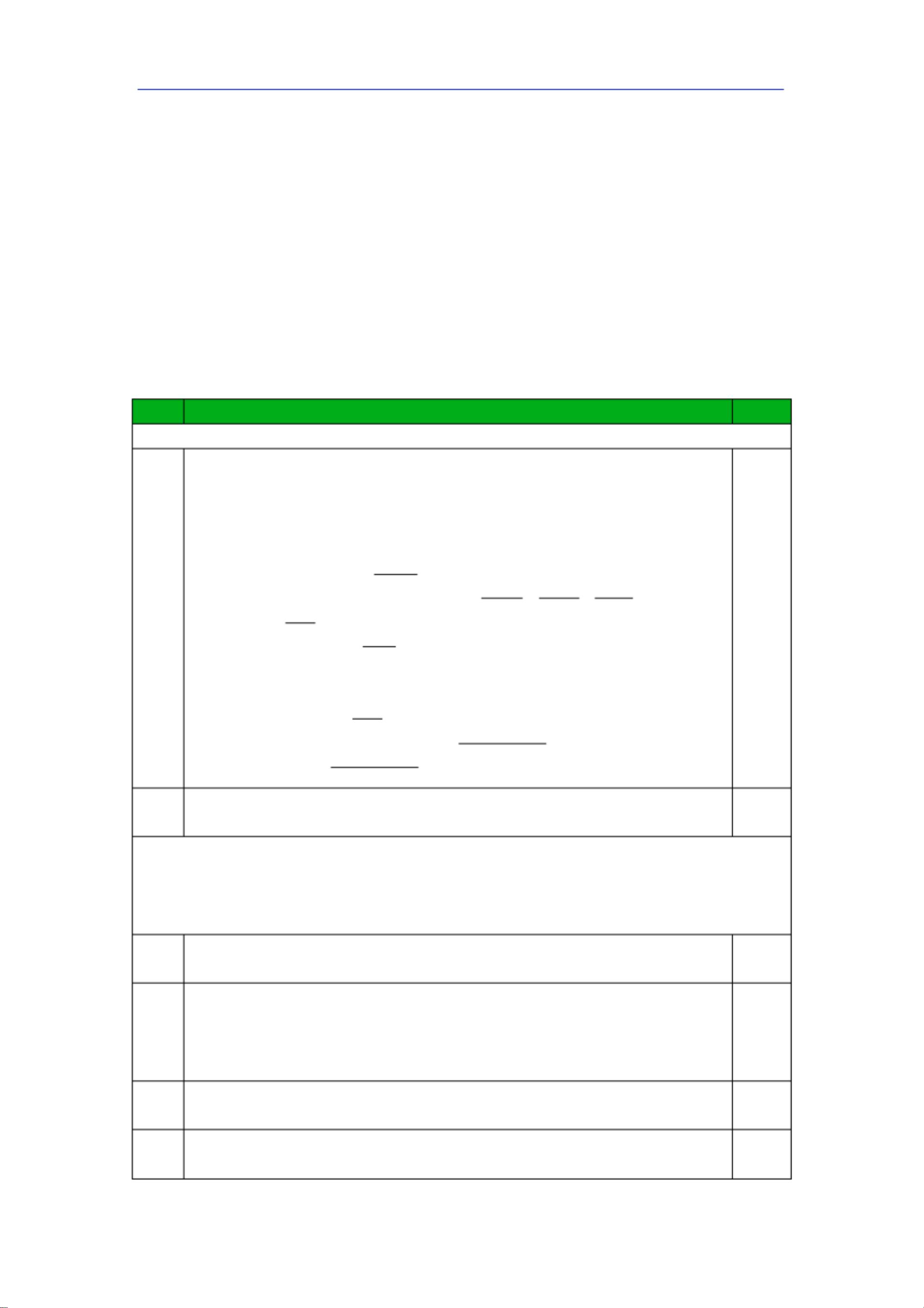

1. **设计检查表**:设计检查表是确保DDR3系统设计质量的关键工具。表中包含了对终端匹配电阻、信号线拓扑和走线长度等重要因素的检查。在设计过程中,需要通过仿真来优化这些参数。此外,如果使用了ODT(On-Die Termination),则可以减少外部终端匹配电阻的需求。DDR3的数据组、地址/命令组、控制组和时钟组的走线配置需要符合特定的分组规则。

2. **终端匹配电阻功耗计算**:终端匹配电阻用于消除信号反射,改善信号完整性和时序。计算功耗时要考虑DDR3的电源电压、电阻值和信号速率等因素。匹配电阻的选择对于信号质量和系统功耗都有直接影响。

3. **VREF**:VREF是DDR3内存接口的参考电压,它对信号质量至关重要。正确设置VREF能确保信号的准确传输,需要根据具体DDR3器件的规格来设定。

4. **VTT电压轨**:VTT是终端匹配电阻的电源电压,通常低于VDDQ(数据线电源)。确保VTT的稳定和正确设置可以避免信号失真和噪声问题。

5. **DDR布线**:DDR3的布线设计有严格的要求,尤其是数据线MDQ、MDQS、MDM、MECC等。数据线应按照分组规则进行布局,同时考虑到信号的延迟和平衡。此外,布局时还要注意信号线的长度匹配,以保持信号的同步。

- **数据线**:64位数据线加上8位ECC,共72位。某些设计可能只有32位数据线,对应的控制信号也会相应减少。

- **Layout建议**:应遵循最小化走线长度、减少串扰、保持信号线对齐等原则,以提高信号完整性。

6. **仿真**:在设计完成后,必须进行仿真验证,包括信号完整性仿真和时序仿真,以确保设计满足DDR3的高速传输要求和时序约束。

7. **扩展阅读**:除了上述内容,还有更多关于DDR3设计的深入阅读材料,可能涵盖更多细节,如电源管理、热设计、EMI控制等。

在实际的DDR3硬件设计中,理解并正确应用这些知识点至关重要,以确保系统的可靠性和性能。设计者需要考虑每个环节的相互影响,通过严谨的设计流程和验证方法,来构建高效、低功耗且稳定的DDR3内存系统。

135 浏览量

2023-01-12 上传

2023-11-30 上传

2023-07-28 上传

2023-07-27 上传

2023-05-30 上传

2023-08-02 上传

2023-07-28 上传

2023-06-05 上传

程序猿徐师兄

- 粉丝: 613

- 资源: 2287

最新资源

- 最优条件下三次B样条小波边缘检测算子研究

- 深入解析:wav文件格式结构

- JIRA系统配置指南:代理与SSL设置

- 入门必备:电阻电容识别全解析

- U盘制作启动盘:详细教程解决无光驱装系统难题

- Eclipse快捷键大全:提升开发效率的必备秘籍

- C++ Primer Plus中文版:深入学习C++编程必备

- Eclipse常用快捷键汇总与操作指南

- JavaScript作用域解析与面向对象基础

- 软通动力Java笔试题解析

- 自定义标签配置与使用指南

- Android Intent深度解析:组件通信与广播机制

- 增强MyEclipse代码提示功能设置教程

- x86下VMware环境中Openwrt编译与LuCI集成指南

- S3C2440A嵌入式终端电源管理系统设计探讨

- Intel DTCP-IP技术在数字家庭中的内容保护