Verilog inout端口详解与常见错误避免

版权申诉

186 浏览量

更新于2024-08-26

收藏 706KB PDF 举报

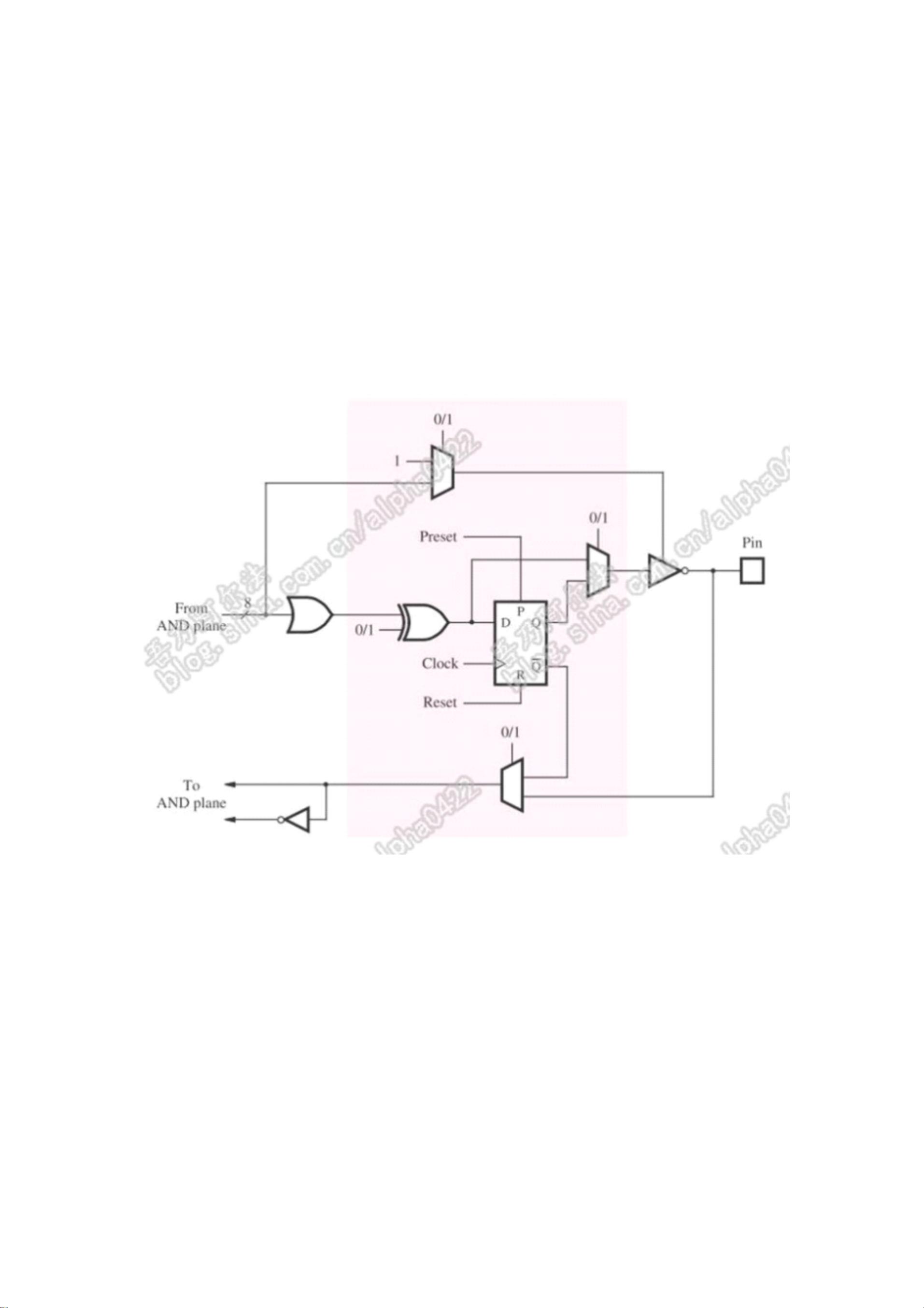

Verilog语言中的inout端口是模拟硬件中双向端口的重要特性,它允许信号在输入和输出之间切换。在FPGA设计中,inout端口通常由三态门实现,这种门具有三个状态:高电平、低电平和高阻态(Z)。在高阻态下,信号处于悬空状态,不会影响其他电路。

使用inout端口时,需要注意几个关键点:

1. 双向性依赖:inout端口本质上是不能独立存在的,因为它们总是与其他inout端口相连,形成双向通信。这意味着,在模块设计中,如果某个端口被定义为inout,与其相连的另一个端口也必须是inout类型,以便实现数据的双向传输。

2. 输入缓冲:当inout端口用作输入时,它需要与一个reg型缓冲器配合使用,这是因为inout端口本身并不能单独处理输入。例如,当control信号为真时,三态门打开,DataOut的数据会被传输到DataBus,而DataIn则需通过缓冲器与DataOut进行数据交换,以确保输入信号的正确传递。

3. 信号交错控制:连接两个inout端口时,需要对信号的驱动和接收进行精细管理。通常,一对信号会交替控制这两个端口,避免了信号冲突和潜在的竞态条件。

在编写Verilog代码时,尤其是描述复杂的系统架构,如CPU和内存之间的交互,必须充分考虑到inout端口的这些特性。在描述CPU模块时,不仅要描述其内部逻辑,还要明确其与内存或其他inout端口的连接方式,包括数据总线的共享和管脚复用策略。

理解并正确使用Verilog中的inout端口是实现高效、准确的硬件描述的关键,它要求设计者具备对硬件行为深入的理解和对Verilog语法规则的熟练掌握。在实际应用中,遵循正确的设计原则和最佳实践,可以避免许多潜在的问题,提升设计的可靠性和效率。

125 浏览量

107 浏览量

1208 浏览量

114 浏览量

166 浏览量

2019-06-18 上传

206 浏览量

119 浏览量

176 浏览量

dtd13961139571

- 粉丝: 1

- 资源: 6万+

最新资源

- phaser-starter-templates:Phaser游戏框架的入门模板

- memorammstein.github.io:个人网站

- tcc-machine-vision:瓦斯生产和销售制度。停车场空位识别系统

- 商业编程-源码-Gridview控件用法Demo.zip

- html5模拟鲨鱼动画效果

- sinric-tv:ESP8266草图,为Sony KDL60R510A使用SinricPro电视设备

- phaser3-vjoy-plugin:Phaser3的虚拟操纵杆插件

- 如何才能编译Linux的内核-综合文档

- IMU_Kalman-filter_MATLAB.zip

- tray-deprecator-dashboard

- jodconverter.rar

- ULTRAMAT 23型红外气体分析仪.zip

- phaser-manifest-loader:Phaser清单加载器

- micro_pyblock:用于micropython的简单伪随机数块堆叠算法

- word-export:填充word模板

- livres:使用Google Books API的android应用