ZedBoard电路设计与应用参考

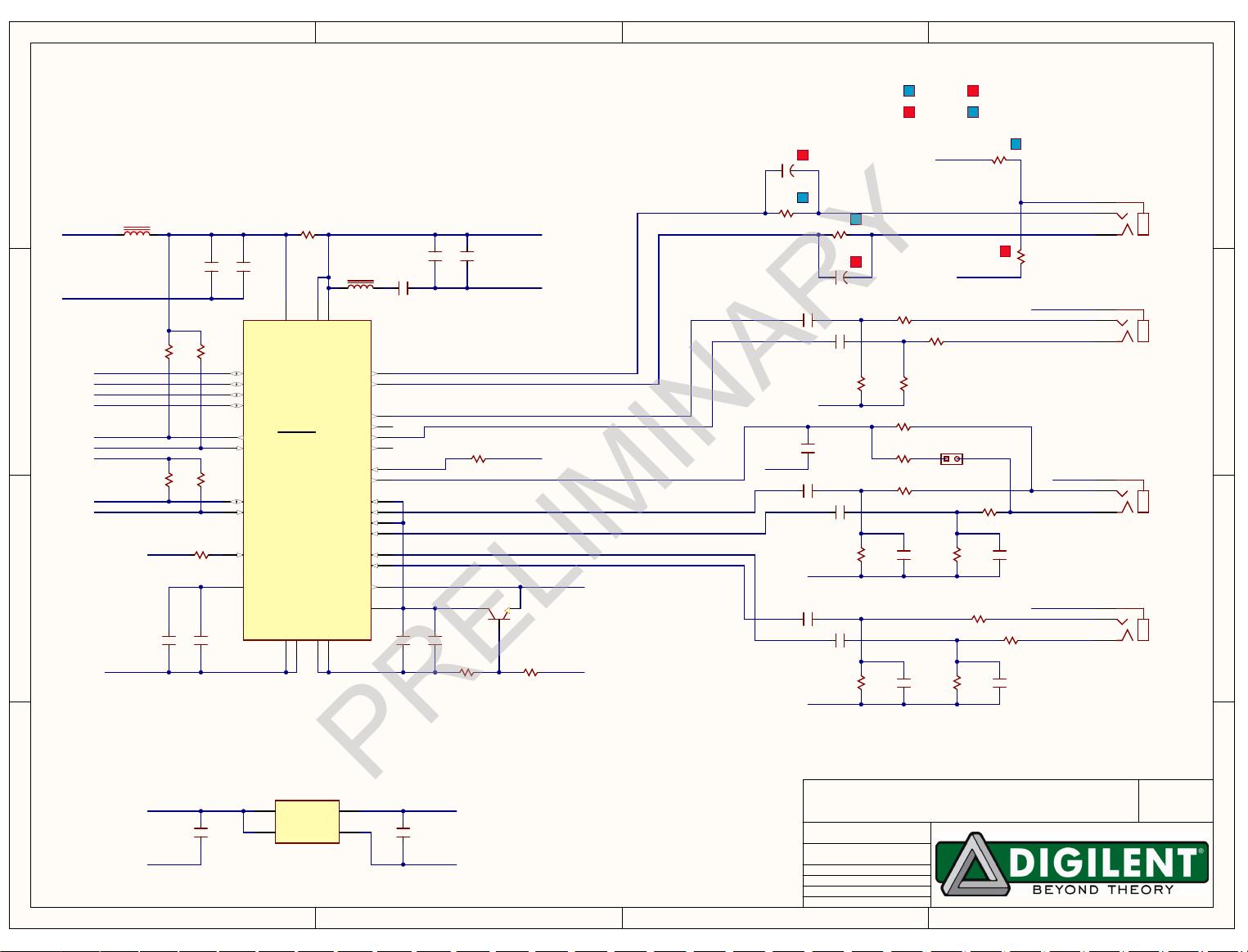

"ZedBoard典型运用电路图展示了Xilinx最新器件的参考设计,适用于了解如何在实际应用中正确配置和连接ZedBoard。"

ZedBoard是基于Xilinx Zynq-7000 All Programmable System-on-Chip (SoC) 的开发板,它集成了ARM Cortex-A9双核处理器和可编程逻辑单元,提供了丰富的接口和功能,广泛应用于教育、研究和原型设计等领域。电路图中的信息揭示了ZedBoard与外部设备的连接方式,包括电源、I/O接口以及通信总线等关键部分。

1. **电源与接地**:图中包含多个GND(接地)引脚,确保电路的稳定运行。VU12V0和VCC3V3则代表不同电压等级的电源引脚,分别提供12V和3.3V的工作电压,这些电源对于供电至关重要,保证了ZedBoard内部组件的正常工作。

2. **FPGA I/O接口**:FMC(FPGA Mezzanine Card)接口是一种标准的高速连接器,用于扩展FPGA的功能。图中所示的FMC-LA系列引脚,如FMC-LA01_CC_P/N、FMC-LA05_N/P等,代表FPGA的差分信号线,可用于高速数据传输,如PCIe、Gigabit Ethernet等。

3. **I2C总线**:FMC-SCL和FMC-SDA是I2C(Inter-Integrated Circuit)接口的时钟和数据线,用于控制和通信各种外设,如传感器、存储器等。它们是两线制的低速通信协议,适合短距离、低数据率的设备连接。

4. **复位信号**:PS-POR-B是处理器系统(PS)的复位信号,当此信号被拉低时,会触发系统的复位操作,重置所有相关寄存器和硬件状态。

5. **时钟输入**:FMC-CLK1_N可能是一个时钟输入引脚,为Zynq SoC提供外部时钟源,对于高性能和同步操作非常重要。

6. **其他未标记的引脚**:图中还有其他未明确标注的引脚,可能涉及到其他的I/O接口、控制信号或电源引脚,具体功能需参照ZedBoard的官方文档进行解读。

使用ZedBoard进行项目开发时,理解这些接口和连接方式是至关重要的。电路图提供了基本的连接指南,但实际应用中可能需要根据具体的设计需求进行适当的修改和配置。同时,由于设计材料没有提供任何保修,开发者应自行承担使用风险,必要时寻求专业技术支持以确保设计的正确性和稳定性。

997 浏览量

437 浏览量

128 浏览量

250 浏览量

259 浏览量

2022-09-23 上传

128 浏览量

u010135012

- 粉丝: 0

- 资源: 1

最新资源

- a-simple-mvc-rest-service:包含带有 TDD 的示例模块的简单 RESTJersey 项目,用 Java 实现

- weather_api

- BudgetTracker:无论有没有连接,用户都可以在其预算中添加费用和存款。 脱机输入交易时,当它们重新联机时应填充总数

- Google_intro:对于Dsl的布局,时间不够。

- dnvod-ad-killer:dnvod.tv的AD卸妆

- 信号与系统 实验作业

- NativeTop.NiceDream.ga4Usk4

- TouTiaoAd:react native头条广告穿山甲广告,腾讯广告优量汇广点通广告集成reactnative RN

- 5_网络字节序_werevj4_

- Angular中的广播消息

- s2c-restful-services:s2c 项目宁静服务 + 存储库

- Gitee上的开源ERP系统源码

- django-countries:一个Django应用程序,提供与表格一起使用的国家/地区选择,标记图标静态文件以及模型的国家/地区字段

- plotly-challenge

- typora笔记工具

- ant_plus_demo:用于测试 ant+ 的 Android 应用