集成电路测试技术:从组合到时序

"集成电路测试技术基础,涵盖了数字逻辑电路测试,包括组合逻辑电路和时序逻辑电路的测试方法,以及扫描通路设计和内置自测试技术。内容还涉及了测试的目的,如故障检测和定位,以及相关的测试设备和故障模型。"

集成电路测试技术是集成电路设计流程中的关键环节,其主要目标是对生产后的集成电路进行故障检测,筛选出不符合规格的次品,并辅助分析生产过程中可能出现的问题。测试在集成电路生产中占据了重要地位,因为它直接影响到产品的质量和可靠性。

测试与验证有显著的区别。验证通常在集成电路设计阶段进行,目的是发现并修正设计错误,而测试则是在芯片制造完成后,针对实际硬件进行的。测试的主要任务是检测由于物理缺陷导致的电路行为异常,即故障。

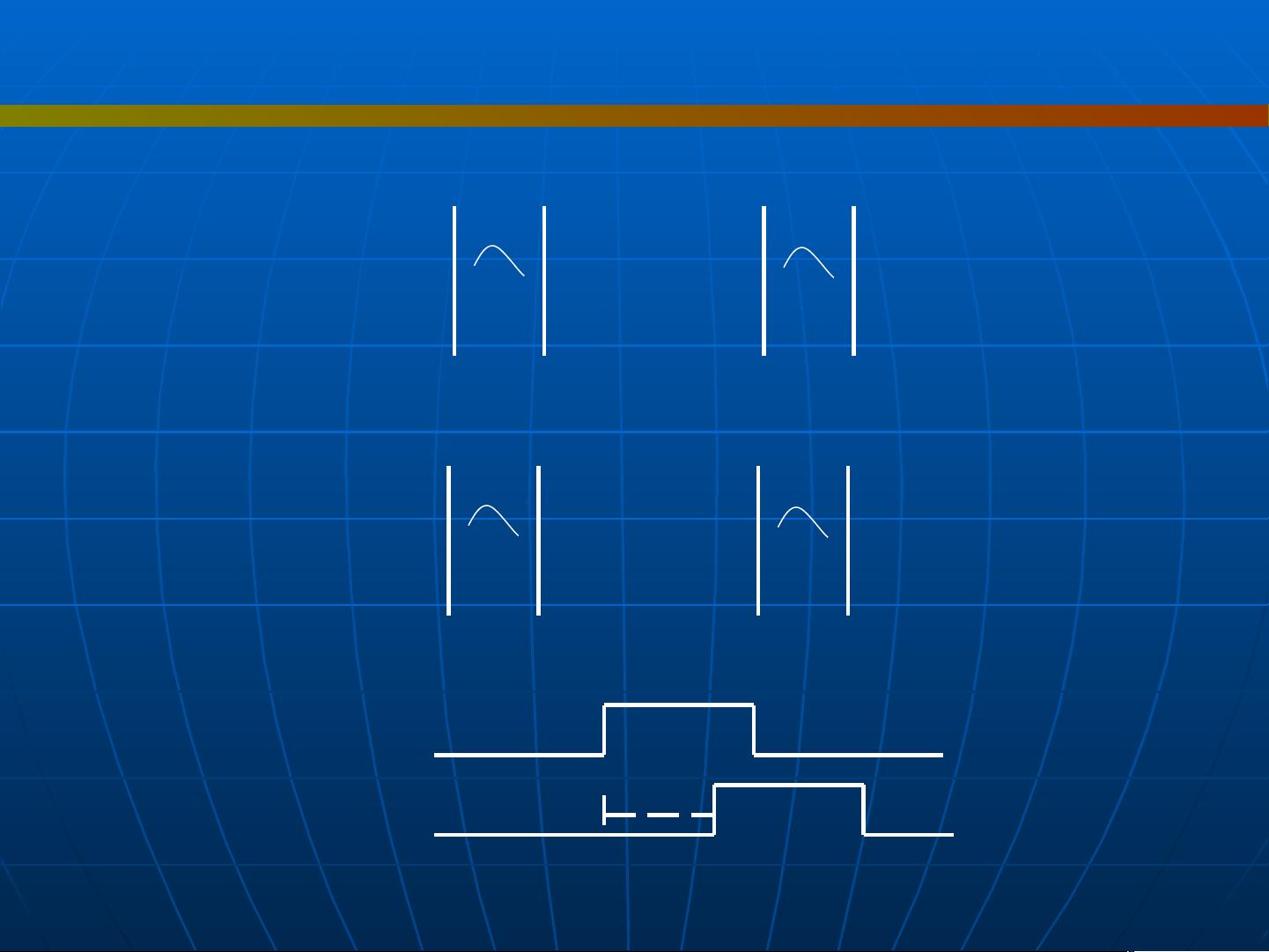

故障模型是理解测试方法的基础。其中,最常见的故障模型是固定型故障模型,包括固定为0故障(stuck-at-0)和固定为1故障(stuck-at-1),即电路中的某个节点始终保持在0或1状态,不随输入变化。此外,还有其他类型的故障,如开路(open fault)和短路(short circuit),以及暂时故障,这些故障可能在特定条件下出现或消失。

对于组合逻辑电路测试,通常采用的方法是通过输入一组测试向量来检查电路的输出是否符合预期。而时序逻辑电路测试则更复杂,因为这类电路包含记忆元素,需要考虑电路的状态转换。扫描通路设计是一种有效的测试手段,通过在设计中加入额外的逻辑,使得测试数据可以被注入到电路内部,简化了时序电路的测试。

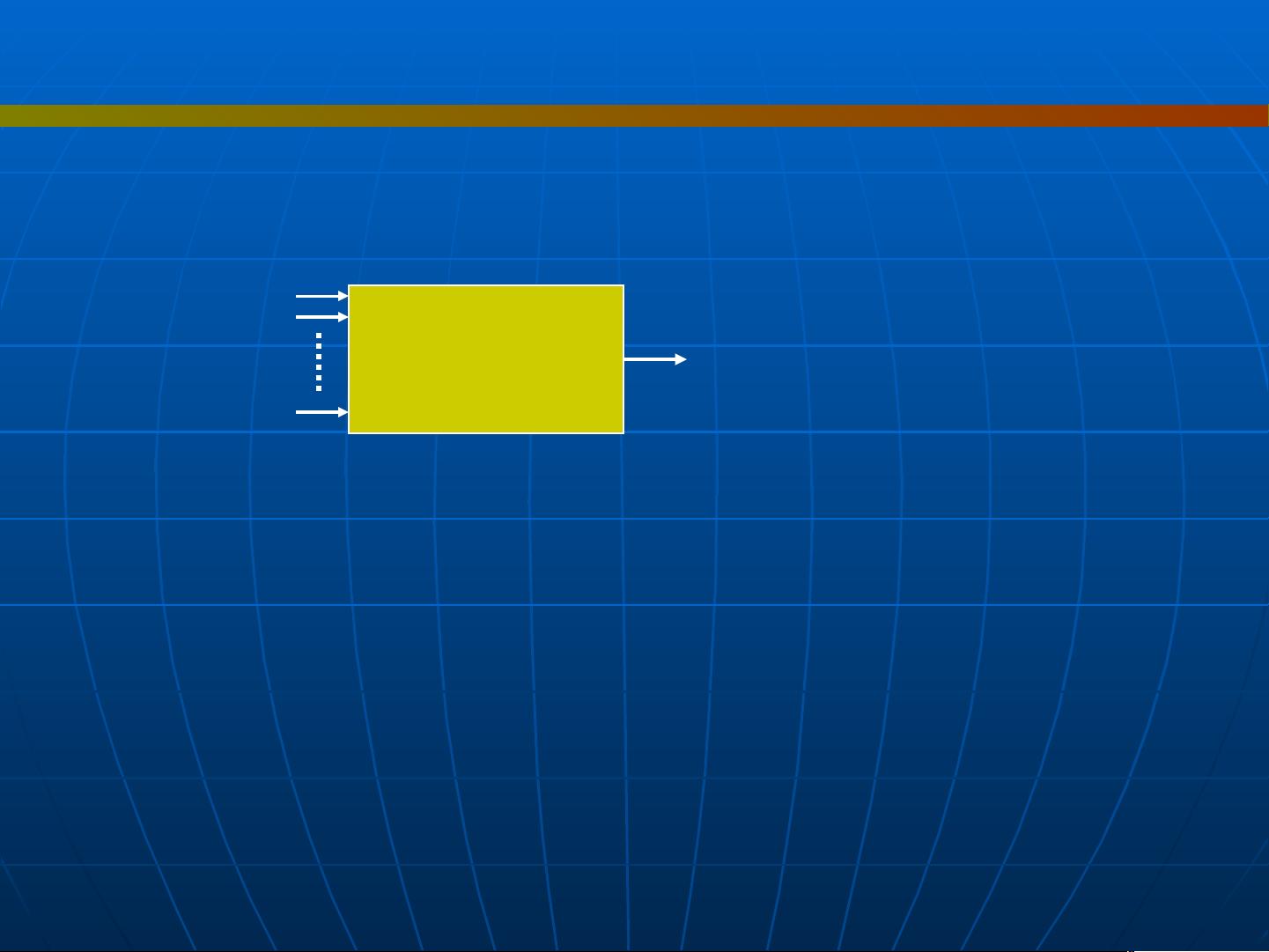

内置自测试(BIST)是近年来发展起来的一种测试技术,它允许电路在运行过程中自我检测。BIST通过集成在芯片内的测试逻辑生成和应用测试向量,减少了对外部测试设备的依赖,提高了测试效率。

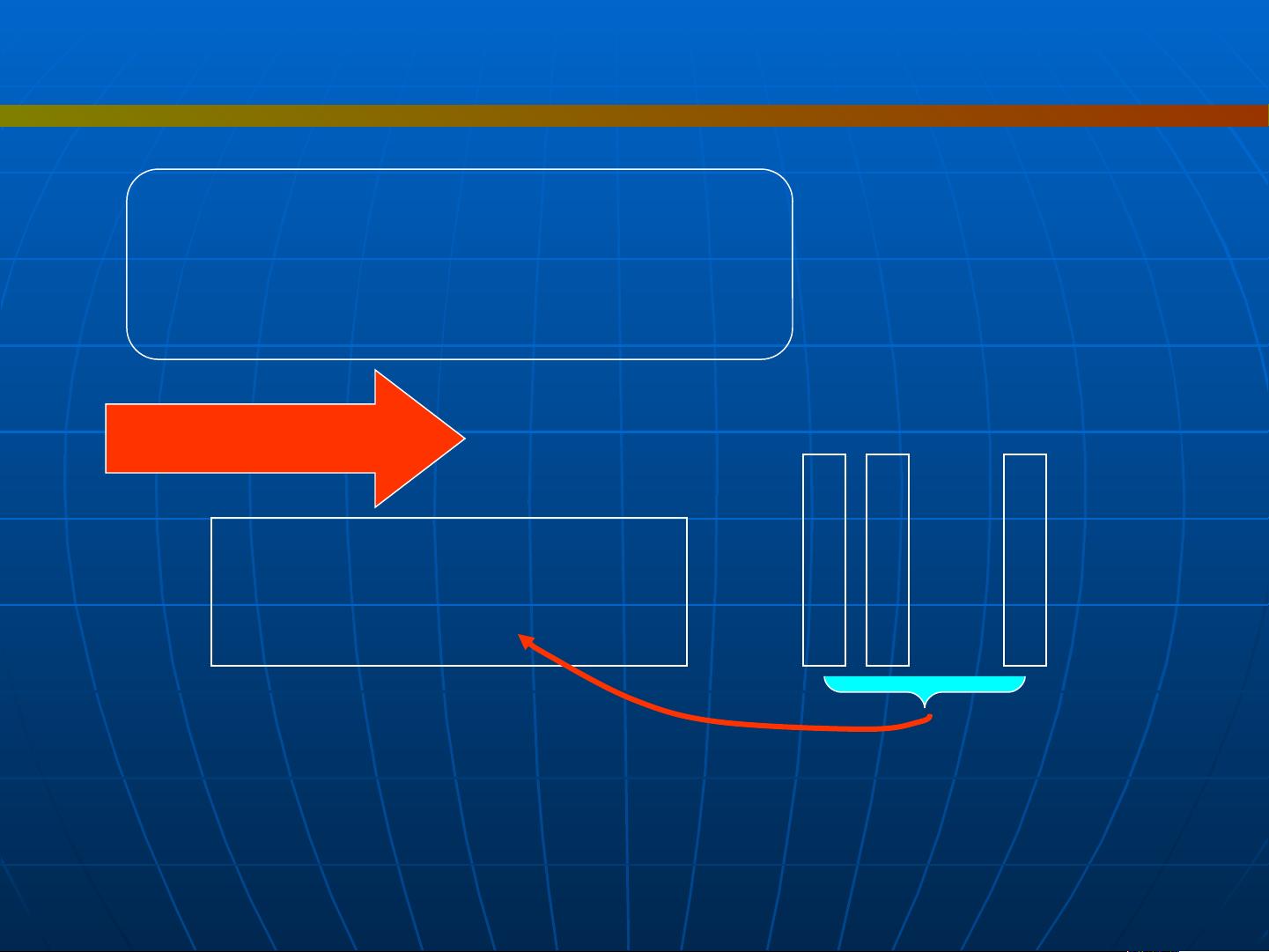

自动测试设备(ATE)是执行集成电路测试的主要工具,它能够生成、应用测试向量,并比较实际响应与期望结果,判断测试是否通过。此外,测试设备还需要配合测试向量生成器和响应压缩机制,以优化测试流程。

集成电路测试技术是确保芯片质量和可靠性的核心手段,涵盖了从故障模型建立、测试结构设计到测试实施的全过程,是集成电路产业不可或缺的一部分。随着集成电路复杂度的增加,测试技术也在不断发展,以应对新的挑战和需求。

708 浏览量

2022-12-17 上传

226 浏览量

629 浏览量

127 浏览量

点击了解资源详情

点击了解资源详情

务实的王编辑

- 粉丝: 1

- 资源: 1

最新资源

- mikamix

- BGInfo(桌面显示IP).zip

- Lausanne_map

- hanu:用于编写Slack机器人的Golang框架

- tcpclient:基于aqueue actor的异步tcpclient

- 与我滚动:在线玩角色扮演游戏的数字工具

- STM32_VL53L1x.zip

- program_for_51.zip_51 舵机程序_51舵机_伺服电机

- 易语言进程冰川名捕

- Orange:该项目包含许多受世界上最受欢迎的电信公司Orange启发的Web组件和脚本

- ist的matlab代码-FBEditor:用于编辑Fritz!Box的配置文件的程序

- tizen-gbs-docker

- xtcp:具有正常关闭,自定义协议的TCP Server框架

- 北京金地中心工程施工组织设计.zip

- 遮罩层特效.zip

- guilhermepontes.github.io:HTML-Página