FPGA驱动的SDRAM文件结构缓存系统:高效数据重组与处理

8 浏览量

更新于2024-08-31

收藏 323KB PDF 举报

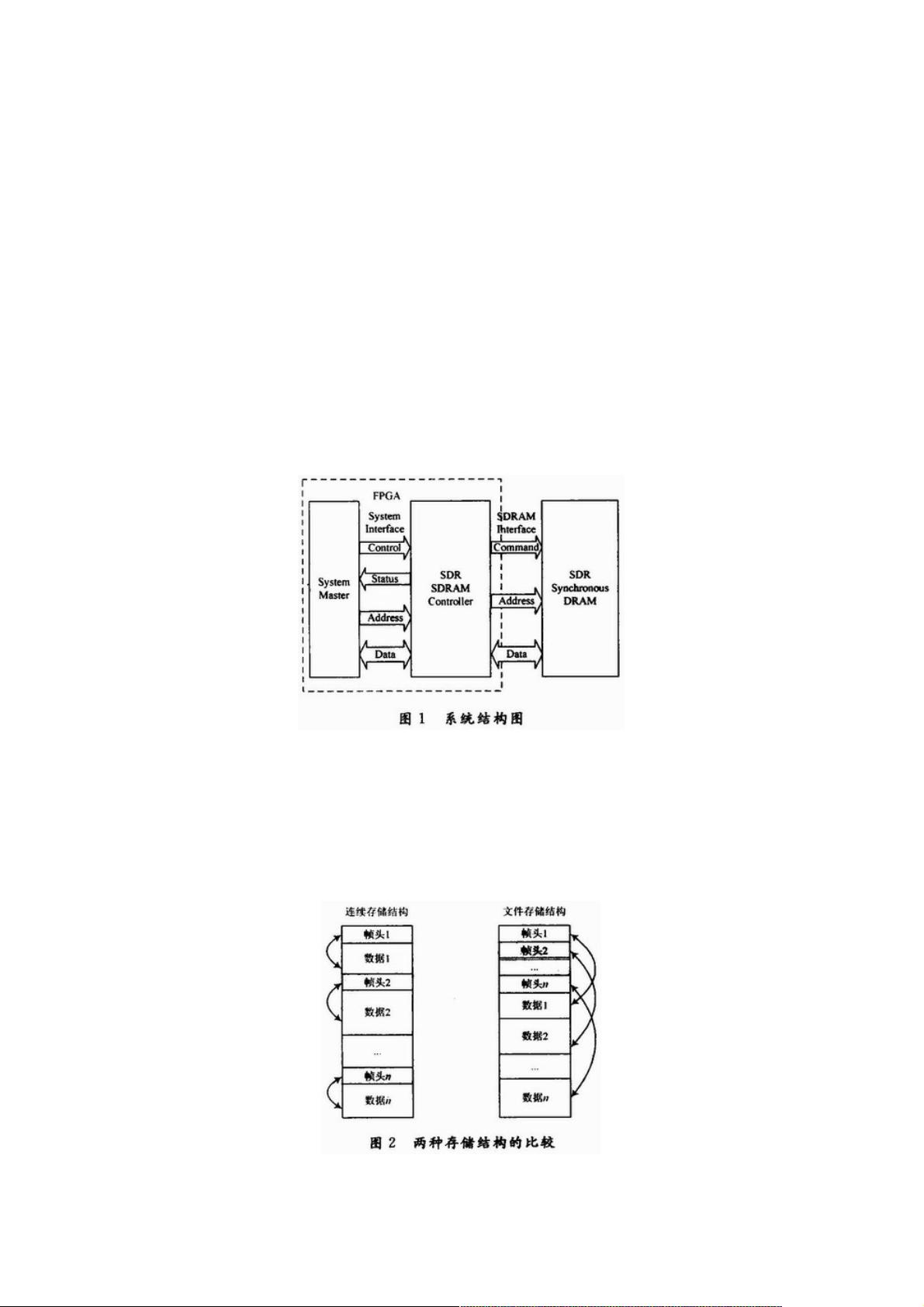

本文主要探讨了基于FPGA的SDRAM文件结构存储控制的实现方法,针对传统连续存储方式在处理多变应用场景中的局限性,提出了创新的数据缓存系统设计。该系统的核心是利用FPGA设计的结构化状态机,它能够实现对SDRAM的高效读写控制,具备数据重组帧的功能。这种新型的文件结构存储方式允许数据按文件的形式存储,帧头与数据分开,每个帧都有明确的首地址,便于后续处理。

系统设计的关键在于FPGA作为核心控制器,通过SystemMaster模块接收高层指令,然后通过SDRAMController模块将这些指令转化为SDRAM的实际读写操作。这样做的优势在于提高了系统的速度、可靠性和灵活性,使得功能扩展变得简单。此外,数据重组帧功能被内置在缓存系统中,大大减轻了后端处理系统的负担,特别是对于那些涉及实时复杂信号处理的应用场景,该系统展现出强大的适应性和效率。

文件结构存储方式使得系统能够在不同信号处理需求下,根据信号特性动态调整数据帧结构,如抽取率和帧长,提供了更大的灵活性。通过这种方式,系统能够支持多种类型的信号并行处理,显著提升了处理性能和系统整体的可移植性。

图1展示了系统的整体架构,清晰地展现了FPGA如何协调各个组件的工作,以及文件结构存储方法在其中的作用。图2则进一步详细解释了这个过程,包括数据读取的流程,从帧头获取地址、偏移地址计算,再到数据读取和帧头更新,确保了数据的准确传输和处理。

总结来说,基于FPGA的SDRAM文件结构存储控制是一种先进的数据缓存解决方案,它不仅解决了传统系统在处理复杂信号时的不足,而且通过优化的硬件设计和文件结构,提升了系统的性能和适应性,为实时信号处理应用提供了理想的平台。

2021-07-13 上传

322 浏览量

210 浏览量

210 浏览量

2022-09-24 上传

414 浏览量

163 浏览量

105 浏览量

2021-07-13 上传

weixin_38631329

- 粉丝: 2

最新资源

- 自动生成CAD模型文件的测试流程

- 掌握JavaScript中的while循环语句

- 宜科高分辨率编码器产品手册解析

- 探索3CDaemon:FTP与TFTP的高效传输解决方案

- 高效文件对比系统:快速定位文件差异

- JavaScript密码生成器的设计与实现

- 比特彗星1.45稳定版发布:低资源占用的BT下载工具

- OpenGL光源与材质实现教程

- Tablesorter 2.0:增强表格用户体验的分页与内容筛选插件

- 设计开发者的色值图谱指南

- UYA-Grupo_8研讨会:在DCU上的培训

- 新唐NUC100芯片下载程序源代码发布

- 厂家惠新版QQ空间访客提取器v1.5发布:轻松获取访客数据

- 《Windows核心编程(第五版)》配套源码解析

- RAIDReconstructor:阵列重组与数据恢复专家

- Amargos项目网站构建与开发指南