Quartus II与VHDL设计:2选1多路选择器实验与组件实例

需积分: 3 81 浏览量

更新于2024-09-17

收藏 444KB DOCX 举报

本篇文档介绍了EDA技术与VHDL语言在潘松、黄继业版教材中的第四章部分实验,主要关注实验4-1和4-2,涉及组合电路设计和VHDL编程实践。实验目标是让学生通过Quartus II工具掌握VHDL文本设计流程,包括设计简单组合电路如2选1多路选择器,以及理解多层次电路设计和仿真测试。

实验4-1的核心内容是设计并实现一个2选1多路选择器,该选择器接受三个输入信号(a、b和s)并根据s的状态选择输出y。实验步骤包括:

1. **VHDL文本设计**:学生需要编写VHDL实体(entity)和结构体(architecture)来定义选择器的功能。实体`muxIS`定义了输入端口a、b和s,以及输出端口y,结构体`oneOFmuxIS`中的进程(process)根据s的值决定y应取a还是b。

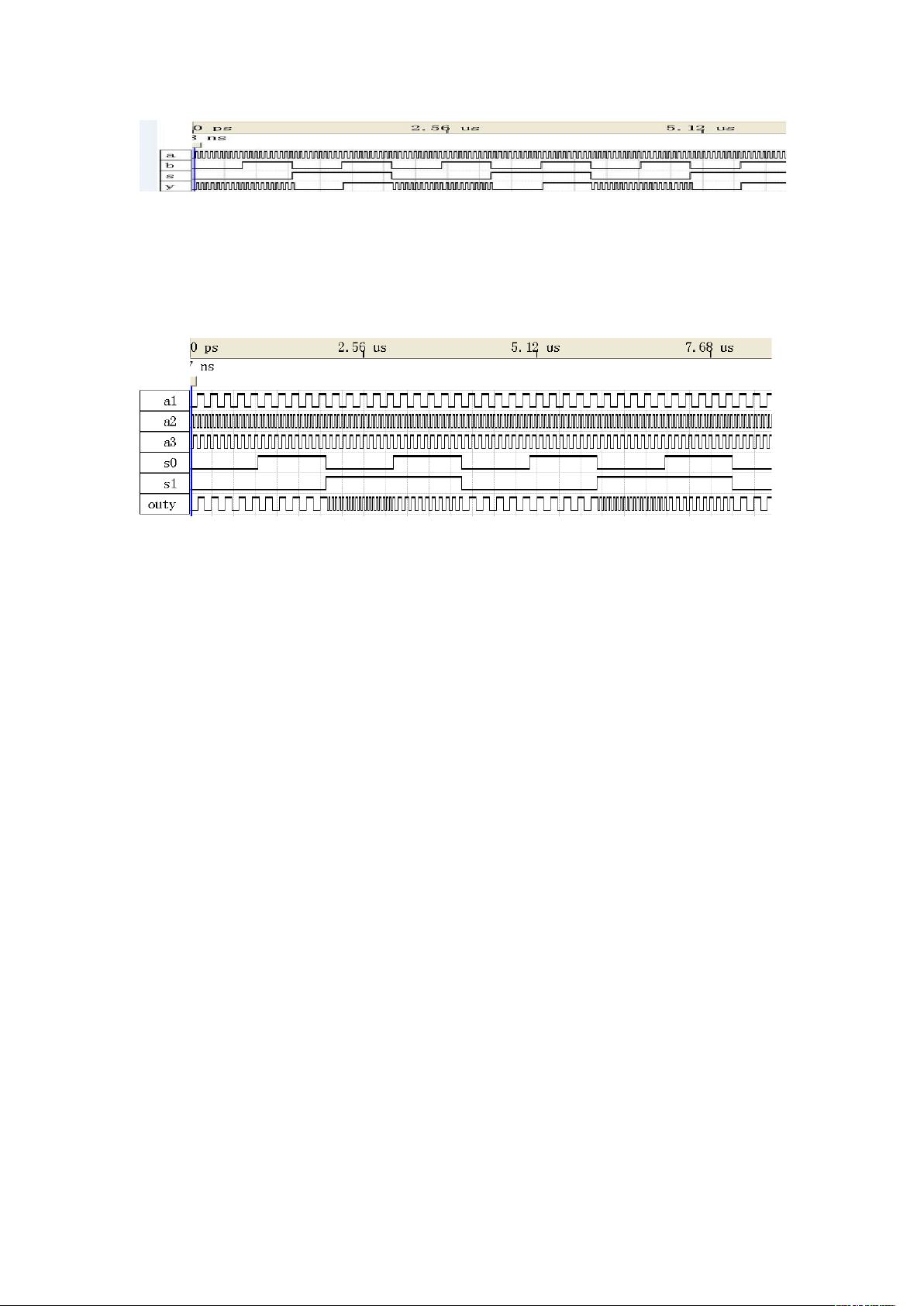

2. **组件例化与连接**:实验指导中提到将多路选择器作为一个元件(component),通过`componentmux`实例化两个组件`u1`和`u2`,并通过`portmap`映射输入和输出,如`u1:muxportmap(a=>a2,b=>a3.,s=>s0,y=>tmp)`。

实验4-2进一步扩展了这个概念,使用更复杂的VHDL语法和信号(signal)来设计一个多输入多输出(MISO)的多路选择器(MUXK)。在这个任务中,学生需编写`ENTITYMUXKIS`和`ARCHITECTUREdoubleOFMUXKIS`,其中包含两个内部处理过程(process)分别处理不同的输入条件,最后输出到`outy`。

在整个过程中,学生不仅锻炼了VHDL编程技能,还学习了如何在Quartus II环境下进行电路设计、仿真和硬件测试,以确保设计的正确性和有效性。通过这些实践,他们能够加深对VHDL语言的理解,以及如何将电路抽象为可复用的模块,以便于构建更复杂的电子系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-12-14 上传

2014-12-10 上传

2013-01-04 上传

2011-04-16 上传

2010-05-18 上传

longtengkd

- 粉丝: 1

- 资源: 1

最新资源

- 深入了解Django框架:Python中的网站开发利器

- Spring Boot集成框架示例:深入理解与实践

- 52pojie.cn捷速OCR文字识别工具实用评测

- Unity实现动态水体涟漪效果教程

- Vue.js项目实践:饭否每日精选日历Web版开发记

- Bootbox:用Bootstrap实现JavaScript对话框新体验

- AlarStudios:Swift开发教程及资源分享

- 《火影忍者》主题新标签页壁纸:每日更新与自定义天气

- 海康视频H5player简易演示教程

- -roll20脚本开发指南:探索roll20-master包-

- Xfce ClassicLooks复古主题更新,统一Linux/FreeBSD外观

- 自建物理引擎学习刚体动力学模拟

- Python小波变换工具包pywt的使用与实例

- 批发网导航程序:自定义模板与分类标签

- 创建交互式钢琴键效果的JavaScript库

- AndroidSunat应用开发技术栈及推介会议