基于QuartusII的多功能数字时钟设计

"eda数字时钟"

EDA(Electronic Design Automation)数字时钟是一种利用电子设计自动化工具,如Altera公司的Quartus II软件,来设计和实现的多功能电子设备。这个项目旨在让学生理解并实践数字时钟的基本功能,包括时钟显示、闹钟设置和万年历等特性。通过这个课程设计,学生可以深入学习数字系统的设计原理和VHDL编程语言。

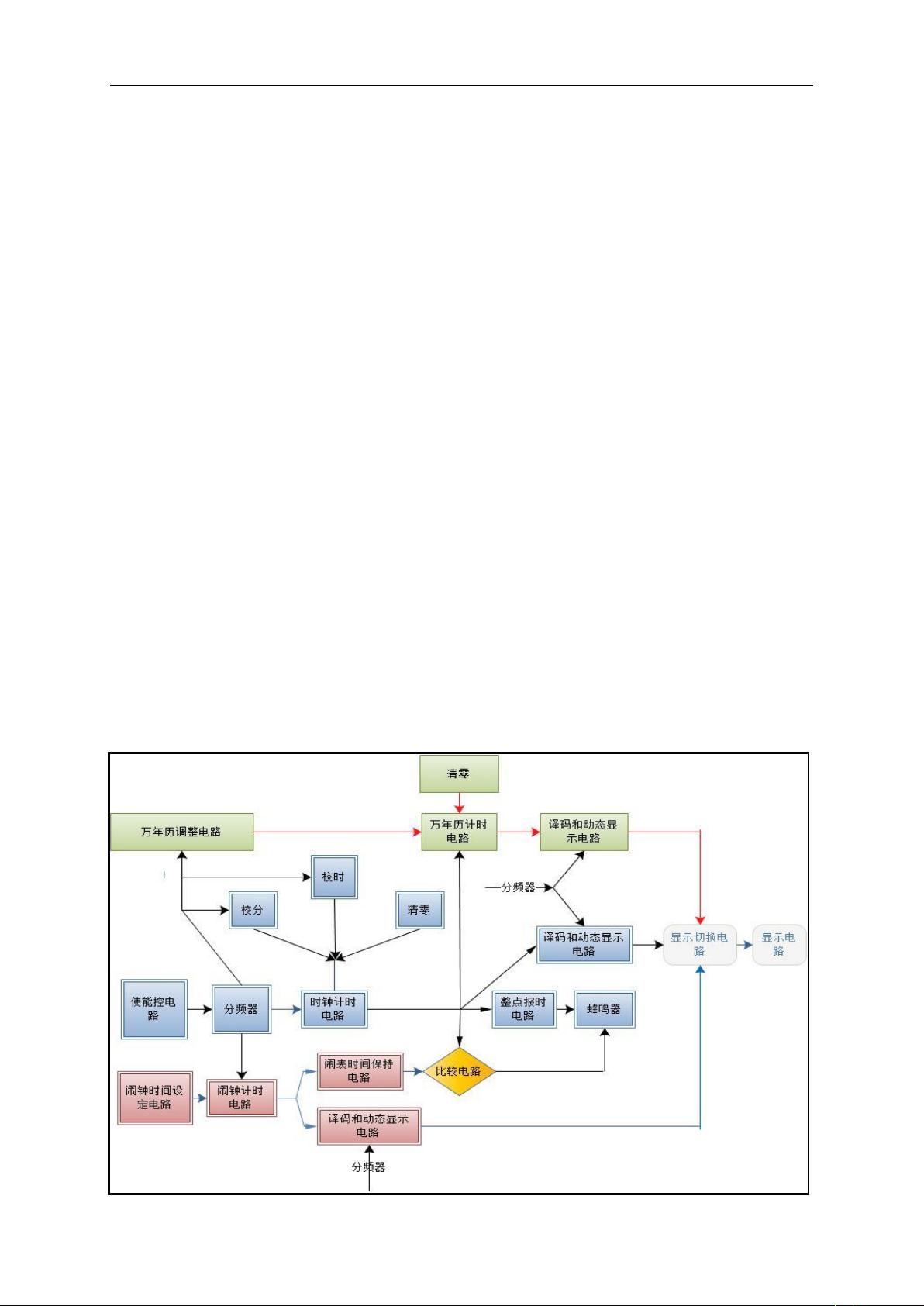

在设计过程中,采用了层次化设计方法,即将复杂系统分解为多个独立的模块,每个模块都有明确的功能,便于管理和扩展。例如,设计包含了三个主要部分:

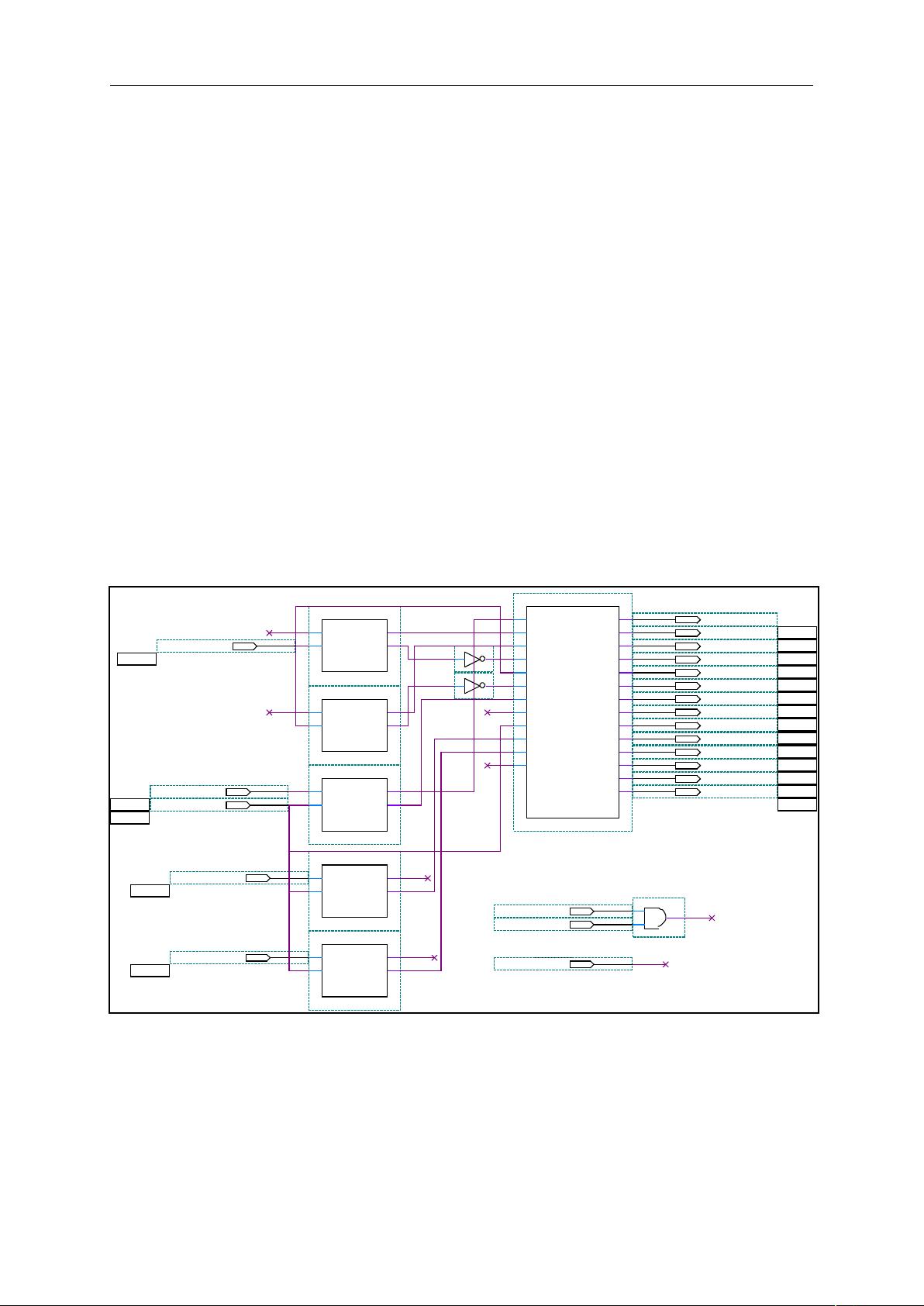

1. 时钟基本功能电路:这部分主要包括模60和模24计数器,用于计算分钟和小时;动态显示控制电路,用于驱动LED或LCD显示时间;分频器生成1Hz的脉冲进行计时,并通过整点报时电路控制蜂鸣器在整点时发出声音。计数器级联采用了内部同步、外部异步的方式,通过巧妙的逻辑设计,实现了同步效果且提高了可靠性。此外,为了节省硬件资源,使用了VHDL编写的24选4数据选择器实现动态显示控制。

2. 闹钟电路:这一部分同样基于模60和模24计数器,但增加了定时和存储功能,允许用户设定特定的闹钟时间。显示控制电路更新闹钟时间,而14-7同或门配合后续的与门电路用于在设定的闹钟时间触发蜂鸣器,提醒用户。

3. 万年历电路:设计中使用了模100、模12和模30的计数器,以处理年、月、日的计数。动态显示电路再次被调用来显示日期。考虑到实际应用中的空间和成本限制,设计者采用了两种复用技术,使得有限的输入和输出可以满足多种功能的需求。

关键词涉及到的“同步整点报时”指的是在每个小时的整点时刻,时钟能够自动发出提示音。而“闹钟”功能则允许用户设置一个特定的时间,到达设定时间时会发出警报。万年历功能则意味着时钟可以准确地显示当前的日期,包括年、月、日,甚至可能包括星期。VHDL语言是实现这些功能的关键,它是一种硬件描述语言,用于编写和仿真数字系统的逻辑。

EDA数字时钟项目是一个综合性的实践教学案例,涵盖了数字逻辑设计、计数器原理、显示技术、时序控制以及VHDL编程等多个方面的知识,对电子信息科学与技术专业的学生来说,这是一个很好的理论与实践相结合的学习机会。

273 浏览量

146 浏览量

181 浏览量

142 浏览量

306 浏览量

462 浏览量

279 浏览量

西越

- 粉丝: 3

- 资源: 7

最新资源

- 在基于WCF的应用程序中处理SOAP异常

- 《这辈子只能这样吗?》读书笔记ppt模板.rar

- 绿色清新水彩手绘叶子背景图片PPT模板

- java源码查看-MyAnimeViewer:适用于Android的免费和开源动漫查看器

- 《给你一点“绿”》——自然春意ppt模板.rar

- 生态能源科技公司网页模板

- THM_Write-Ups:这是TryHackMe Room文章的存储库

- 三张彩色水彩背景图片PPT模板

- 《没事别随便思考人生》读书笔记ppt模板.rar

- 两张蓝橙放射状科技背景图片PPT模板

- 蓝色IT科技教育网页模板

- 国家

- teev:基于libdvbtee构建的基于QT的电视观看应用程序

- artsiukhou.github.io

- 《愿有人陪你颠沛流离》读书笔记ppt模板.rar

- 该论文-论文.zip