MCS@-51 ARCHITECTURAL OVERVIEW

The bits RSOand RSl are wed to select one of the four

register banks shown in Figure 7. A number of instruc-

tions refer to these RAM locations as RO through R7.

The selection of which of the four banks is being re-

ferred to is made on the basis of the bits RSOand RS1

at execution time.

The Parity bit reflects the number of 1s in the Accumu-

lator P = 1 if the Accumulator contains an odd num-

ber of 1s, and P = O if the Accumulator contains an

even number of 1s. Thus

thenumber of 1s in the Accu-

mulator plus P is always even.

Two bits in the PSW are uncommitted and maybe used

as general purpose status flags.

Addressing Modes

The

addressing modes in the MCS-51 instruction set

are as follows

DIRECT ADDRESSING

In direct addressing the operand is specitied by an 8-bit

addreas field in the instruction. Only internal Data

RAM and SFRS can be directly addressed.

INDIRECT ADDRESSING

In indirect addressing the instruction specifies a register

which contains the address of the operand. Both inter-

nal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be RO or

RI of the selected register bank, or the Stack Pointer.

The addreas register for id-bit addresses can only be the

id-bit “data pointer” register, DPTR.

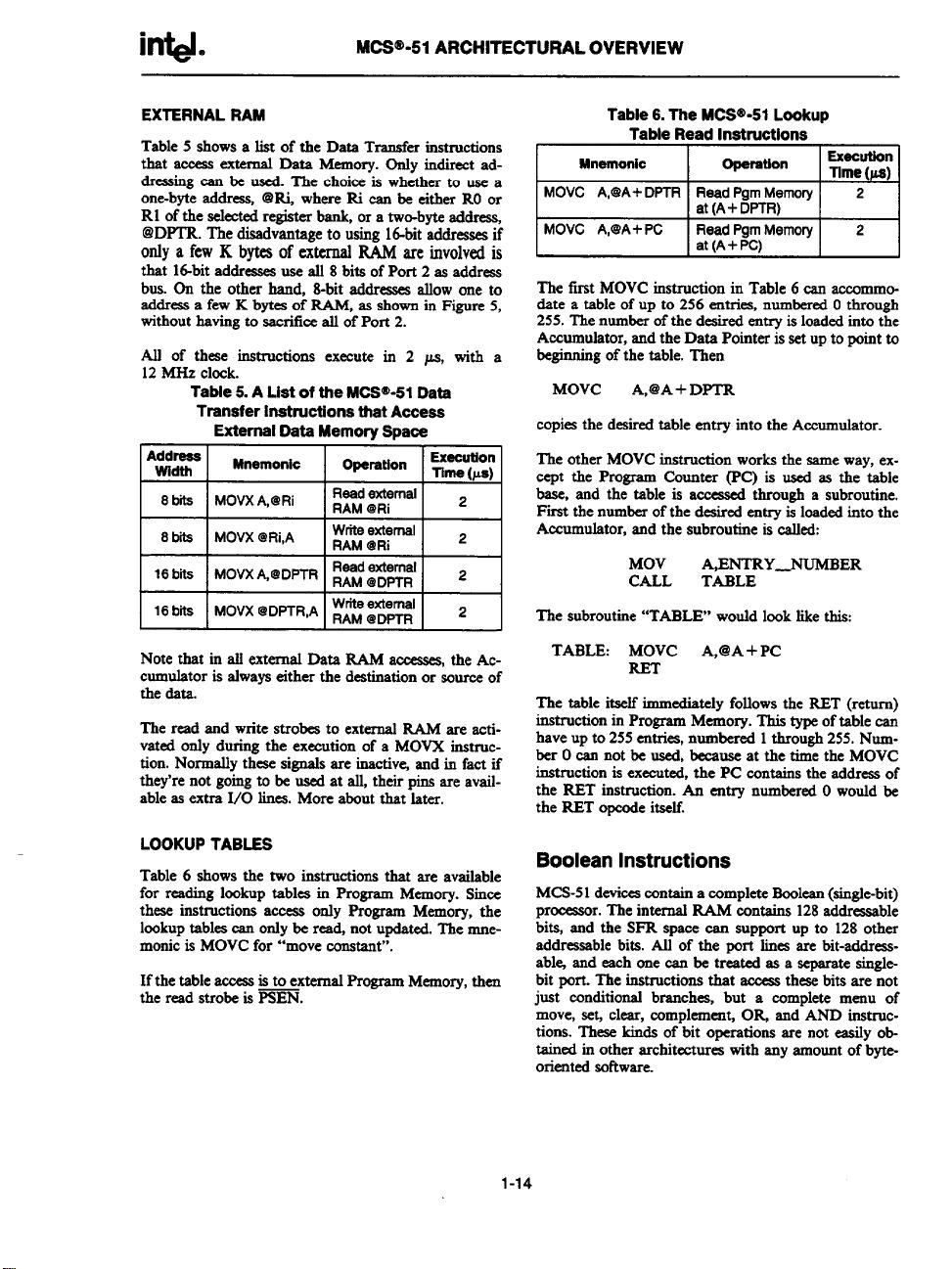

REGISTER INSTRUCTIONS

The

register banks, containing registers ROthrough R7,

can be accemed by certain instructions which carry a

3-bit register specification within the opcode of the in-

struction. Instructions that access the registers this way

are code efficient, since this mode elirninatez an addreas

byte. When the instruction is executedj one of the eight

registers in the selected bank is amessed. One of four

banks is selected at execution time by the two bank

select bits in the PSW.

REGISTER-SPECIFIC INSTRUCTIONS

Some instructions are specific to a certain register. For

example, some instructions always operate on the Ac-

cumulator, or Data Pointer, etc., so no address byte is

needed to point to it. The opcode itself does

that.In-

structions that refer to the Accurrdator as A assemble

as accumulator-specific opcmdes.

IMMEDIATE CONSTANTS

The value of

a constant can follow the opcode in Pro-

gram Memory. For example,

MOV A, # 100

loads the Accumulator with the decimal number 100.

The same number could be specified in hex digitz as

64H.

INDEXED ADDRESSING

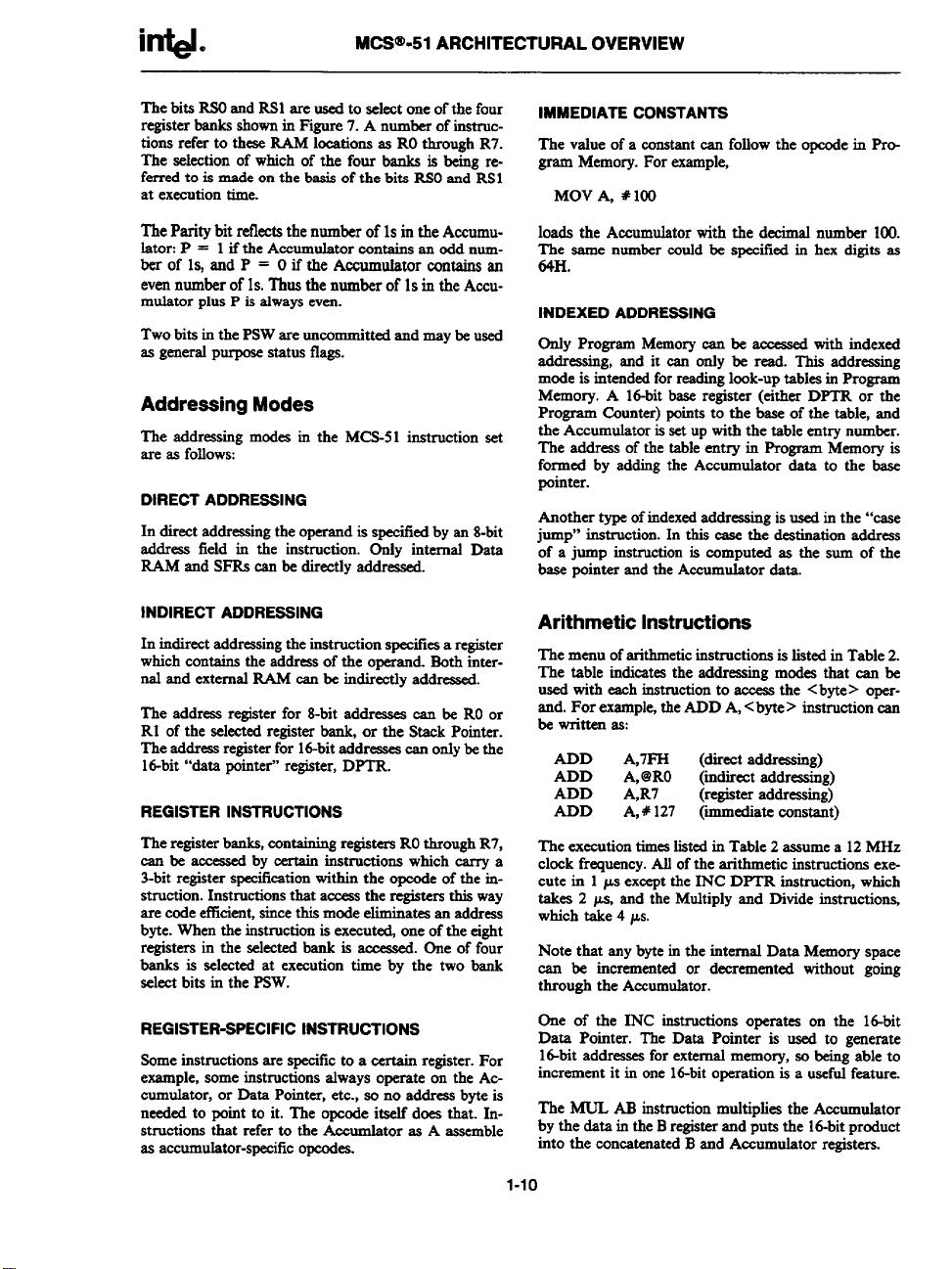

only

Program Memory can be amessed with indexed

addressing, and it can only be read. This addressing

mode is intended for reading look-up tables in Program

Memory. A Id-bit base register (either DPTR or the

Program Counter) points to the base of the table, and

the Accumulator is setup with the table entry number.

The address of the table entry in Program Memory is

formed by adding the Accumulator data to the base

pointer.

Another type of indexed addreaaing is used in the “case

jump” instruction. In this case the destination address

of a jump instruction is computed as the sum of the

base pointer and the Accumulator &ta.

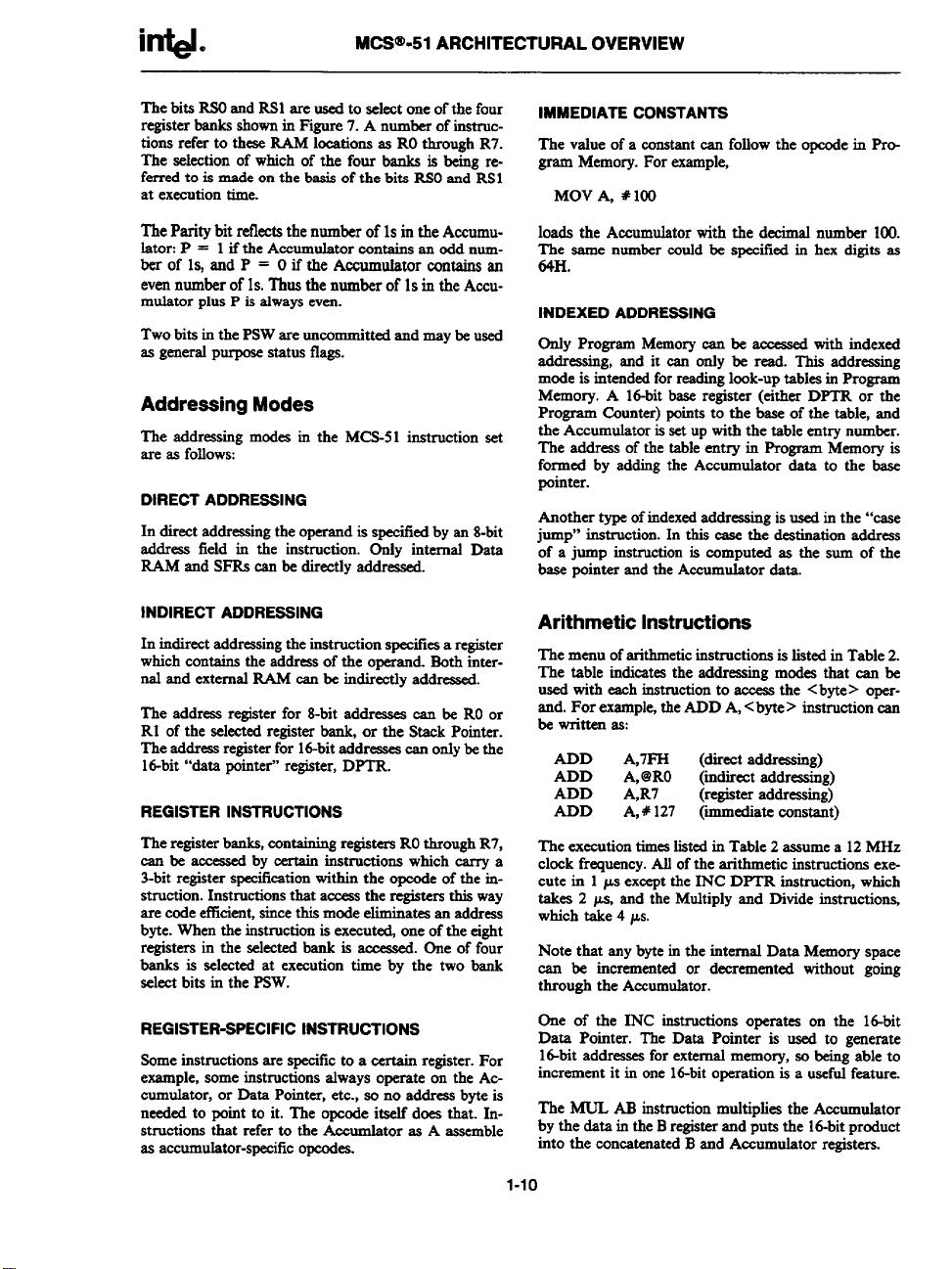

Arithmetic Instructions

The

menu of arithmetic instructions is listed in Table 2.

The table indicates the addressing modes that can be

used with each instruction to access the <byte> oper-

and. For example, the ADD A, <byte> instruction can

be written as

ADD A,7FH

(directaddressing)

ADD A,@RO (indirect addressing)

ADD A,R7 (register addressing)

ADD A,# 127 (iediate constant)

The execution times listed in Table 2 assume a 12 MHz

clock frequency. All of the arithmetic instructions exe-

cute in 1 ps except the INC DPTR instruction, which

takes 2 W, snd the Multiply and Divide instructions,

which take 4 ps.

Note that any byte in the internal Data Memory space

can be incremented or decremented without going

through the Accumulator.

One of the INC instructions operates on the Id-bit

Data Pointer. The Data Pointer is used to generate

16-bit addresses for external memory, w being able to

increment it in one 16-bit operation is a usefirl feature.

The MUL AB instruction multiplies the Accumulator

by the data in the B register and puts the Id-bit product

into the concatenated B and Accumulator registers.

1-1o