2022 IEEE国际固态电路会议特刊:超低相位噪声X带BiCMOS VCO与数字PLL

需积分: 12 132 浏览量

更新于2024-06-28

收藏 157.52MB PDF 举报

"JSSC 2022.12 - IEEE Journal of Solid-State Circuits"

这篇文章摘录自《IEEE Journal of Solid-State Circuits》(JSSC)2022年12月刊,这是一本专注于固态电路领域的权威学术期刊。JSSC是固态电路和系统设计领域的顶级出版物,它涵盖了微电子学、集成电路设计以及相关技术的最新研究和进展。

编辑部在本期新增了两位副编辑,分别是D. Sylvester,他们的介绍位于3507页和3508页。这表明JSSC在不断更新其编辑团队,以保持与该领域发展的同步,确保发表的论文具有最高水平的科学严谨性和专业性。

特别关注的是,本期还包含了一个关于2022年IEEE国际固态电路会议(ISSCC)的特辑。ISSCC是固态电路领域的旗舰会议,聚集了全球顶尖的研究成果,对推动该领域的发展起着至关重要的作用。W. Wu, H. Ito, J. Anders, A. Ali, 和 G. Pillonnet共同撰写的客座编辑序言位于3509页,为读者介绍了这个特辑的背景和价值。

此外,本期还发表了多篇技术论文,涉及先进的电路设计:

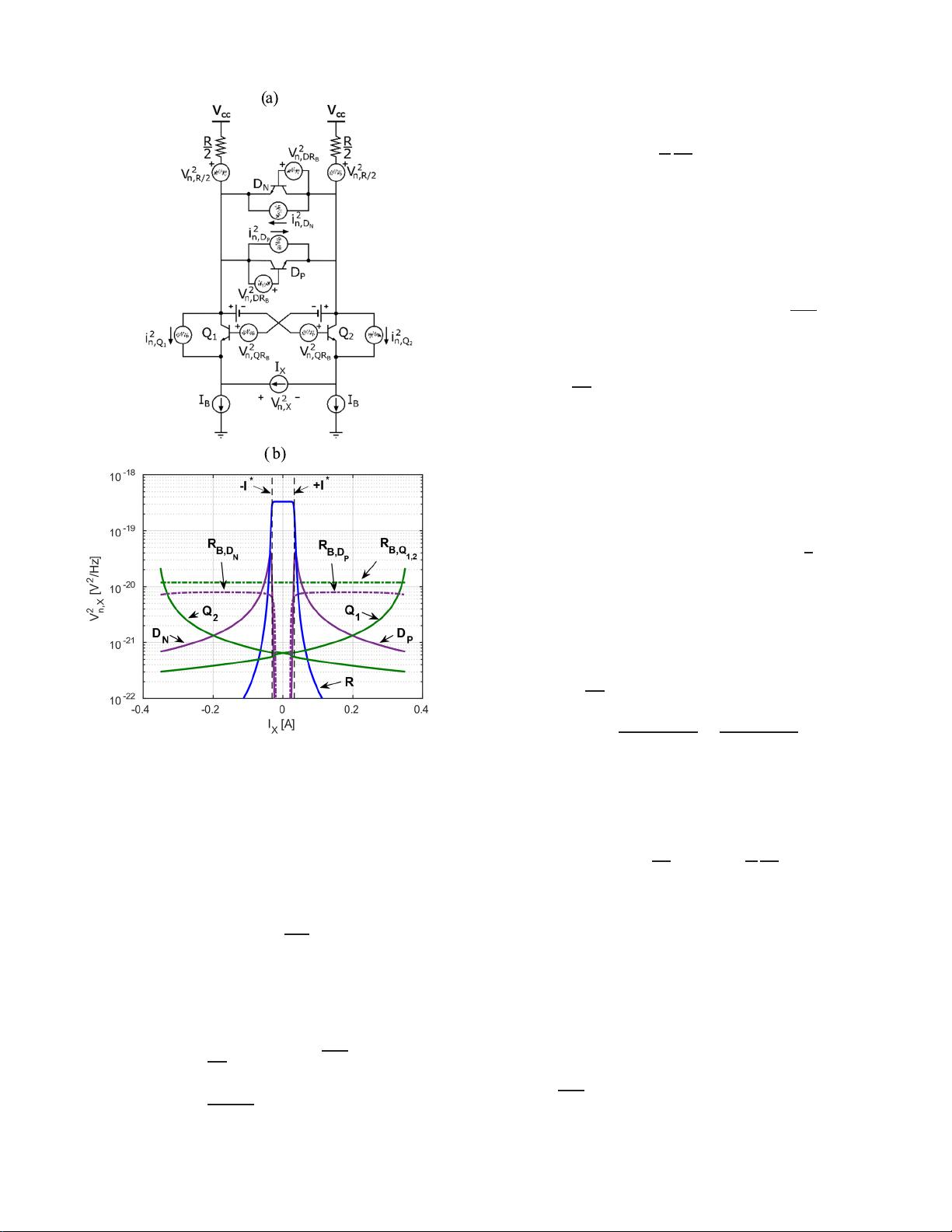

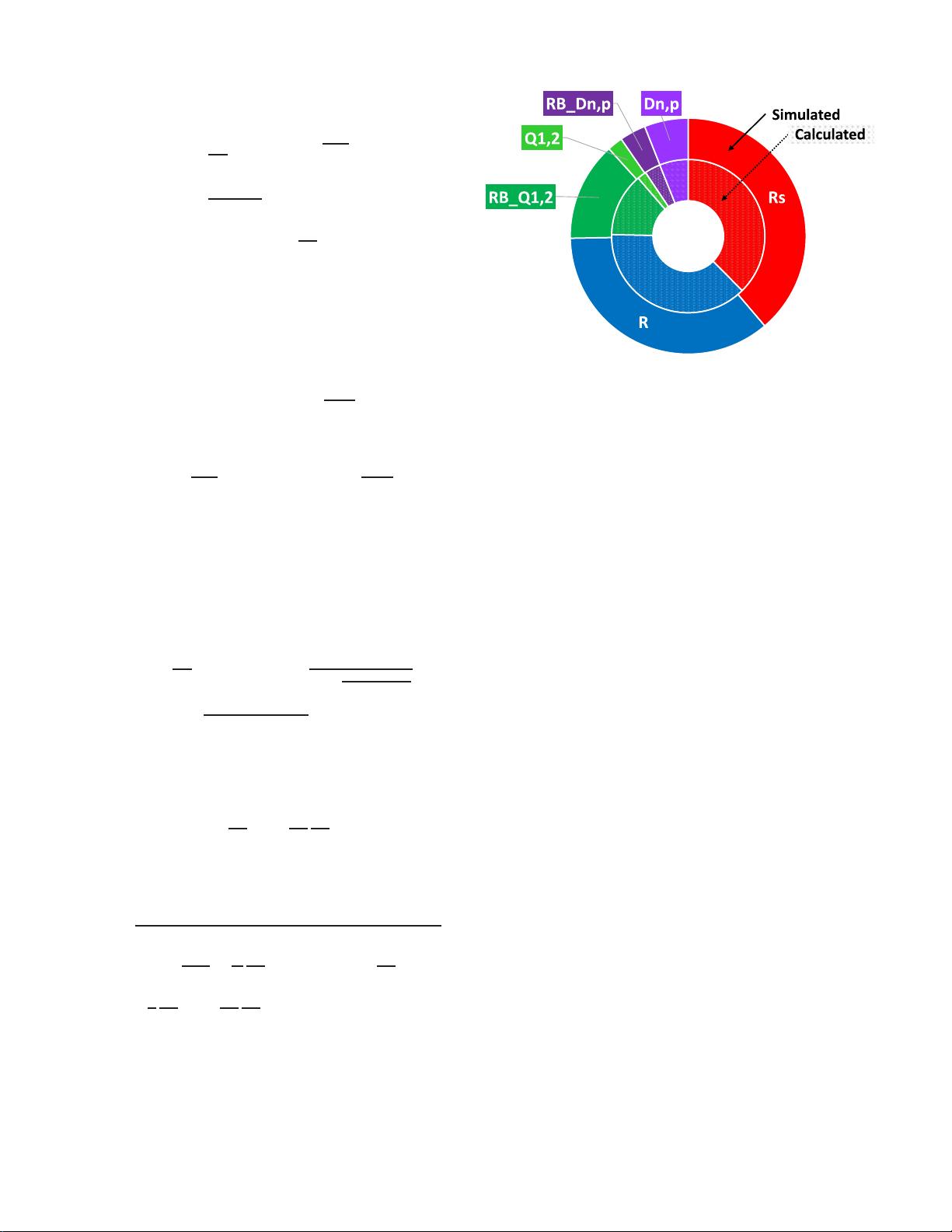

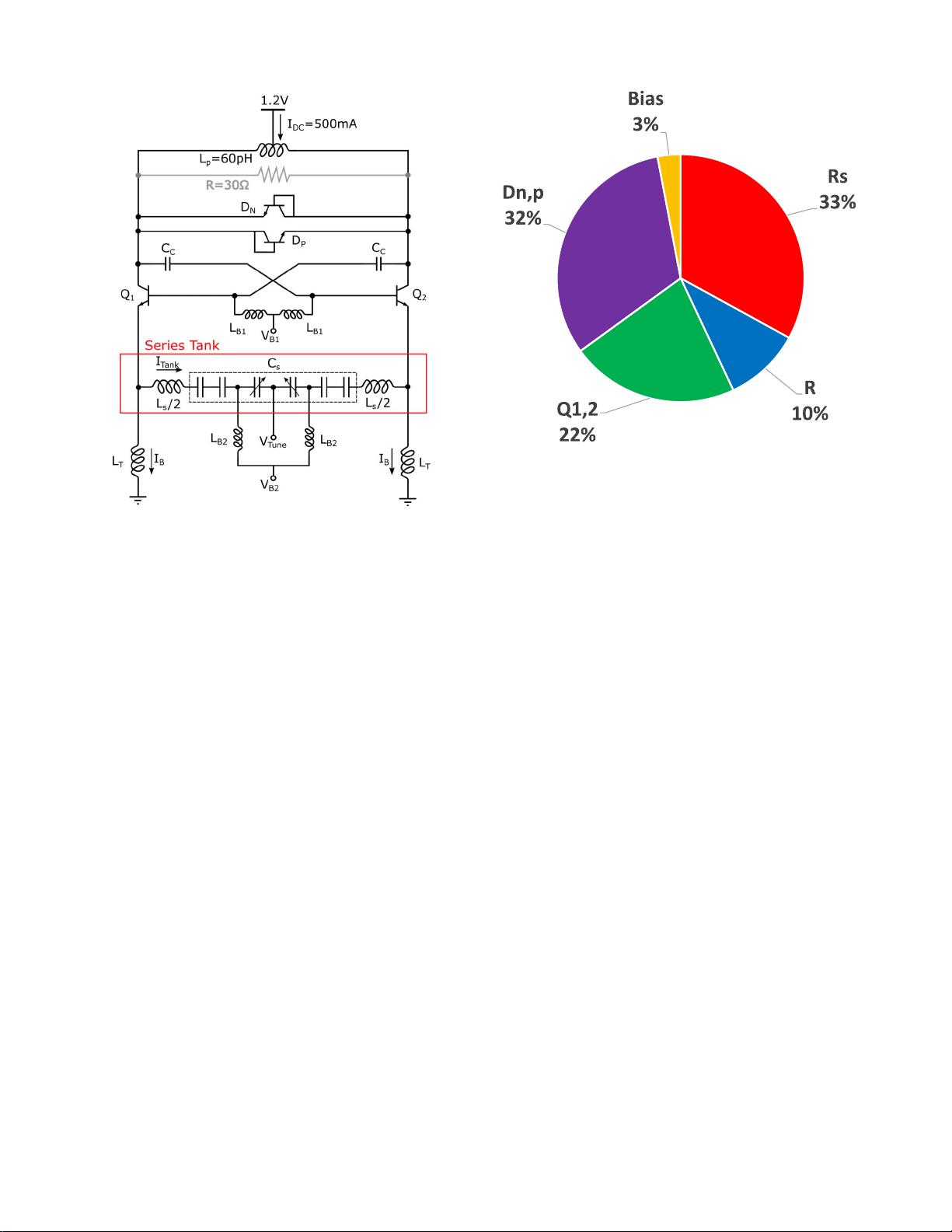

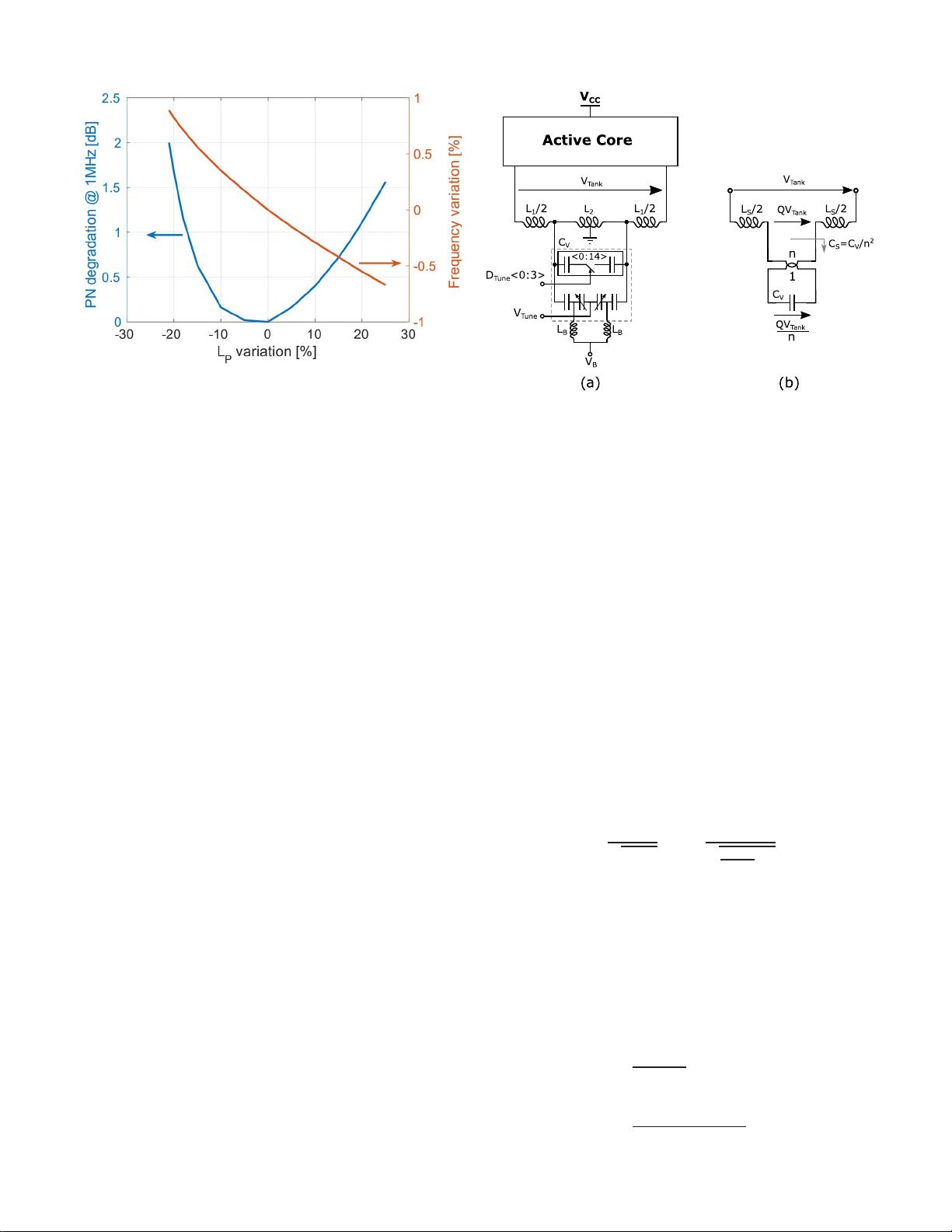

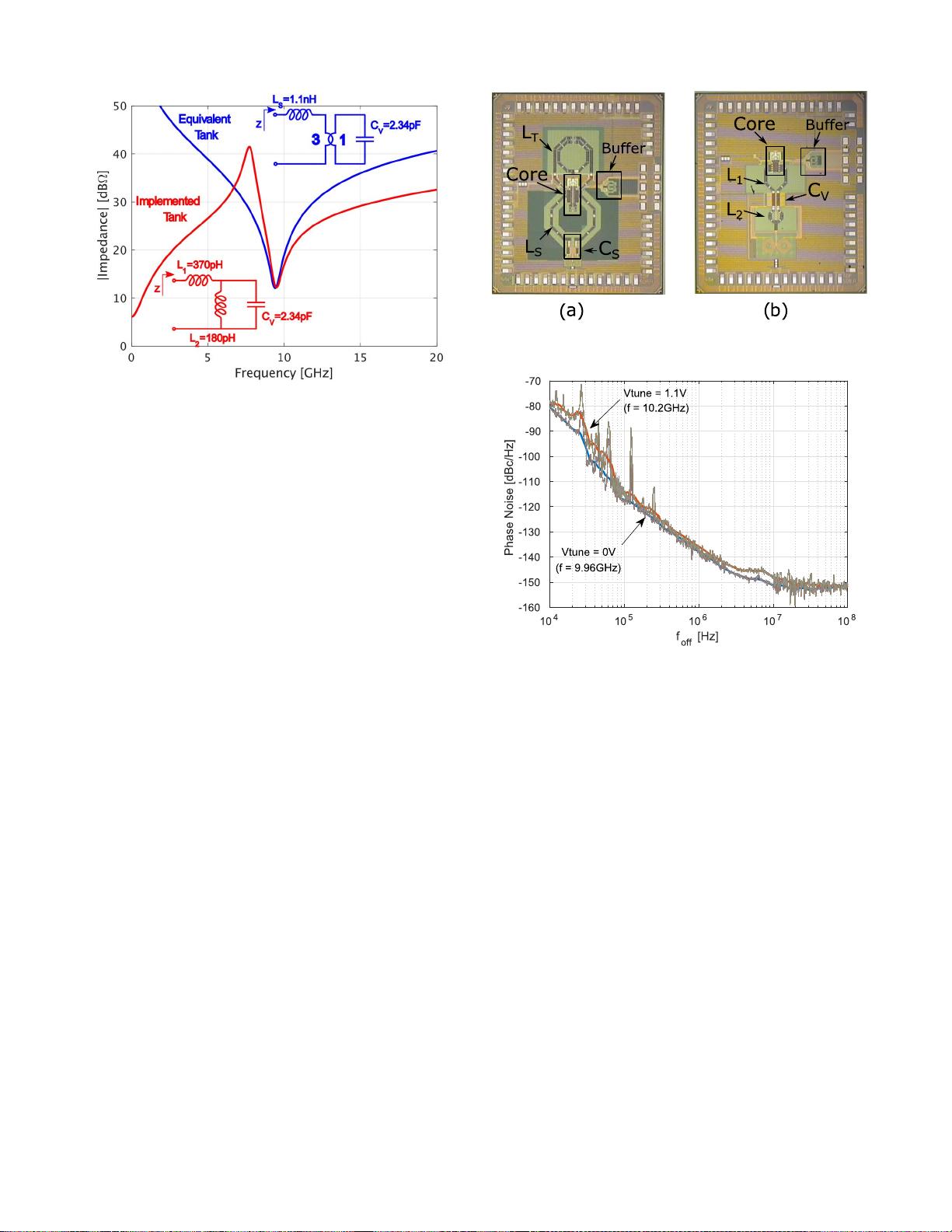

1. "Ultra-Low Phase Noise X-Band BiCMOS VCOs Leveraging the Series Resonance":Franceschin, Riccardi 和 Mazzanti的这篇论文详细探讨了利用串联谐振实现超低相位噪声的X波段双极型互补金属氧化物半导体(BiCMOS)压控振荡器(VCO)。VCO是射频和通信系统中的核心组件,其相位噪声性能直接影响系统的整体性能。

2. "A Low-Jitter Ring-DCO-Based Fractional-N Digital PLL With a 1/8 DTC-Range-Reduction Technique Using a Quadruple-Timing-Margin Phase Selector":由Park, Hwang, Seong 和 Choi提交的这篇论文介绍了采用四倍时钟裕量相位选择器的低抖动环形压控振荡器(Ring-DCO)为基础的分数-N数字锁相环(PLL),并提出了一种降低分频计数器(DTC)范围的技术,旨在优化频率合成和减少时钟抖动。

3. "A Fractional-N Bang-Bang PLL Based on Type-II Gear Shifting and Adaptive Frequency Switching Achieving 68.6 fs-rms Total-Integrated-Jitter and 1.56μs-Locking-Time":Dartizio等人展示了一种基于Type-II齿轮切换和自适应频率切换的分数-N开关电荷泵(Bang-Bang PLL)设计,实现了极低的总集成抖动和快速的锁定时间,这对于高速数据传输和通信系统至关重要。

4. "A Harmonic-Mixing PLL Architecture":最后,还有一篇关于谐波混合锁相环架构的论文,这类架构通常用于提高频率转换效率和线性度,对于现代无线通信和射频系统的设计至关重要。

JSSC 2022.12期揭示了固态电路领域的最新创新,包括高级振荡器设计、低抖动PLL技术以及谐波混合方法,这些都是推动未来电子设备小型化、高效化和高性能化的重要研究方向。

2021-12-26 上传

2022-12-14 上传

2022-12-14 上传

125 浏览量

2022-12-14 上传

2022-12-14 上传

2022-12-14 上传

2022-12-14 上传

netshell

- 粉丝: 11

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例