PCIe原理解析:从并行到串行的演变与体系架构详解

PCI Express (PCIe) 是一种高性能的I/O串行总线标准,它的发展经历了几个关键阶段。从最早的并行接口如ISA、EISA、Micro Channel (MC) 和 VESA,这些早期的总线系统主要用于连接处理器和周边设备,数据传输速度有限且受限于处理器类型。

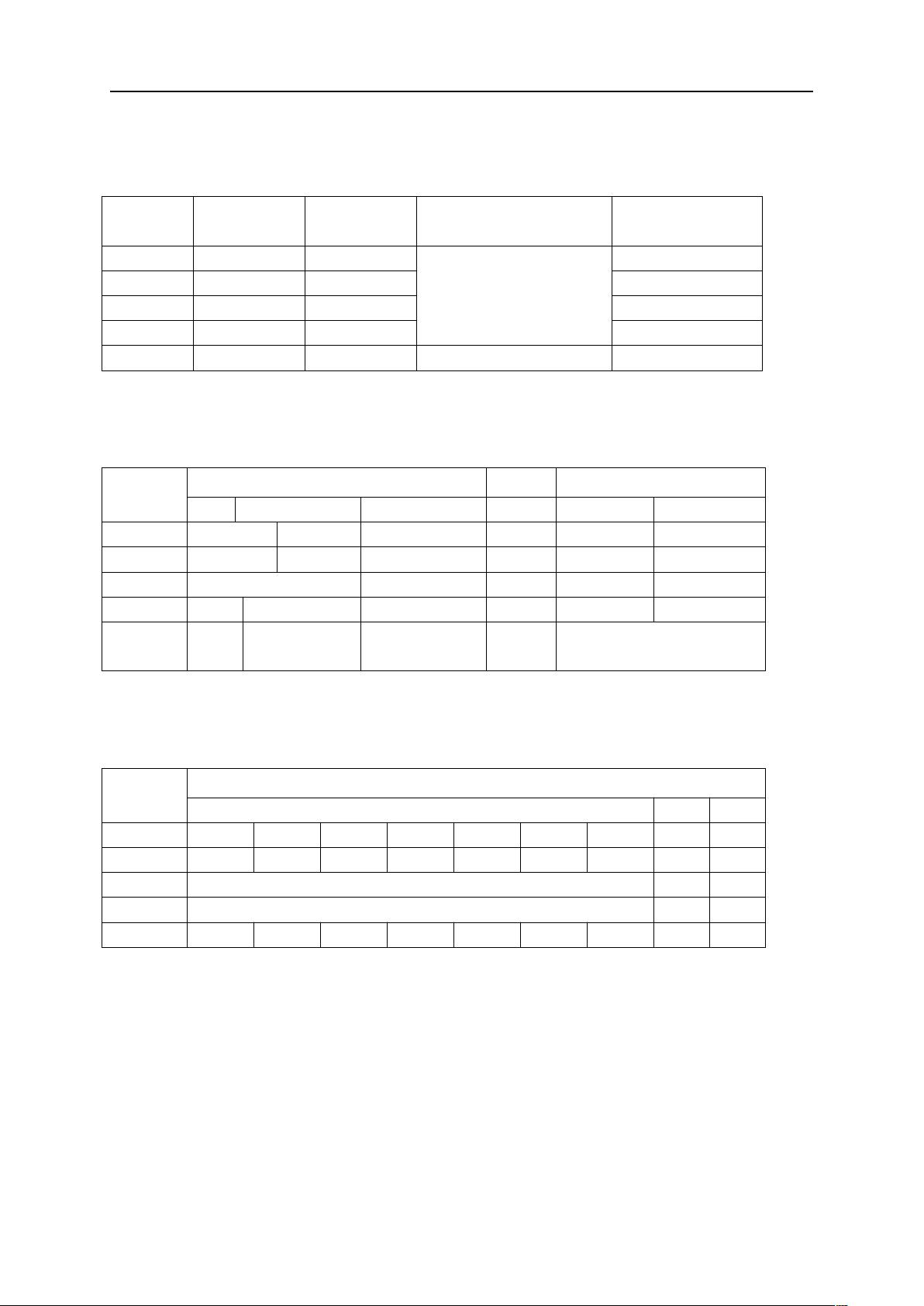

第一代并行总线如ISA(1984年推出,16位数据宽度,5MBps速率)和EISA(1989年,32位宽,33MBps),它们的性能逐渐提升但依然存在带宽瓶颈。EISA是第一个尝试提高总线性能的局部总线,而MC则进一步加强了这一方向,但作为微通道总线,它并不是独立的接口标准。

第二代并行总线PCI(1992年推出)引入了32位宽、133MBps的数据速率,随后的AGP(1993年)和PCI-X(1995年)分别提升了数据宽度至64位,并引入了更高的频率,以支持图形处理需求,特别是PCI-X的不同版本提供不同的带宽选项。这些接口主要依赖于共享总线结构,即下挂式总线,总线带宽由连接的多个设备共享。

PCIe则是对这一传统模式的根本变革。从第三代开始,PCIe转向了串行通信,消除了并行总线的多条数据、地址和控制线,转而采用点对点的连接方式,每条链路可以包含一条或多条通路,每个设备拥有独享的带宽。这种设计显著提高了带宽效率,同时保持了向后兼容,支持原有的地址空间和配置机制。

PCIe 1.x、2.0的推出分别标志着接口性能的提升,数据宽度扩展至1路、2路甚至4路,带宽也随之提升。与传统的PCI相比,PCIe通过PLL技术实现更高的频率和更好的性能,增加了额外的属性,使得数据传输更为灵活和高效。

PCIe的出现不仅改变了计算机系统的内部架构,而且推动了现代计算机硬件的高速连接和扩展,广泛应用于显卡、硬盘控制器、网卡等高速接口,对于提高系统整体性能和效率起到了关键作用。随着技术的进步,PCIe的后续版本还在不断演进,以满足不断增长的计算需求。

相关推荐

1575 浏览量

qq_24205049

- 粉丝: 0

最新资源

- finquick:利用Web应用实现gnucash财务数据实时访问与同步

- 探索网络化技术的未来发展与应用

- Wireshark网络数据包分析与处理技巧全解

- GitHub文件编辑监控:通过Webhook及时获取通知

- 安卓图像处理:实现头像圆角剪裁与照片获取教程

- 点菜管理系统课程设计:数据库应用与程序开发

- MediBang Paint Pro v5.3 32位版本:专业漫画绘制与云同步

- 2019年数学建模竞赛题及翻译分享

- 合同内其它业务收入管理规定全面解析

- AITalker: 探索人工智能聊天助手的开源世界

- Minecraft Spigot插件配置:fkboard动态Web界面

- NumberDrive项目中的表达式解析器NumberDriveParser

- Biu-link:NodeJS实现的文本文件URL缩短器

- 探索Texas LED字体的设计与应用

- QuizizzHelper:简化在线Quizizz操作的JavaScript工具

- 安卓平台头像制作与圆角剪裁功能实现教程