ns-scaled time-coding method for real-time 3D

super-resolution range-gated imaging

Dezhen Lu (卢德贞), Xinwei Wang (王新伟)*, Songtao Fan (范松涛), Jun He (何 军),

Yan Zhou (周 燕), and Yuliang Liu (刘育梁)

Optoelectronics Systems Laboratory, Institute of Semiconductors, Chinese Academy of Sciences,

Beijing 100083, China

*Corresponding author: wangxinwei@semi.ac.cn

Received March 19, 2015; accepted May 27, 2015; posted online June 26, 2015

We present a method of time coding with ABAB synchronization timing control for real-time 3D super-

resolution range-gated imaging (3DSRGI). To meet the high precision of time delay and pulse width in ABAB

synchronization time sequencing, phase shift is implemented to achieve ns-scaled delay and width accuracy

without restoring to high clock frequencies. Theoretical analysis and experiments prove that 1 ns delay and

width precision is obtained by our timing control unit based on a single field-programmable gate array

with 5 ns clock cycle. Finally, a prototype experiment of 3DSRGI is demonstrated at a 10 Hz video rate with

696 pixels × 520 pixels.

OCIS codes: 110.6880, 150.6910.

doi: 10.3788/COL201513.081102.

High-resolution real-time 3D imaging is urgently need for

spatial navigation

[1]

, spacecraft landing and docking

[2]

, and

topographic surveying and mapping

[3]

. However, the

widely investigated 3D flash LIDAR has a low resolution

that cannot satisfy some high-resolution applications in

dynamic environments. For instance, NASA’s Autono-

mous Precision Landing and Hazard Detection and Avoid-

ance Technologies (ALHAT) project has determined that

a single frame of a 3D image generated by the current

state-of-the-art 3D flash LIDAR may not be sufficient

to build a landing site digital elevation map with accept-

able spatial resolution, precision, and area coverage

[2]

.3D

range-gated imaging (3DRGI) is a new prominent tech-

nique of remote sensing with a higher resolution than

3D flash LIDAR

[4]

. The current 3DRGI has been mainly

developed with two approaches: time sliding and super-

resolution. For the method of time sliding, 3D scene

reconstruction is achieved in a post-processing procedure

using hundreds of sliding gated delay time 2D images

[5,6]

,

which has bad performance in real time. 3D super-

resolution range-gated imaging (3DSRGI) can reconstruct

3D images from a minimum number of two 2D range-

gated images

[7–11]

, which has potential for real-time 3D im-

aging. In this Letter, we propose a time-coding method to

realize real-time 3DSRGI where the range-gated imaging

system is synchronized by an ABAB synchronization tim-

ing control. However, the current time delay and pulse

width precision are governed by the clock frequency of

a field-programmable gate array (FPGA)

[12–14]

, which is

the preferred option used to realize the synchronization

timing for reliability, independence, and system integra-

tion reasons. To overcome the synchronization problems,

we propose a phase-shift method to improve the time

delay and pulse width precision to a ns-scale by a single

FPGA. Computer modeling experiments and prototype

field tests are conducted to confirm the improvement of

synchronous control precision and real-time performance

of time coding 3DSRGI.

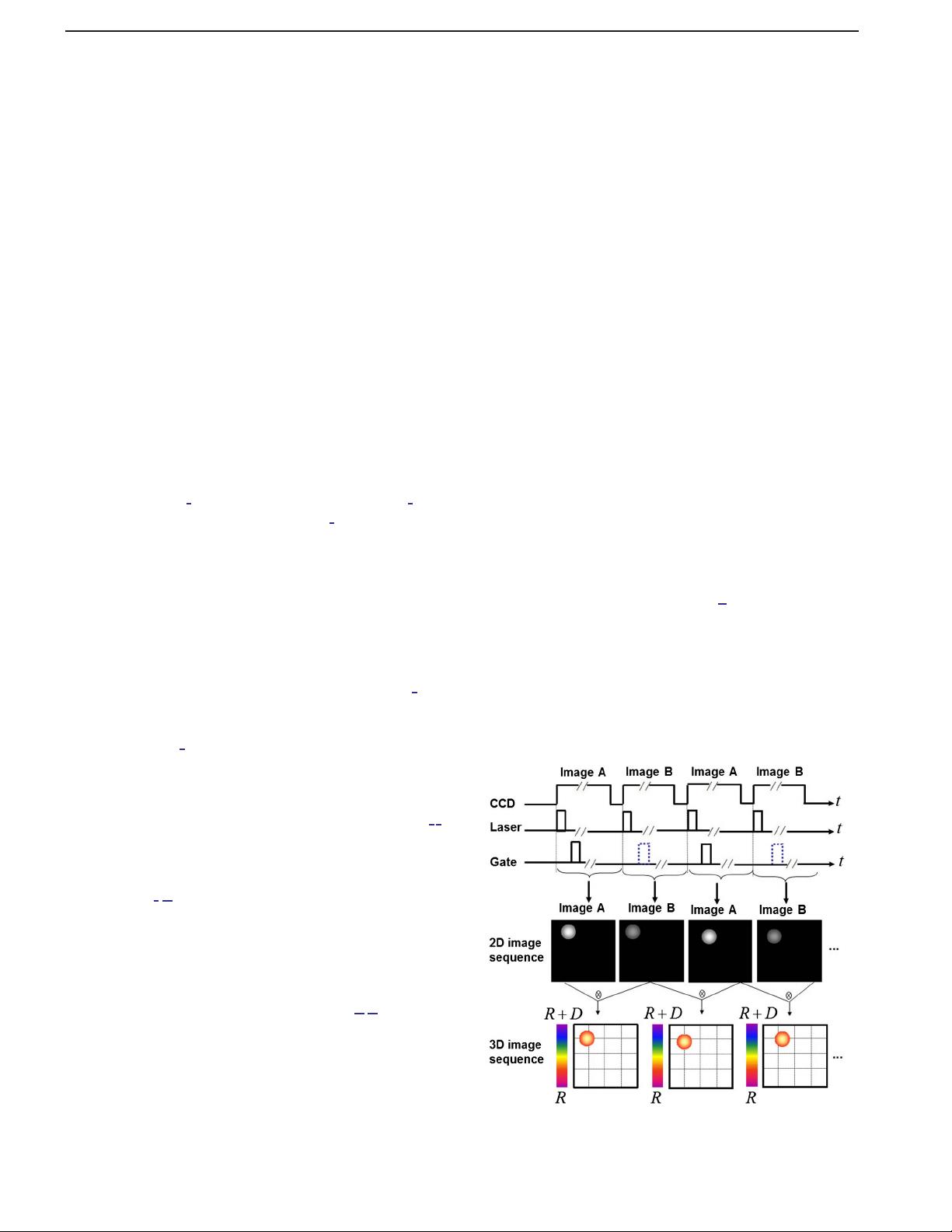

In 3DSRGI, each la ser pulse triggers a camera with a

highly sensitive gate, so that a number of laser pulses

are integrated on a CCD and a CCD eventually produces

a 2D gate image. As depicted in Fig.

1, to realize real-time

3DSRGI, sequences of time coding 2D images (ABAB…)

are recorded by a synchronization timing of ABAB mode

which is generated by a timing control unit (TCU) to syn-

chronize the laser and the gate as well as the CCD. Under

the ABAB synchronization timing sequence the corre-

sponding time-coding images of targets are output and

the two consequent frames inevitably contain a gate image

Fig. 1. Principle of the time-coding method in 3DSRGI.

COL 13(8), 081102(2015) CHINESE OPTICS LETTERS August 10, 2015

1671-7694/2015/081102(5) 081102-1 © 2015 Chinese Optics Letters