FPGA驱动的三参数预选器:高效雷达信号分选利器

21 浏览量

更新于2024-08-30

1

收藏 374KB PDF 举报

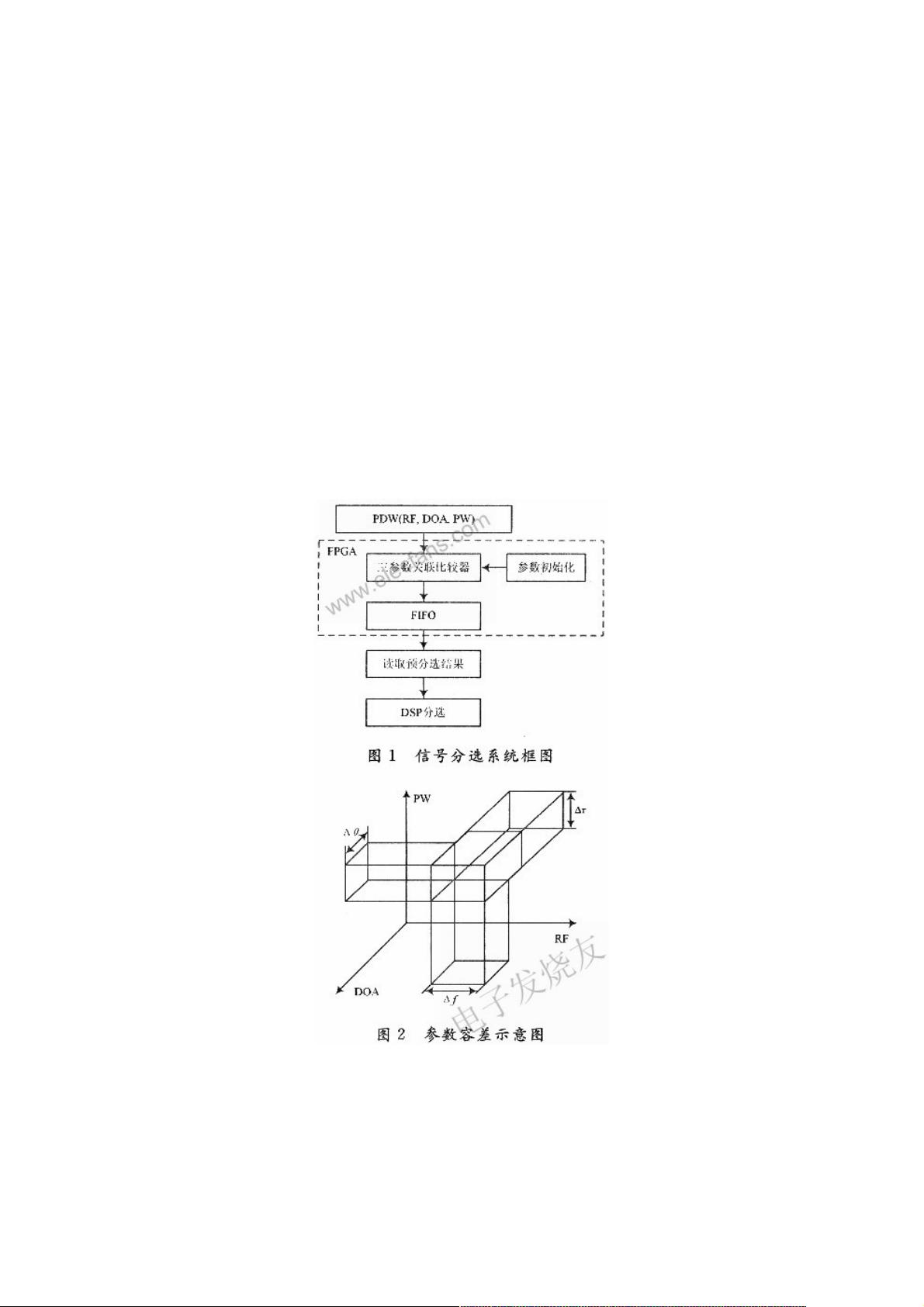

在现代电子战环境中,随着信号密度增加和新体制雷达的广泛应用,实时分选各种雷达信号成为了电子支援措施(ESM)的关键挑战。为了满足快速处理的需求,本文探讨了如何利用高速现场可编程门阵列(FPGA)技术来设计高效的预分选器,替代传统的中小规模集成芯片。

文章的核心内容围绕基于FPGA的三参数关联比较器展开,这三个参数分别是载频(RF)、脉宽(PW)和到达方位(DOA)。RF通常在离散频率点集中,易于识别,是重要的信号特征;DOA反映了雷达与侦察机的相对位置,即使在有运动的情况下,变化也相对较慢,同样具有很高的区分度;PW的稳定性和聚敛性使其成为有效的分选参数。相比之下,脉幅(PA)和到达时间(TOA)由于受多重因素影响,稳定性较差,一般不作为预分选的主要依据。

预分选系统设计包含两个主要阶段:预分选和主分选。预分选由FPGA执行,通过三参数关联比较器来执行RF、PW和DOA的联合分选。这个过程涉及将每个雷达信号看作空间中的一个具有特定坐标的小盒子,其大小由接收机测量精度决定的参数容差决定。当测量精度足够且容差设定合理时,可以有效去除信号交错,从而确定脉冲序列的存在。

关联比较器的设计是整个预分选器的核心。它的工作原理是利用FPGA的并行处理能力,对输入的多个信号进行快速比较,找出符合预设参数范围的信号。通过硬件级别的优化,FPGA能够实现实时高效的数据处理,大大提高了信号处理的性能和效率。

总结来说,本文的技术贡献在于提出了一种利用FPGA的创新方法,通过三参数关联比较器设计预分选器,以应对复杂电子战环境中对信号分选速度和精度的高要求。这种设计既提高了处理效率,又具有良好的可扩展性和优化潜力,对于现代电子战系统具有重要意义。

2020-10-25 上传

2021-07-13 上传

2021-09-30 上传

155 浏览量

189 浏览量

145 浏览量

217 浏览量

182 浏览量

359 浏览量

weixin_38588592

- 粉丝: 3

最新资源

- 易酷免费影视系统:开源网站代码与简易后台管理

- Coursera美国人口普查数据集及使用指南解析

- 德加拉6800卡监控:性能评测与使用指南

- 深度解析OFDM关键技术及其在通信中的应用

- 适用于Windows7 64位和CAD2008的truetable工具

- WM9714声卡与DW9000网卡数据手册解析

- Sqoop 1.99.3版本Hadoop 2.0.0环境配置指南

- 《Super Spicy Gun Game》游戏开发资料库:Unity 2019.4.18f1

- 精易会员浏览器:小尺寸多功能抓包工具

- MySQL安装与故障排除及代码编写全攻略

- C#与SQL2000实现的银行储蓄管理系统开发教程

- 解决Windows下Pthread.dll缺失问题的方法

- I386文件深度解析与oki5530驱动应用

- PCB涂覆OSP工艺应用技术资源下载

- 三菱PLC自动调试台程序实例解析

- 解决OpenCV 3.1编译难题:配置必要的库文件