Cadence Virtuoso EDA平台:模拟IC设计流程详解

"模拟IC设计的EDA平台和流程-cadence"

本文将深入探讨基于Cadence的集成电路(IC)设计流程,特别是使用Virtuoso Analog Design Environment 5.1.41版本。Cadence是一款广泛使用的电子设计自动化(EDA)工具,它提供了全面的解决方案,覆盖了IC设计的各个阶段,从概念到实现再到验证。

课程目标主要是让读者理解并掌握如何利用Cadence的工具进行模拟IC设计。课程大纲包括以下关键部分:

1. 课程介绍:简述课程目标、课程结构、时间安排,以及获取帮助、技术支持和文档的方式。

2. 5.1.41版新特性:介绍此版本更新带来的功能改进和增强。

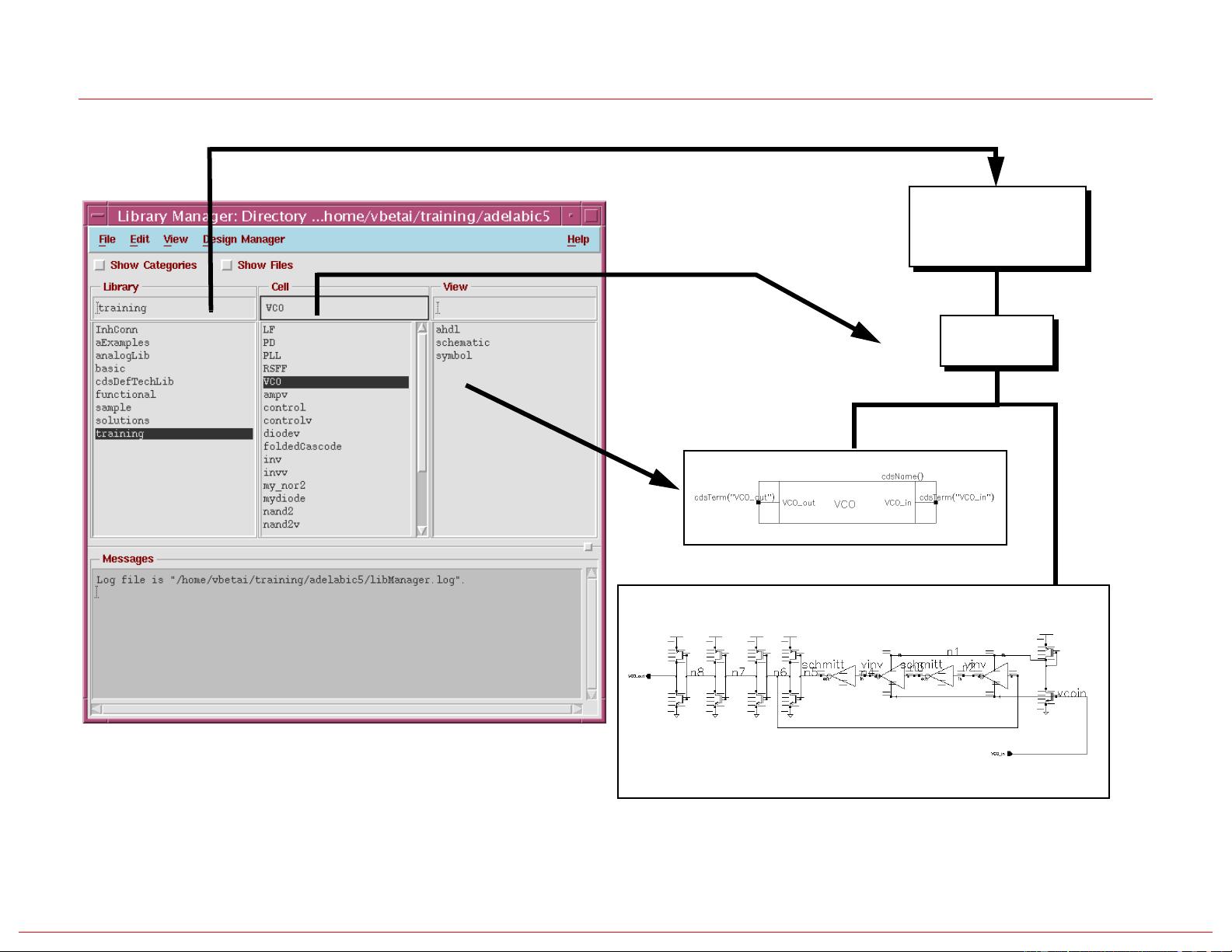

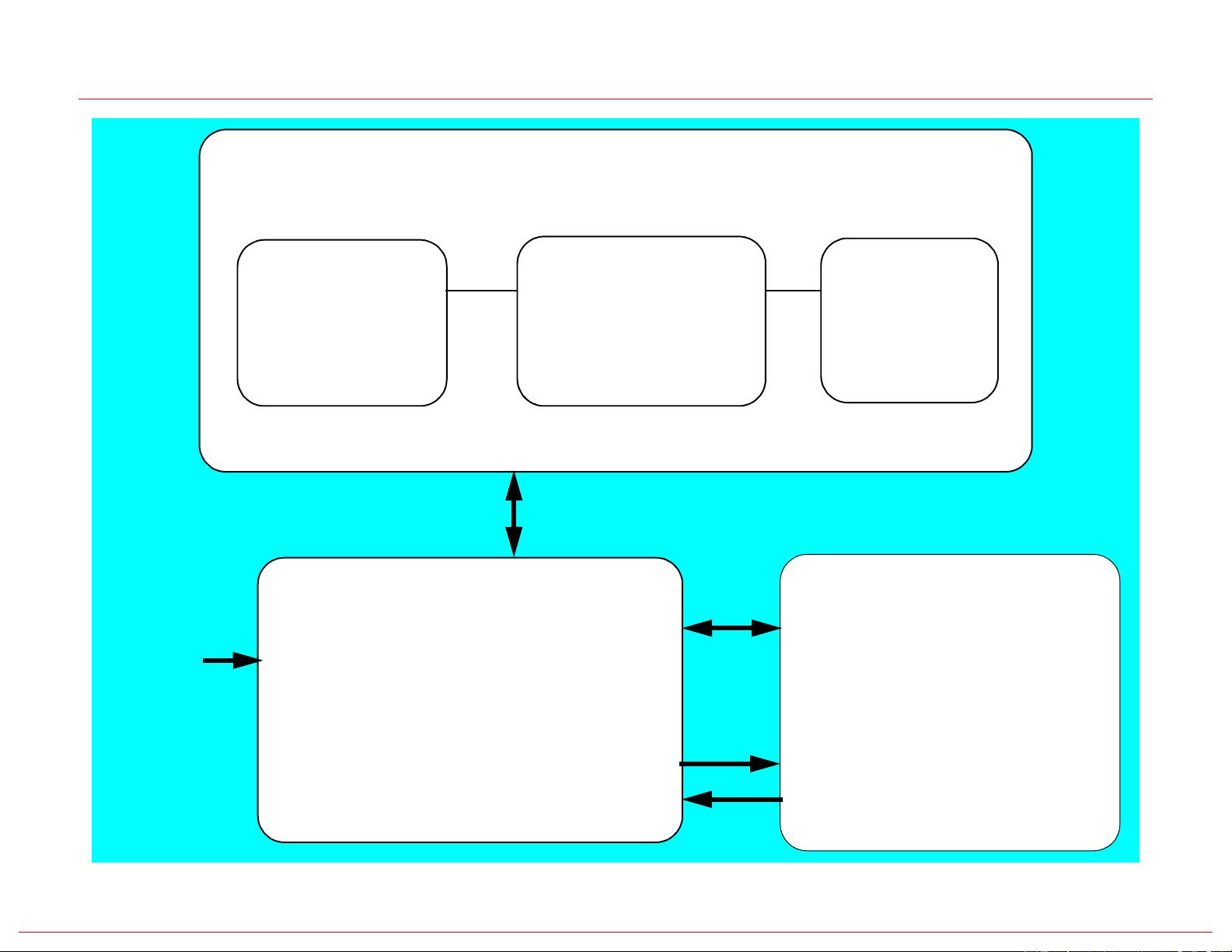

3. 设计框架II设计环境:阐述Cadence的Design Framework II,这是一个集成的设计环境,支持库创建、单元设计和视图管理。

4. 访问设计工具:解释如何启动和配置不同的设计工具,以便进行有效的设计流程。

5. 创建库:详述创建自定义设计库的过程,这是存储设计单元的基础。

6. 细胞和单元视图创建:指导用户如何定义和管理设计中的基本构建块,如晶体管级电路模型。

7. 电路原理图捕获:讲解如何使用Cadence的图形界面来绘制和编辑模拟电路。

8. 模拟仿真:介绍如何执行电路的模拟分析,包括瞬态、稳态、频率域等多种模拟类型。

9. 分析:涵盖不同类型的分析,如噪声分析、功耗分析等,以评估电路性能。

10. 参数化分析:说明如何通过改变参数来研究设计的敏感性和优化。

11. 角度分析:讨论在不同的工艺或温度条件下进行多角分析,以考虑制造过程的不确定性。

12. 蒙特卡洛分析:介绍统计方法,用于评估设计在随机参数变化下的行为。

获取帮助和支持:Cadence提供多种途径获取帮助,包括内置的帮助系统、在线文档、技术支持论坛和技术服务热线,确保用户在遇到问题时能得到及时解答。

在模拟IC设计中,Cadence Virtuoso扮演着核心角色,它提供了一个统一的工作平台,整合了设计、仿真、分析和优化工具,使得复杂的设计任务变得更加高效和可管理。通过学习和熟练掌握这些工具和流程,工程师可以更好地设计出高性能、低功耗的模拟集成电路。

2023-12-31 上传

2023-12-31 上传

2021-05-20 上传

2023-07-14 上传

2021-08-01 上传

2021-08-01 上传

tiantianuser

- 粉丝: 120

- 资源: 7