PRELIMINARY

20 • AR9341 Highly-Integrated and Feature-Rich 802.11n 2x2 2.4 GHz SoC Atheros Communications, Inc.

20 • February 2011 COMPANY CONFIDENTIAL

2.8 SLIC

2.8.1 Overview

The AR9341 provides a single, 4-wired, multi-

channel PCM digital highway for connecting to

a SLIC-based VOIP interface circuit. The SLIC

interface is compatible with a standard PCM

interface based on T1 (24 channels at

1.544 MHz) or E1 (32 channels at 2.048 MHz).

Trunk interfaces are suitable for VOIP

applications. Other non-standard channel

numbers up to 64 channels and a bit rate up to

8.092 MHz are supported via register

configuration. In a VOIP application, the

AR9341 SLIC controller can be configured as a

bridge between the PCM voice interface and

the LAN/WAN/WLAN IP packet interface.

The SLIC controller can transmit/receive on 1,

2, or multiple-time multiplexed 8-bit voice

channels on the PCM trunk. Up to 64 channels

are supported through the bit mask channel

enable registers. All Tx/Rx operations are 8-bit

PCM samples transferred using descriptor-

based DMA controllers (mailboxes) between

the system memory and the trunk interface.

Each direction (Tx and Rx) has one mailbox

DMA controller.

The major features include:

■ Programmable number of SLIC_SLOTs

■ Enabling multiple slots

■ Master or slave programming

■ Short/long frame sync

■ Delayed or non-delayed data operation

mode

■ SLIC enable/disable

■ Programmable divider clock

■ 8-bits/slot (maximum of 64 slots); having 16

bits/slot requires enabling two consecutive

slots. In 16-bit mode, the total number of

slots available becomes 32.

■ Separate interrupts for Rx and Tx DMA

completion

■ SLIC interrupt for unexpected frame sync in

slave mode

■ Bit swap across byte boundary

■ Configurable options to send data at

various edges after frame sync

■ Variations in frame sync duration

– Frame sync can last for a half clock

duration of BIT_CLK

– Frame sync can stay for more than one

clock duration of BIT_CLK (the number

of clocks for which frame sync should be

high is configurable)

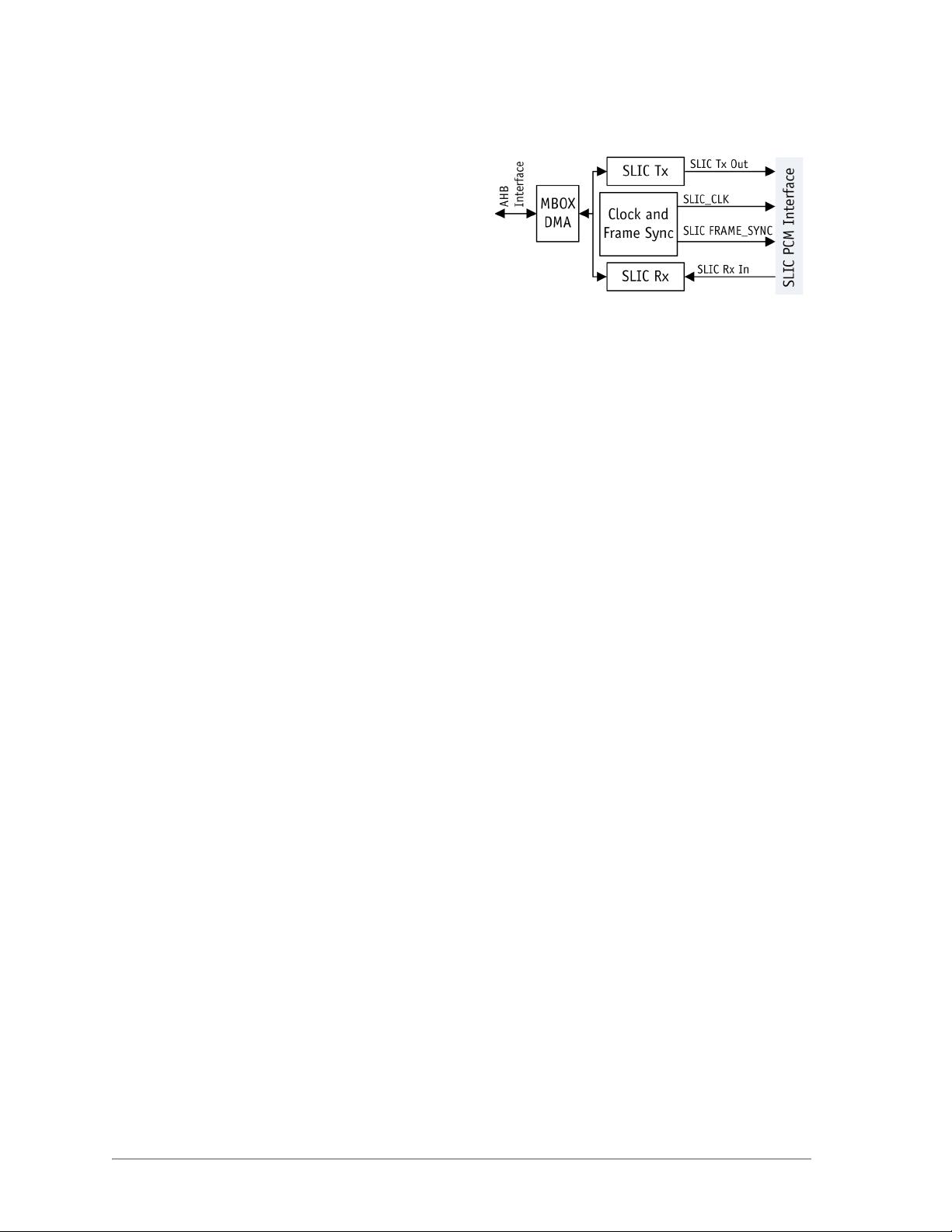

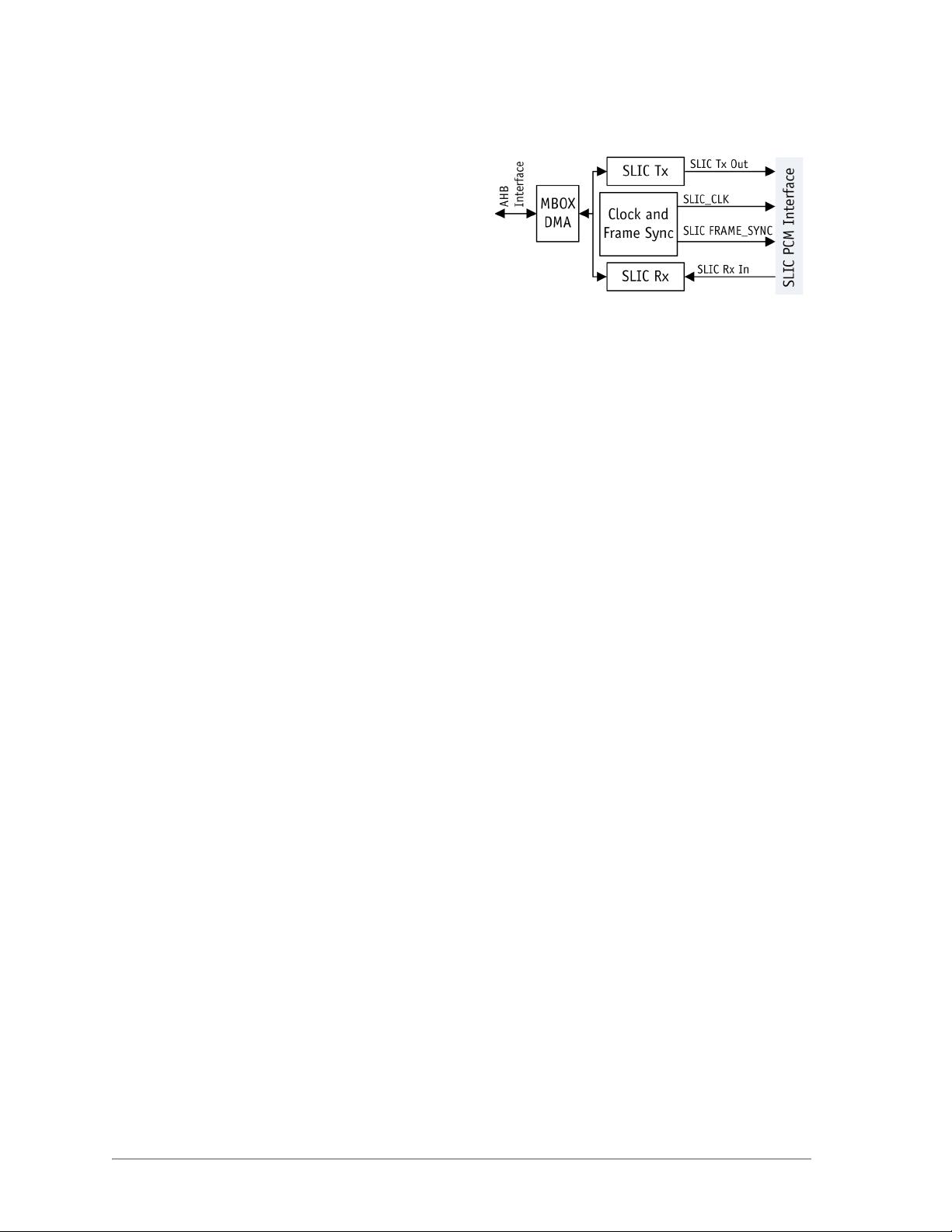

Figure 2-7 shows the SLIC block diagram.

2.8.2 SLIC Interface

The SLIC interface utilizes a versatile mailbox

DMA controller for all data transfers to and

from system Memory. See “Mailbox (DMA

Controller)” on page 33 for more information.

2.8.3 Transmit

In the Tx direction, software prepares suitable

voice buffers from IP packets received from

LAN/WAN/WLAN in system memory, and

hands to the mailbox DMA using descriptors.

The DMA controller reads the buffers from

memory and puts them onto the Tx channels or

time slots on the PCM interface. Only

channels/time slots enabled by the Tx mask

registers are used for sending Tx data. All Tx

data synchronizes with respect to frame sync,

which provides voice sample synchronization

between the source and the voice data receiver.

Channel numbering starts with respect to the

frame sync being asserted and based on

programmable number PCM clocks where

frame sync remains asserted.

2.8.4 Receive

In the Rx direction, the SLIC controller receives

voice samples from the channels/time slots

reenabled by the Rx mask register. These 8-bit

samples are then assembled and DMAed to

system memory based on the buffer pointers

provided in the Rx descriptors. Like Tx, all Rx

sample operations synchronize with respect to

frame sync. Channel numbering starts with

frame sync being asserted and is based on the

programmable number of PCM clocks where

frame sync remains asserted.

Figure 2-7. SLIC Block Diagram