Nios在FPGA中的嵌入式处理器策略与通用编解码器应用

59 浏览量

更新于2024-08-30

收藏 236KB PDF 举报

Nios在通用编译码器中的应用是Altera针对FPGA市场推出的一种嵌入式处理器解决方案。随着ASIC开发成本上升,OEM厂商倾向于选择FPGA来构建系统,因为它们提供了灵活性和成本效益。Altera的Nios系列包括三种产品,Nios/f、Nios/s和Nios/e,分别满足不同性能和FPGA资源需求:Nios/f提供最高性能但FPGA占用较多,Nios/s有较高的性能和较低的资源消耗,Nios/e则是低成本和最少FPGA使用的选择。

Nios系列的核心特点是都具备32位处理器架构,包括32位指令集、数据和地址路径、通用寄存器以及32个外部中断源,支持统一的指令集架构(ISA),确保软件的二进制兼容性。这种设计使得设计者可以根据项目需求调整处理器,无需重写软件,节省了时间和成本。

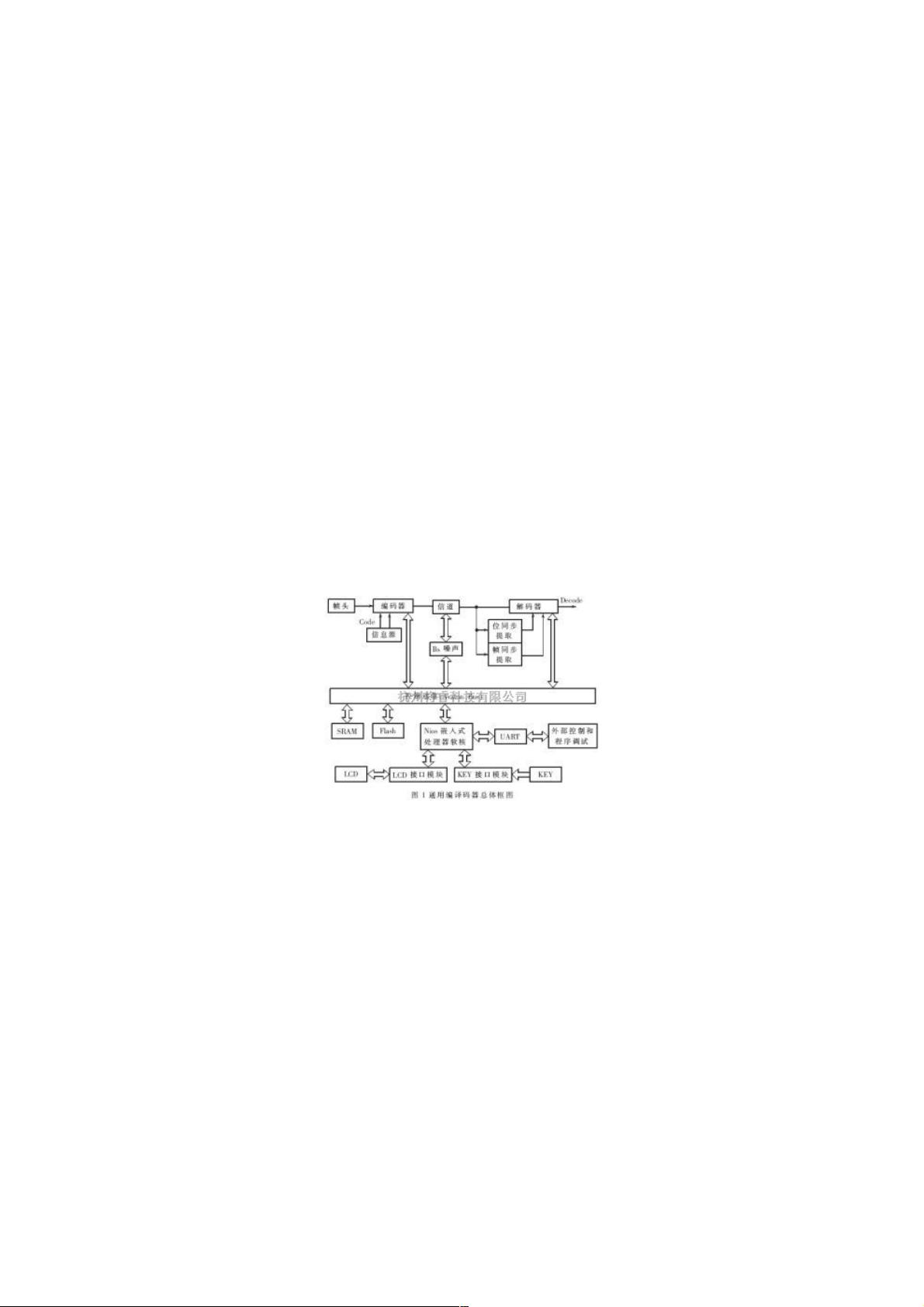

这款基于Nios的通用编解码器是一个集成的硬件设计,将编解码模块、微处理器控制以及其他外围设备如LCD和键盘整合到单个FPGA中。这样的设计显著减少了外围电路的数量,提高了系统集成度,简化了电路板布局,增强了抗干扰能力,并且由于FPGA的可编程特性,便于系统扩展和升级,适应不同通信系统的需要。

具体实现上,编解码器的设计流程包括信息源接收、编码器编码、信道仿真、同步提取、译码器解码以及与内存和外设交互等功能。所有这些操作都在Nios软核的控制下进行,用户能够灵活配置编解码器的工作模式和参数,例如设置编解码类型和信码速率,同时利用LCD显示结果。

总结来说,Nios在通用编解码器中的应用展示了其在FPGA环境中的高效性能和灵活性,为系统设计者提供了定制化和易于扩展的解决方案,尤其适合那些需要高效处理能力和低成本应用的场景。

2023-06-21 上传

2023-06-07 上传

2023-02-06 上传

2023-07-24 上传

2023-02-12 上传

2023-05-15 上传

2024-02-06 上传

2024-01-16 上传

2023-02-06 上传

weixin_38641876

- 粉丝: 3

- 资源: 942

最新资源

- Unity UGUI性能优化实战:UGUI_BatchDemo示例

- Java实现小游戏飞翔的小鸟教程分享

- Ant Design 4.16.8:企业级React组件库的最新更新

- Windows下MongoDB的安装教程与步骤

- 婚庆公司响应式网站模板源码下载

- 高端旅行推荐:官网模板及移动响应式网页设计

- Java基础教程:类与接口的实现与应用

- 高级版照片排版软件功能介绍与操作指南

- 精品黑色插画设计师作品展示网页模板

- 蓝色互联网科技企业Bootstrap网站模板下载

- MQTTFX 1.7.1版:Windows平台最强Mqtt客户端体验

- 黑色摄影主题响应式网站模板设计案例

- 扁平化风格商业旅游网站模板设计

- 绿色留学H5模板:科研教育机构官网解决方案

- Linux环境下EMQX安装全流程指导

- 可爱卡通儿童APP官网模板_复古绿色动画设计