高速设计中的IBIS建模与关键技术探讨

IBIS (Industry Standard for Interconnect Emulators) 是一种广泛应用于高速设计中的模型化工具,旨在精确地模拟电子组件的行为,特别是在数字电路中的信号传输特性。在JEDEX2004 IBIS Workshop中,Dr. Lynne Green 提供了深入的讲解,涵盖了IBIS规范、模型构建方法以及高级应用技术。

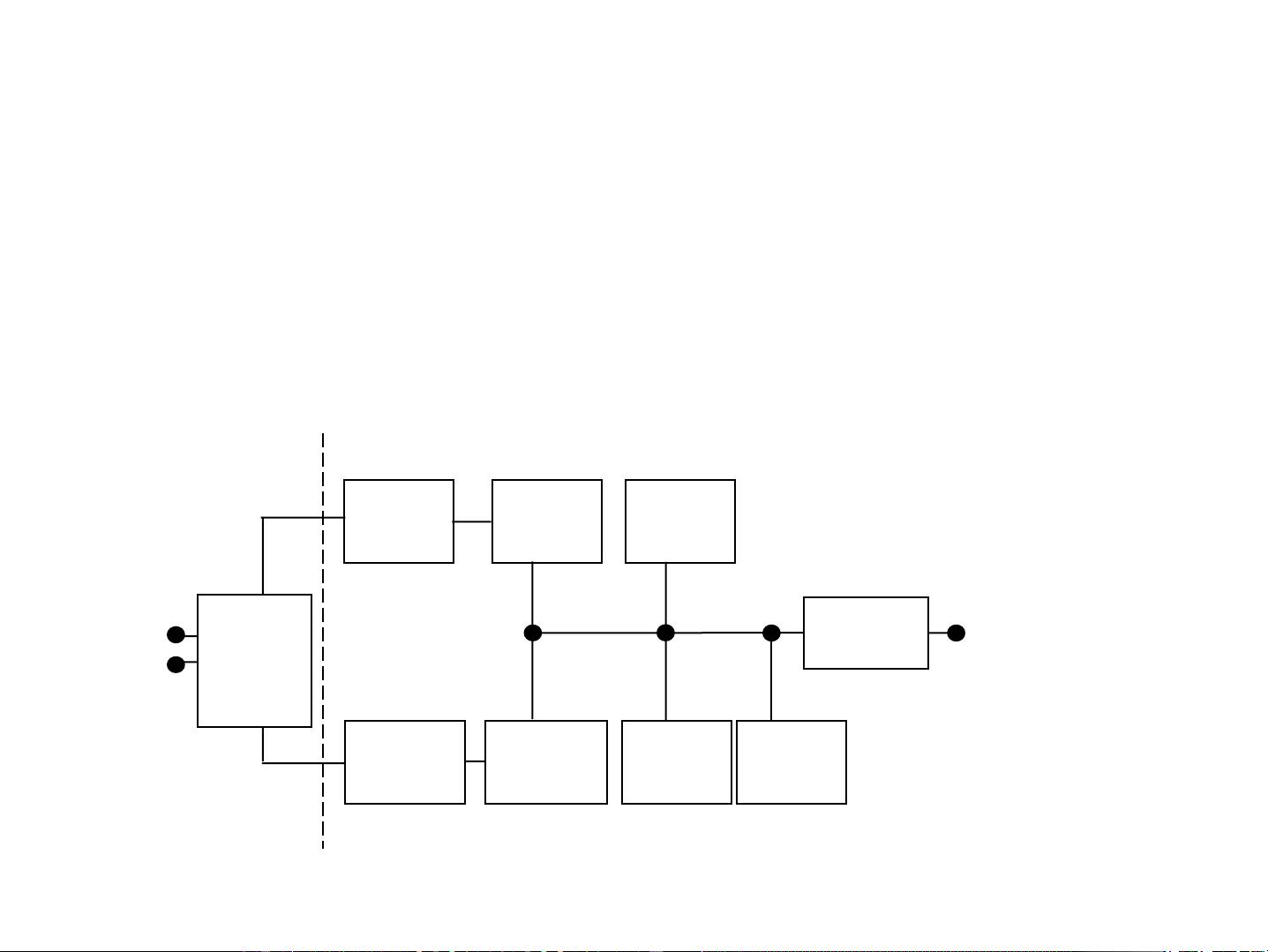

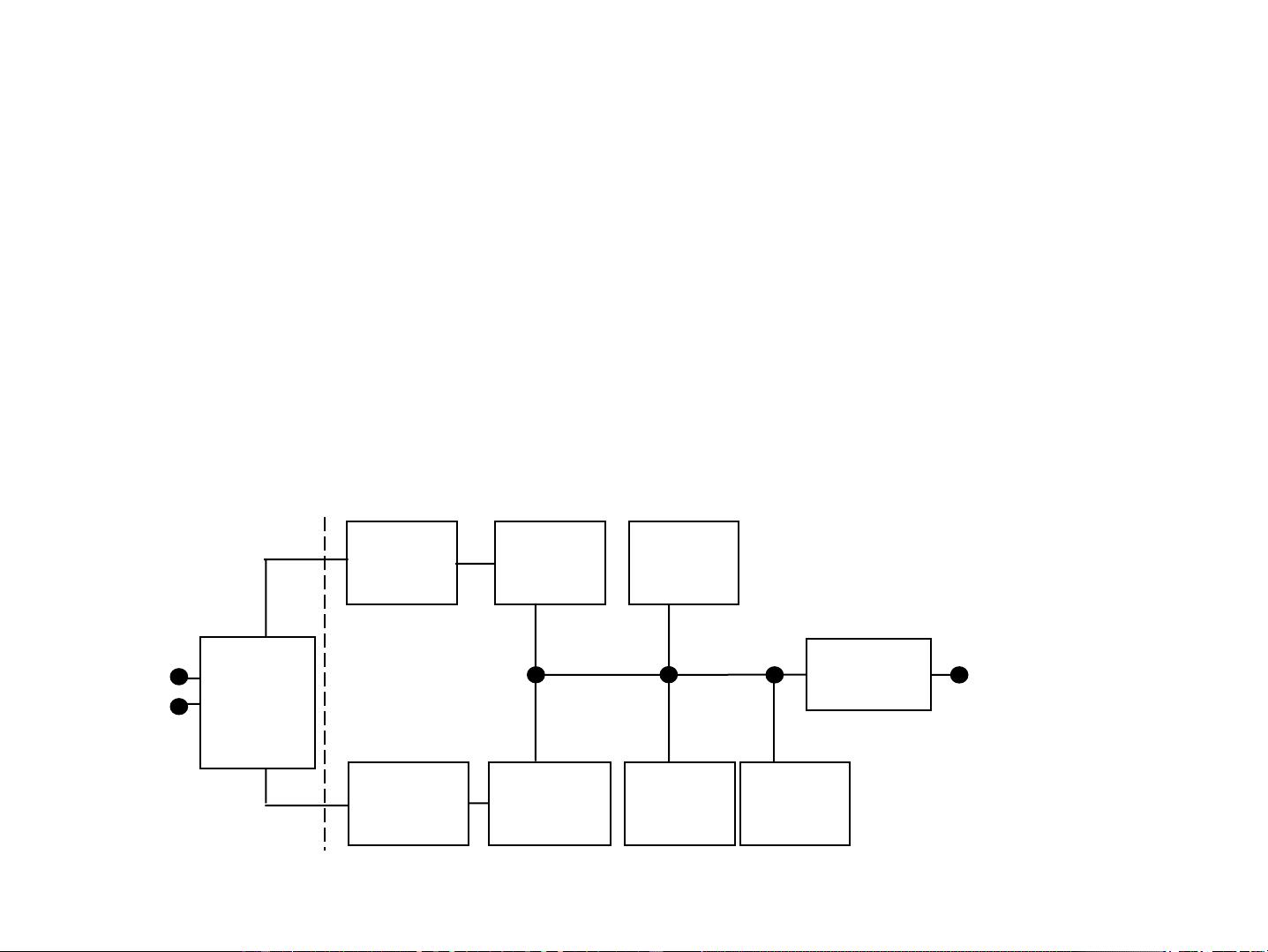

该研讨会首先介绍了上午的内容,包括IBIS规范的核心要素,这涉及到如何创建和理解模型的结构与功能。参与者学习了如何使用官方规格来确保模型的准确性和一致性,以及有效的验证方法,以便识别并解决常见的问题。此外,课程还提到了如何处理高速设计中的特殊挑战,如差分缓冲器模型和封装模型的建模技巧。

下午的环节深入探讨了针对高速设计的模型优化技术,例如针对高速数据传输的时序分析,以及如何通过IBIS模型实现信号完整性管理。参会者能够了解到如何在实际设计中利用这些模型来提高系统性能,减少信号噪音和反射,并且如何避免潜在的信号延迟或抖动。

在资源链接部分,IBIS官方网站(http://www.eigroup.org/ibis/ibis.htm)是获取最新标准、规格文档、实用工具和教程的重要入口。例如,IBIS Cookbook 和 BIRDs(Best Industry Design Resources)提供了丰富的实践指南和案例研究,帮助设计师更好地理解和应用IBIS模型。同时,还有专门的解析器(Parser)如http://www.eda.org/pub/ibis/ibischk3/,以及质量检查清单(Quality Checklist)和培训材料,如SI-Soft的http://www.sisoft.com/ibis-quality/checklist/,这些都是提升模型质量和工程效率的关键资源。

此外,该研讨会还提供了一个免费的模型审查服务,允许设计师们将自己的模型提交进行专业评估,这对于保证模型的准确性和可靠性具有重要意义。电子邮件论坛如ibis-users和ibis-request@eda.org,以及SI-list相关的邮件列表,为用户提供了一个交流和解决问题的平台。

JEDEX2004 IBIS Workshop是一次宝贵的培训机会,不仅教授了构建和使用IBIS模型的基本原理,还涵盖了针对高速设计的特殊应用场景,为电子工程师们提供了解决高速信号传输复杂性问题的实用工具和策略。通过学习和掌握这些知识,设计师可以显著提高他们的设计效率和产品质量。

160 浏览量

214 浏览量

2023-01-09 上传

129 浏览量

2022-09-23 上传

lvyue213

- 粉丝: 2

- 资源: 6

最新资源

- Simple_scraper

- 行销导向式服务的认识PPT

- Elearning:在线学习

- gradle-4.10.1-all文件夹.rar

- ImageJ-Tools:核分割和比例定量

- android_magic_conch_shell:电视节目Spongebob Squarepants中的Magic Conch Shell的Android应用程序

- finiki:Finiki-以旧换新

- 井字游戏:井字游戏

- Qex Studio:从 BIM 模型创建预算-开源

- Autojs调用zxing实现扫码功能

- crud-surittec:CRUD Paraavaliaçãopela empresa Surittec

- opencv_python-3.4.4.19-cp35-cp35m-linux_armv7l.zip

- image-preloadr:将图像数组预加载到body元素底部的dom

- Praktyki2GG:Nowe repo bo tamtebyłosłabeD

- LinearAlgebra:线性代数简介的注释和python代码

- e-commerce:带有Commerce.js和Stripe.js的电子商务应用程序