亚稳态:产生、消除与CDC检查解析

需积分: 13 145 浏览量

更新于2024-08-07

收藏 909KB PDF 举报

"亚稳态产生消除与避免.pdf"

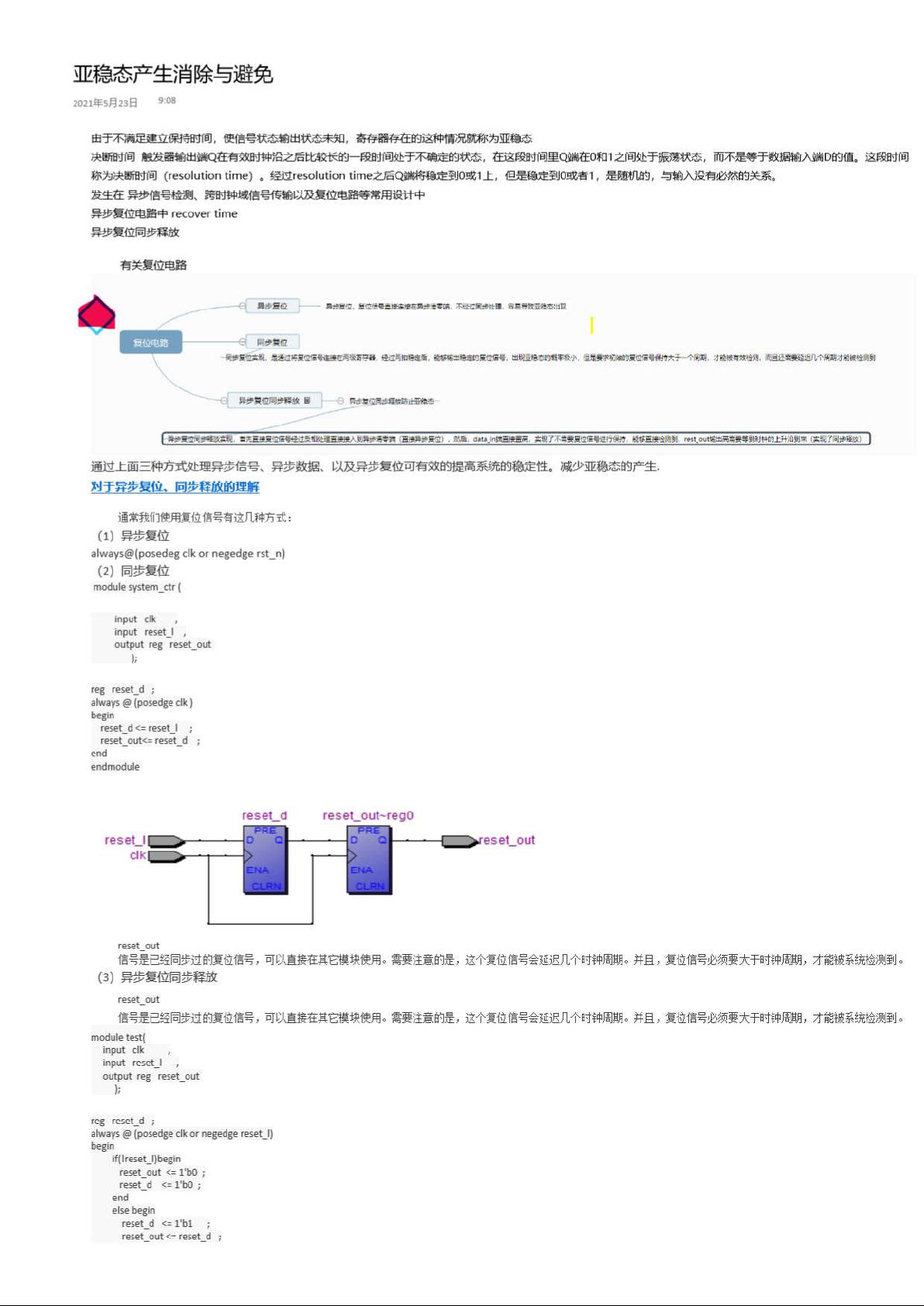

本文主要探讨了数字集成电路设计中的一个重要概念——亚稳态,以及如何有效地避免和消除亚稳态。亚稳态通常发生在跨时钟域的数据传输中,由于不同时钟域之间没有固定的相位关系,可能导致数据在传输过程中出现不稳定状态,从而引发功能错误。

亚稳态产生的机理:

当数据在两个不同时钟域之间传递时,如果接收端的采样时刻没有恰巧落在发送端时钟的上升沿或下降沿,就可能出现亚稳态。这种情况下,接收端无法立即确定接收到的数据是稳定还是处于不确定状态,需要一段时间进行恢复,这段时间被称为亚稳态持续期。

消除亚稳态的方法:

1. 同步设计:通过同步电路确保数据在稳定的时钟域内处理,比如使用多级寄存器同步、异步FIFO和握手协议等,以防止亚稳态信号无序传播。

2. 延迟锁定环(DLL)和相位锁定环(PLL):这些电路可以调整时钟,使不同时钟域的边缘尽可能对齐,减少亚稳态的可能性。

3. 适当的数据路径设计:确保数据传输路径上的延迟满足建立时间(setup time)和保持时间(hold time)要求,以避免亚稳态的产生。

4. 强化时钟树结构:优化时钟分配,减小时钟偏斜,确保时钟信号到达各个部分的延迟一致。

跨时钟域处理(CDC):

在大规模集成电路(SOC)设计中,跨时钟域的处理至关重要。有效的CDC策略包括使用专用的同步检查工具,例如Conformal CDC和Spyglass CDC,进行静态的CDC检查,以确保设计的正确性。前端signoff阶段的CDC检查是保证数字IC设计质量的关键步骤。

时钟域相关概念:

- 时钟:时钟信号是周期性的脉冲,控制芯片内部晶体管的工作,就像心脏的跳动,决定了芯片执行任务的节奏。

- 时钟偏斜(clock skew):时钟信号在芯片的不同位置到达的时间差,可能影响数据采样的准确性,需要通过优化布线和时钟树结构来减少。

亚稳态的管理和避免是数字IC设计中的核心问题,设计师必须理解其原理并采取有效措施来消除潜在风险,以确保电路的稳定性和可靠性。通过同步设计、时钟同步技术以及使用专业的EDA工具,可以有效地管理和减少亚稳态带来的影响,保证系统的正常运行。

244 浏览量

2009-09-06 上传

2021-07-13 上传

2022-01-04 上传

2021-10-30 上传

2022-02-05 上传

363 浏览量

2021-11-02 上传

432 浏览量

qet159357

- 粉丝: 2

最新资源

- 易酷免费影视系统:开源网站代码与简易后台管理

- Coursera美国人口普查数据集及使用指南解析

- 德加拉6800卡监控:性能评测与使用指南

- 深度解析OFDM关键技术及其在通信中的应用

- 适用于Windows7 64位和CAD2008的truetable工具

- WM9714声卡与DW9000网卡数据手册解析

- Sqoop 1.99.3版本Hadoop 2.0.0环境配置指南

- 《Super Spicy Gun Game》游戏开发资料库:Unity 2019.4.18f1

- 精易会员浏览器:小尺寸多功能抓包工具

- MySQL安装与故障排除及代码编写全攻略

- C#与SQL2000实现的银行储蓄管理系统开发教程

- 解决Windows下Pthread.dll缺失问题的方法

- I386文件深度解析与oki5530驱动应用

- PCB涂覆OSP工艺应用技术资源下载

- 三菱PLC自动调试台程序实例解析

- 解决OpenCV 3.1编译难题:配置必要的库文件