"VerilogPresent-v1.3 是一份关于Verilog语言的学习资料,涵盖了Verilog的基本元素、门级建模、数据流建模、行为建模以及模拟和测试平台的介绍,适合FPGA和数字电路设计者使用。"

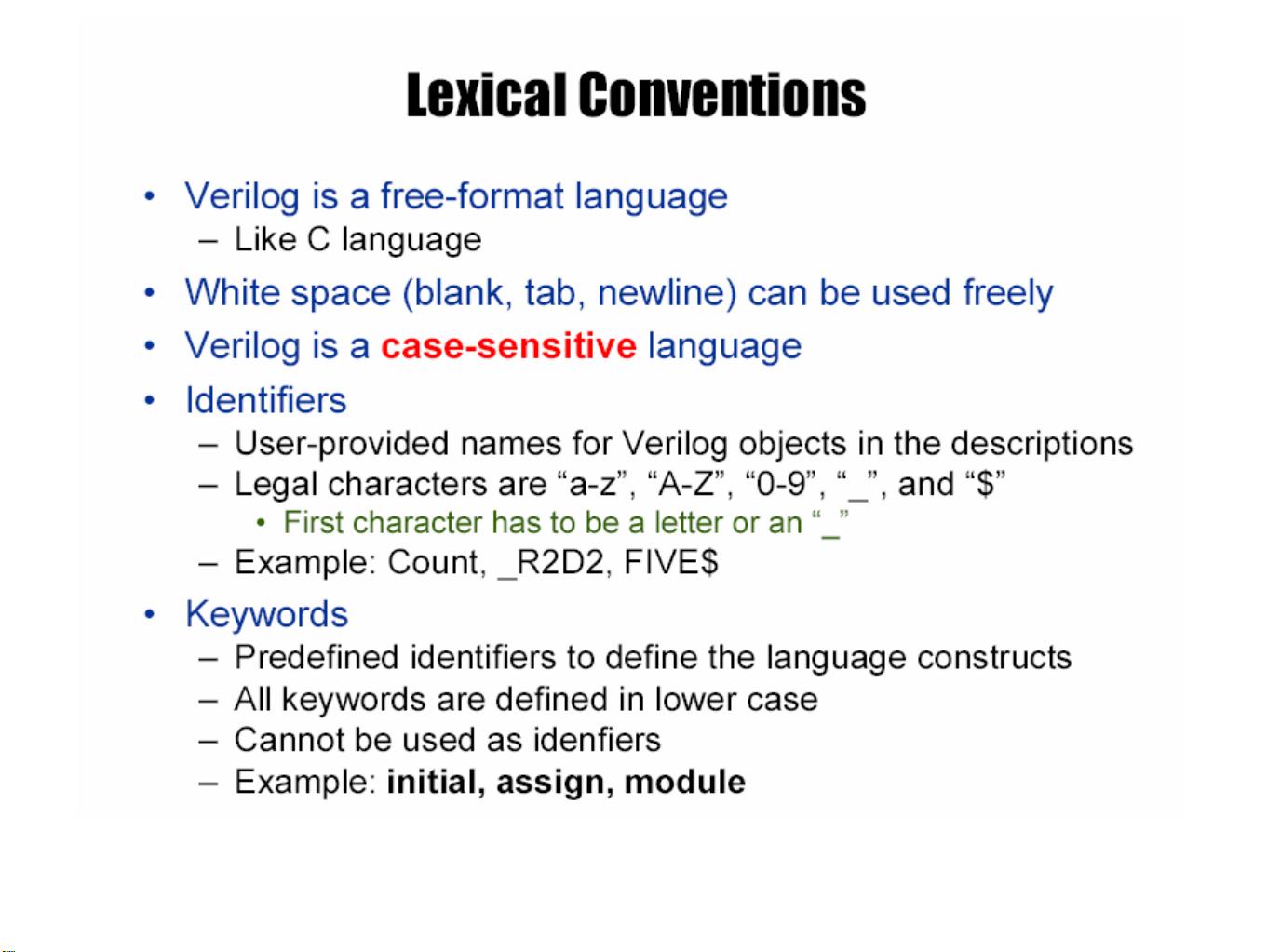

在电子设计自动化(EDA)领域,Verilog是一种广泛使用的硬件描述语言(HDL),它允许工程师以不同的抽象层次来描述数字系统的逻辑。这份文档“VERILOG TUTORIAL”是学习Verilog语言的一个经典教程,特别适合那些对FPGA(Field-Programmable Gate Array)开发和数字电路设计感兴趣的人员。

1. **语言元素**:

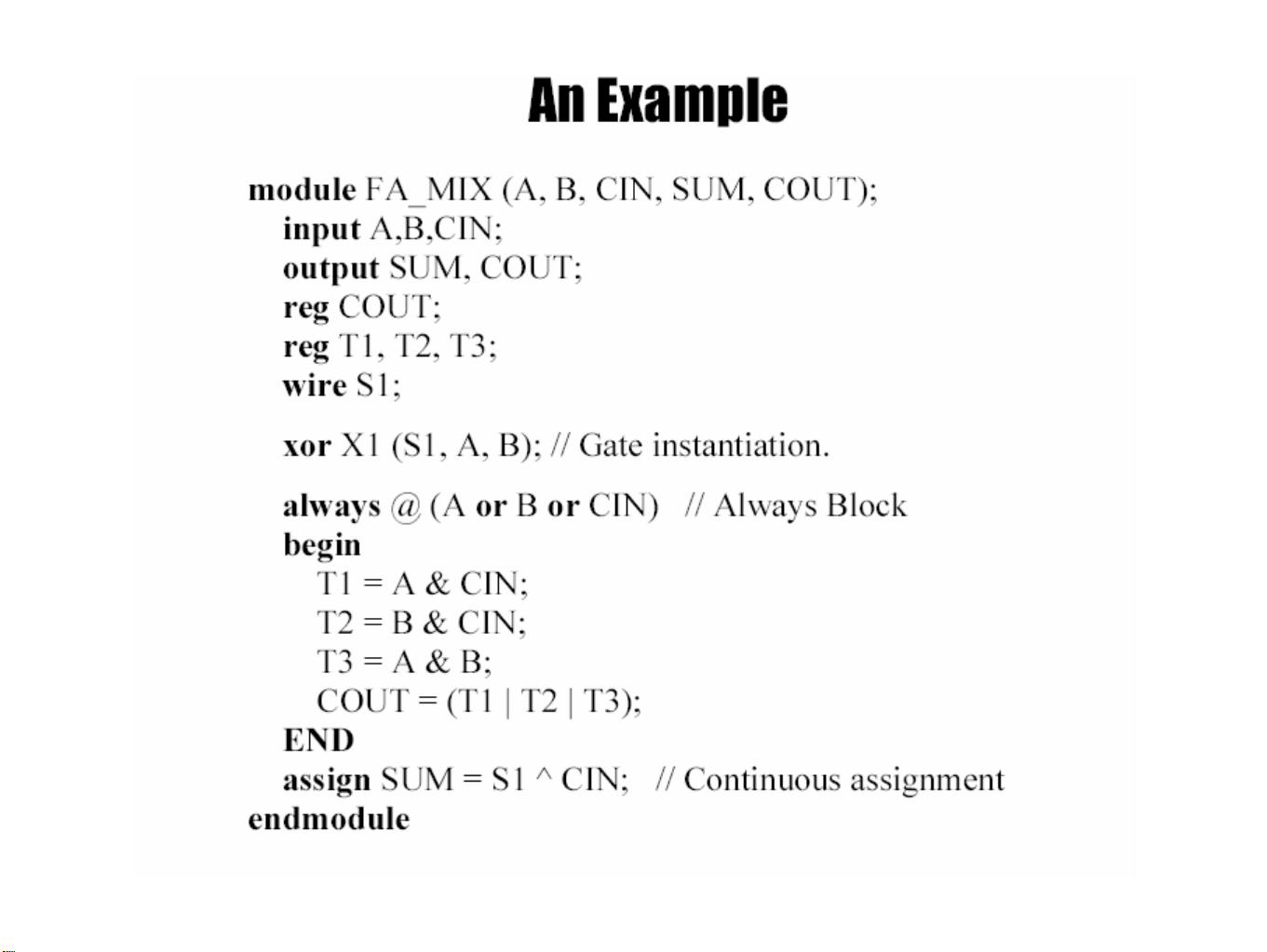

Verilog语言包括基本的数据类型(如reg、wire)、运算符、过程(如always、initial)、模块(module)和实例化(instance)等元素。这些元素构成了描述数字系统的基础。例如,`reg`类型的变量用于存储状态信息,而`wire`类型的变量则表示信号的传输路径。

2. **门级建模**:

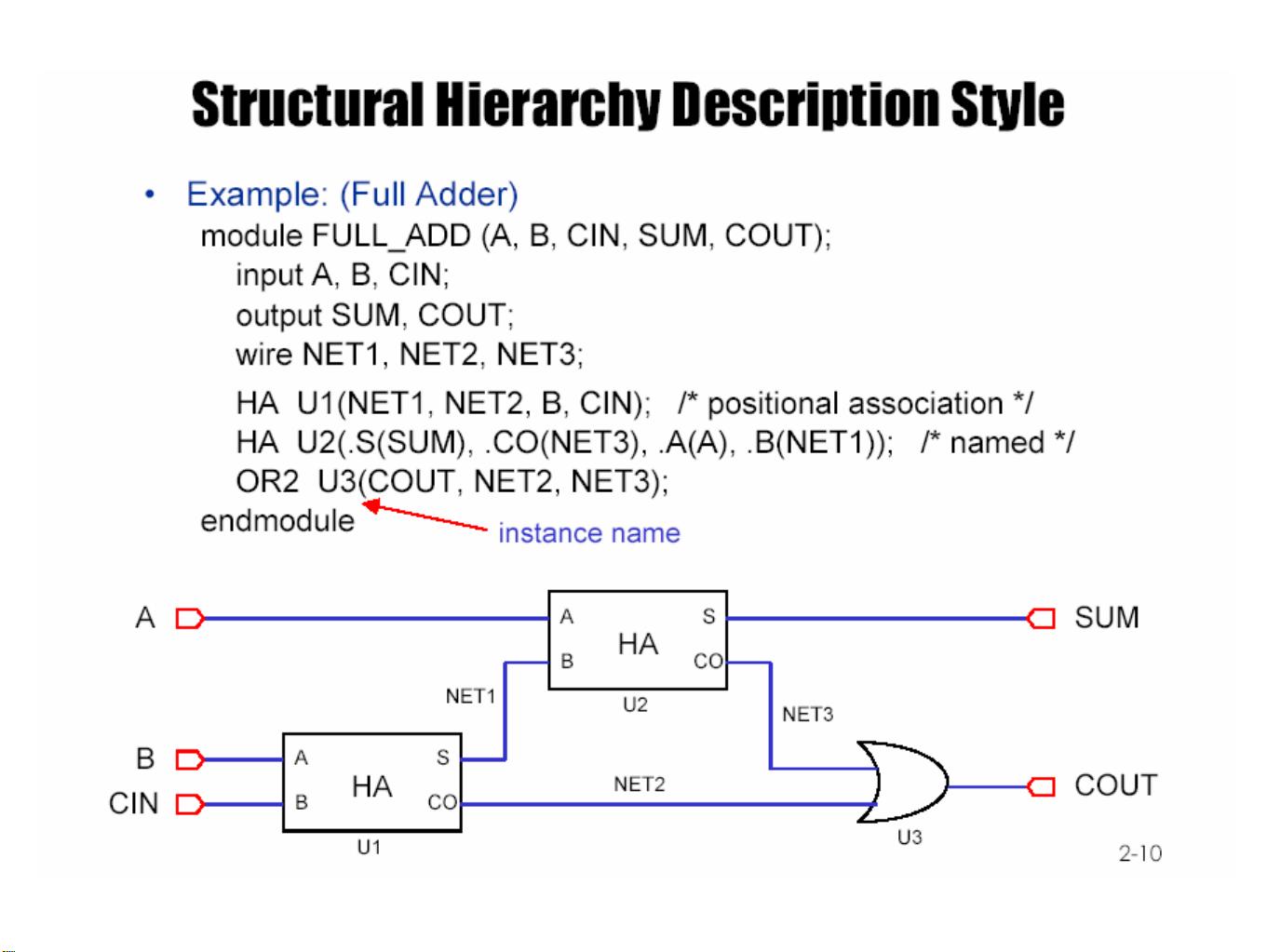

在门级建模中,Verilog用于表示基本的逻辑门,如AND、OR、NOT、NAND、NOR等,以及更复杂的门,如MUX、DFF等。通过这些门,可以构建出基本的逻辑电路。门级模型通常用于芯片的物理实现阶段,当需要详细到晶体管级别的设计时非常有用。

3. **数据流建模**:

数据流建模关注的是数据在系统中的流动,通常与寄存器传输级(RTL)建模相结合。在Verilog中,这可以通过always块来实现,描述数据如何在不同寄存器之间移动,以及如何处理这些数据。

4. **行为建模**:

行为建模,也称为算法级或RTL建模,主要关注系统的功能行为,而不是具体的实现细节。它可以使用高级语言构造来描述算法,如循环、条件语句等,这使得设计者能快速验证设计的功能正确性,而不必考虑底层实现。

5. **建模示例**:

教程中会提供各种示例,展示如何用Verilog描述不同的数字系统,如计数器、加法器、状态机等,帮助读者理解并应用这些概念。

6. **模拟和测试平台**:

Verilog模拟是验证设计的关键步骤。在文档中,将介绍如何创建测试平台(testbench),通过激励生成和断言来验证设计的行为是否符合预期。这通常包括编写测试向量,设置边界条件,以及使用非阻塞赋值(non-blocking assignments)来确保正确的时间行为模拟。

7. **设计的抽象层次**:

Verilog支持从行为级到门级的多种抽象层次。行为级模型最接近于高级算法描述,而门级模型则接近实际的电路实现。介于两者之间的RTL建模是最常用的设计层次,它描述了数据在寄存器之间的转移和处理方式。

通过深入学习和实践“VerilogPresent-v1.3”,读者可以掌握Verilog语言的核心概念,并具备设计和验证FPGA项目的能力。这份文档将有助于提升设计者的数字系统设计技能,为进入更复杂的系统设计打下坚实基础。