"计算机组成原理课程设计报告:阵列乘法器设计"

版权申诉

《计算机组成原理阵列乘法器课程设计报告》是由计算机学院的唐健峰和黄亚军共同完成的一份报告。该报告是针对计算机组成原理课程中的4位乘法整列设计的课程项目。该课程设计旨在帮助学生深入理解计算机组成原理中的乘法运算,并通过实际的设计和实现过程来提高他们的实践能力。在教师的指导下,唐健峰和黄亚军成功完成了这个项目,展示了他们在计算机科学与技术领域的扎实知识和技能。

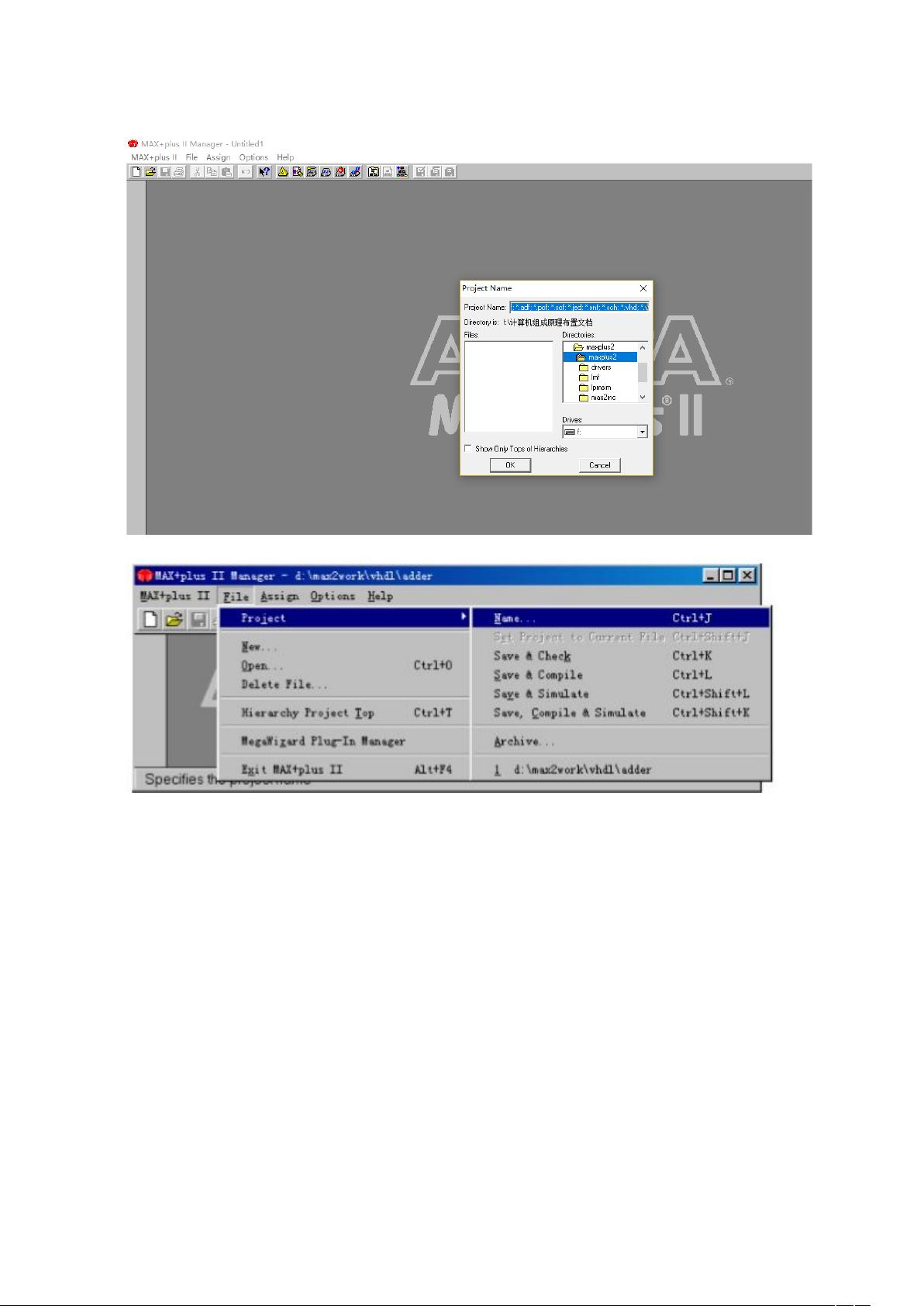

在该课程设计中,学生们首先学习了计算机组成原理中的乘法器原理和阵列乘法器的设计思想。通过对各种乘法器的结构和算法进行分析和比较,他们深入了解了乘法运算在计算机中的重要性和应用场景。在此基础上,唐健峰和黄亚军开始了他们的设计工作,通过对乘法器的功能和性能要求进行详细分析,他们设计并实现了一个高效的4位乘法整列。他们考虑了乘法器的结构、功能模块的划分和数据通路的设计,最终完成了一个符合要求的乘法器设计。

除了设计和实现阵列乘法器,唐健峰和黄亚军还对他们的设计进行了测试和优化。他们编写了测试用例,并通过仿真和实验验证了乘法器的正确性和性能。在测试过程中,他们发现了一些问题并对其进行了调整和改进,最终使乘法器达到了预期的效果。通过这一过程,他们不仅加深了对乘法器设计原理的理解,还提高了对计算机组成原理课程内容的实际运用能力。

在整个课程设计过程中,唐健峰和黄亚军充分展现了他们的团队合作能力和技术水平。他们相互配合,共同分工,有效地完成了设计任务。同时,他们还充分发挥了自己的创造力和解决问题的能力,不断探索和尝试,最终取得了成功。通过这个课程设计项目,他们不仅提高了自己的专业知识水平,还培养了实践能力和团队协作意识,为他们未来在计算机科学与技术领域的发展奠定了良好的基础。

综上所述,《计算机组成原理阵列乘法器课程设计报告》是一份成功的设计项目,通过这个项目,唐健峰和黄亚军深入学习和实践了计算机组成原理中的乘法器设计原理,提高了实践能力和团队协作能力。他们的努力和成果不仅丰富了自己的专业知识,还为未来的学习和发展打下了坚实的基础。希望他们在今后的学习和工作中能够继续保持努力和创新精神,取得更大的成就。

2023-05-28 上传

2021-10-11 上传

2021-10-03 上传

2021-12-20 上传

2021-10-03 上传

2022-07-07 上传

gjmm89

- 粉丝: 15

- 资源: 19万+

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析