FPGA基DDS函数信号发生器设计:多波形生成与调制实现

版权申诉

120 浏览量

更新于2024-06-29

收藏 2.6MB PDF 举报

本文主要探讨的是基于FPGA(现场可编程门阵列)的函数信号发生器设计,针对当前测试设备和技术需求的提升,信号发生器作为关键测试工具的重要性日益凸显。函数信号发生器在通信、测量、雷达、控制和教育等多个领域具有广泛应用。

文章首先介绍了函数信号发生器的基本概念及其在现代化测试中的核心地位。随着中国经济发展和技术进步,对信号发生器的性能和灵活性提出了更高的标准,例如多波形输出和灵活的调制能力。传统的信号发生器技术存在一定的局限性,无法满足这些新需求。

为了实现这些功能,作者选择了Altera公司的FPGA芯片作为核心,这是因为FPGA以其高集成度、灵活性和可编程特性,非常适合用于设计高性能的信号发生器。作为开发工具,文章采用了硬件描述语言Verilog HDL,这是一种强大的并行编程语言,特别适合于设计复杂的数字逻辑电路。

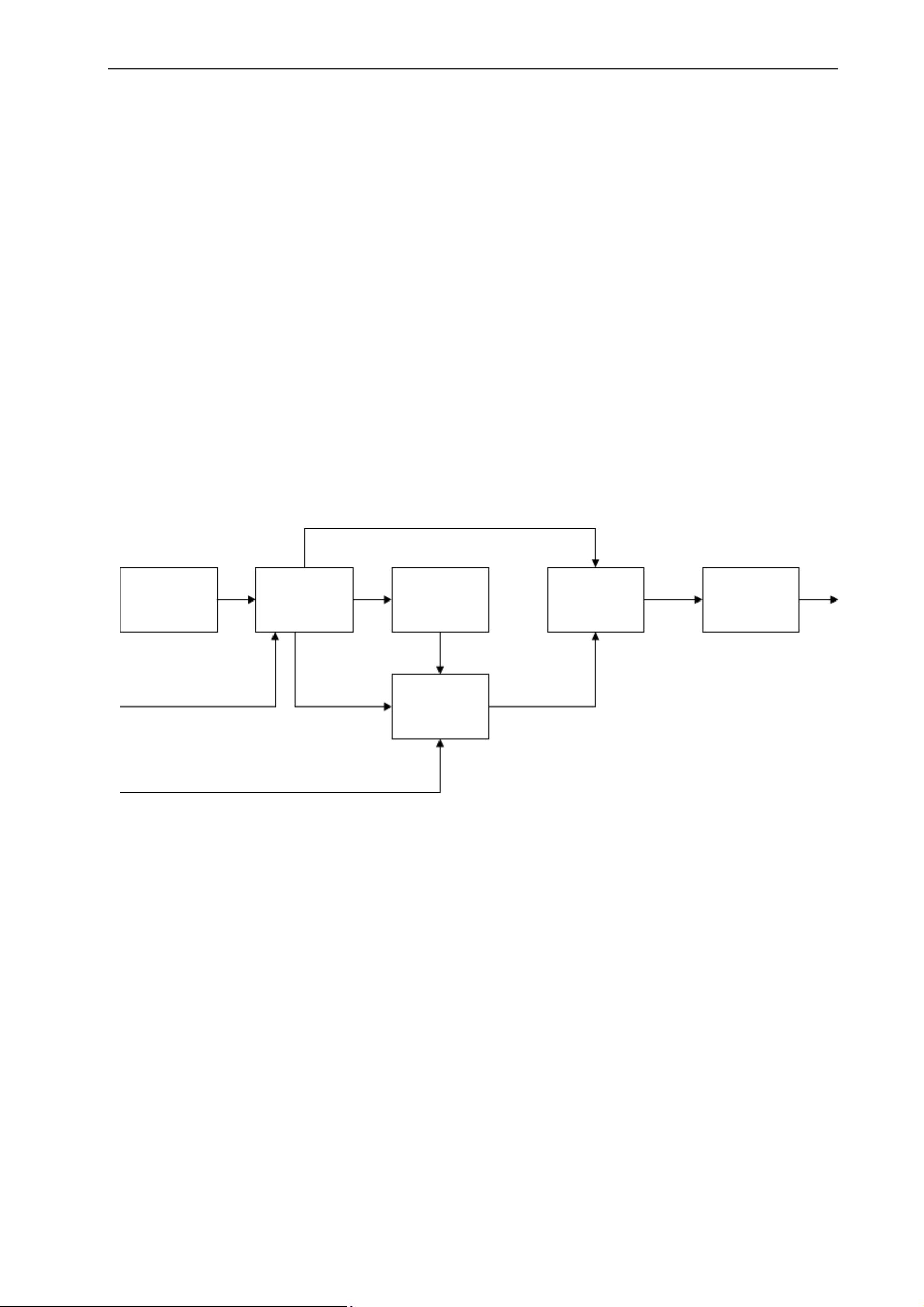

本文详细解析了直接数字频率合成(DDS)技术,这是现代信号发生器的关键技术,它能够精确地生成和控制各种频率的信号。DDS通过将数字信号转换为模拟信号,提供了精确的频率控制,使得信号发生器能产生连续可调的波形。

接着,文章重点讲述了如何利用Verilog HDL设计DDS模块以及波形产生和调制模块。波形产生部分以正弦波为例,展示了如何生成基本的周期性信号;而固定波形如方波和锯齿波的生成,则展示了设计的灵活性和多样性。调幅模块则允许用户根据需要改变信号的幅度,实现对信号强度的动态控制。

最终,通过全面的系统仿真,验证了基于FPGA和DDS技术的函数信号发生器的有效性和性能。实验结果显示,这种设计不仅能够生成多种波形,而且具备方便的频率和幅度调整能力,显著优于传统信号发生器。这表明,采用FPGA实现的DDS函数信号发生器已经成功地突破了传统方法的局限,为现代测试环境提供了强大且灵活的解决方案。

本论文通过详细介绍FPGA、DDS技术和Verilog HDL的应用,展示了基于这些技术的函数信号发生器在提升测试效率和精度方面的巨大潜力,为相关领域的研发和实践提供了有价值的参考。

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

xxpr_ybgg

- 粉丝: 6737

- 资源: 3万+

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全