2011年VHDL数字系统期末复习指南:模块结构与关键知识点

需积分: 10 138 浏览量

更新于2024-07-30

2

收藏 1.09MB DOC 举报

VHDL是Verilog Hardware Description Language的缩写,是一种专门用于描述数字系统和可编程逻辑器件行为的高级硬件描述语言。这门课程的期末复习资料针对2011年6月21日的考试,涵盖了VHDL语言的基础知识以及数字系统设计的关键概念。

在第一部分,复习者需要理解VHDL模块的基本构成,它由实体说明和结构体说明两部分组成。实体说明(Entity)定义了一个模型的外部接口,即输入(ports)和输出,用以描述设计的抽象功能,就像一个黑盒,仅关注其输入输出。实体说明的典型格式包括实体名、端口声明和数据类型。

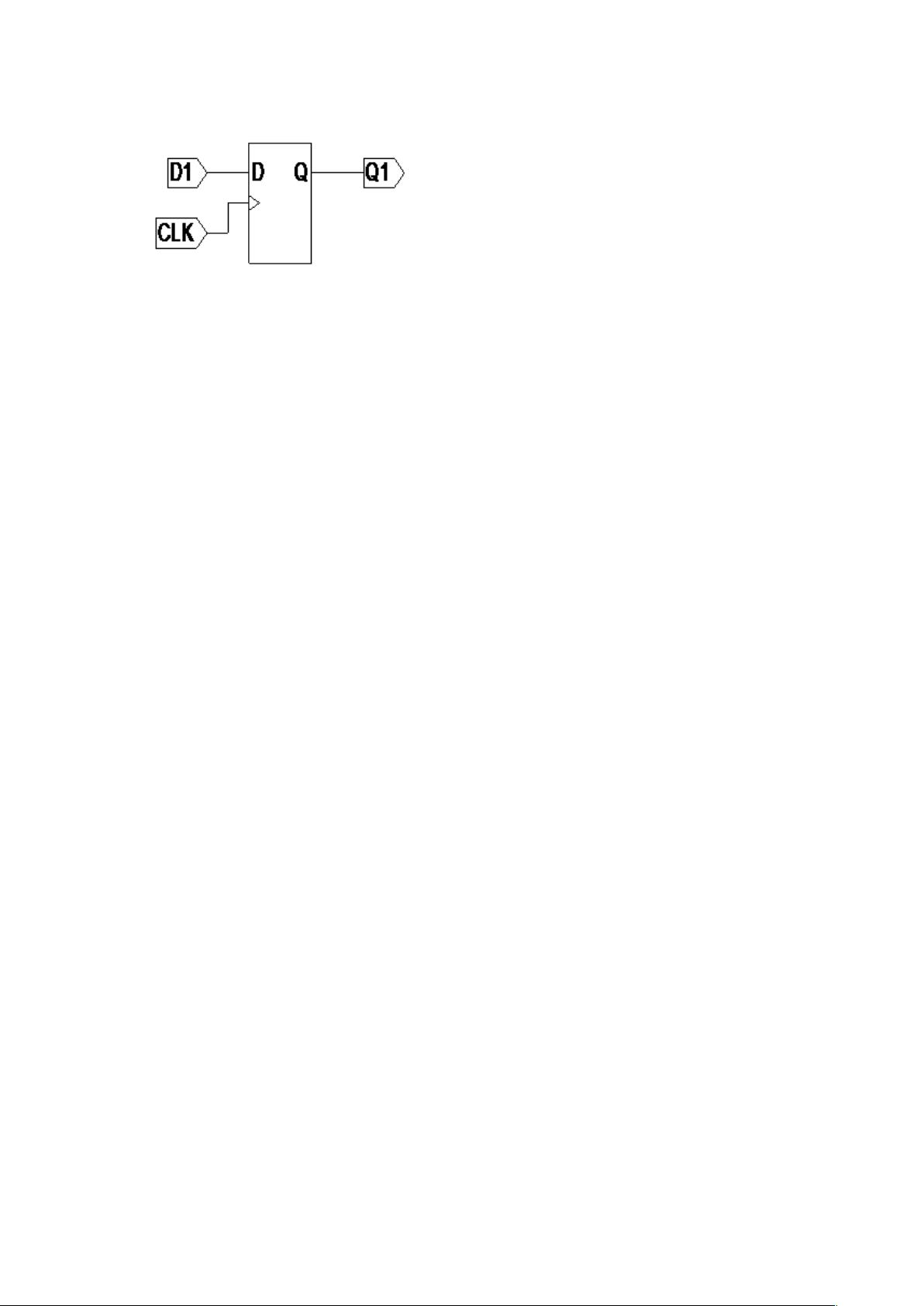

结构体说明(Architecture)则进一步定义了实体内部的逻辑实现,包括行为描述(描述信号如何随时间变化)、数据流描述(数据的流动和处理方式)和可能的结构描述(如使用顺序或并行流程)。此外,复习要点还包括VHDL语句的使用,惯性延迟和传输延迟的理解,以及如何通过习题2.2、2.7、2.16、2.19和2.44来巩固这些概念。

第二章介绍了可编程逻辑器件,区分了工厂可编程逻辑器件和现场可编程逻辑器件,并探讨了它们的组成部分。第三章重点在于系统设计中的状态机(SM)图和微程序,涉及数字系统设计的基本组成部分,如控制单元和数据单元,以及如何将SM图转化为VHDL代码。

第四章深入讨论了VHDL语言的高级特性,如过程和函数的区别、函数调用、属性语句和生成语句的使用,以及如何通过文本文件读取操作进行数据交互。第五章涉及硬件测试和可测试性设计,讲解组合逻辑电路的故障检测方法和IEEE1149.1测试访问端口。

第六章则是数字系统设计的实际应用,包括系统设计的要求、方案制定和模块设计,这些都是实际项目中必不可少的技能。

复习时,学生应重点关注实体和结构体的定义、数据对象(信号)的管理和时序分析、SM图在设计中的作用、VHDL高级语法的运用,以及硬件测试和设计案例的学习。通过本份复习资料和课堂讲解,考生可以更好地理解和掌握VHDL语言,为考试做好充分准备。

261 浏览量

136 浏览量

628 浏览量

261 浏览量

2024-11-30 上传

136 浏览量

147 浏览量

2010-04-08 上传

2024-11-30 上传

qiuyong123

- 粉丝: 0

最新资源

- ASP.NET+Access打造高效网络投票系统

- 以太坊Studio:官方IDE简化以太坊DApp开发与部署

- Java源码工具:读取和解压iOS IPA文件至当前目录

- 提升vim效率:winmanager插件使用教程

- 简约完美版漏雨屋日记本:在线签写与管理

- 清华java课件分享:全面提升编程能力

- 掌握C# ASP.net中ListBox控件的使用教程

- FbinstTool_v1.607:深入探讨menu.lst文件修改技巧

- Truffle插件自动化验证智能合约于Etherscan

- SnagIt 8.0:高效便捷的经典截图工具

- 掌握网络通讯抓包工具的五大关键技巧

- windlx模拟器及源代码使用教程大集合

- Flex打造火车站职工奖惩管理系统源码分析

- CSpect插件深度体验:ZX Spectrum模拟器的新工具与功能

- 路由器设置工具小助手V1.2:简易操作指南

- MATLAB数学建模应用详解:从基础到实践