VHDL入门:实体与构造体详解及基础组件设计

168 浏览量

更新于2024-07-15

收藏 1.38MB PDF 举报

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种专门用于描述数字系统行为的高级硬件描述语言。本文档深入解析了VHDL的基本概念和结构,重点讲解了实体(Entity)和构造体(Architecture)的概念,以及它们在设计硬件电路时的角色。

1. **实体(Entity)**:在VHDL中,实体是电路设计的基本单位,它定义了电路的输入和输出接口。实体由`Entity()`结构定义,包括实体名和一组端口(Port)。端口包括名称、方向(IN、OUT、INOUT、BUFFER、LINKAGE)和数据类型。IN信号是输入,只能被读取;OUT信号是输出,只能被赋值;INOUT信号既可以输入也可以输出;BUFFER用于存储数据,允许数据的读写;LINKAGE端口通常用于链接两个实体。端口的定义体现了电路的输入输出特性。

2. **构造体(Architecture)**:实体的实际功能和实现细节由对应的构造体描述。`Arcthitecture`结构定义了实体内部的逻辑结构,包括定义信号、常数、元件、数据类型、函数以及并行处理语句。例如,一个名为`STRUCT`的构造体会具体实现FULLADD实体的功能,可能包含并行执行的块(block)、进程(process)、函数和过程。

3. **其他设计单元**:

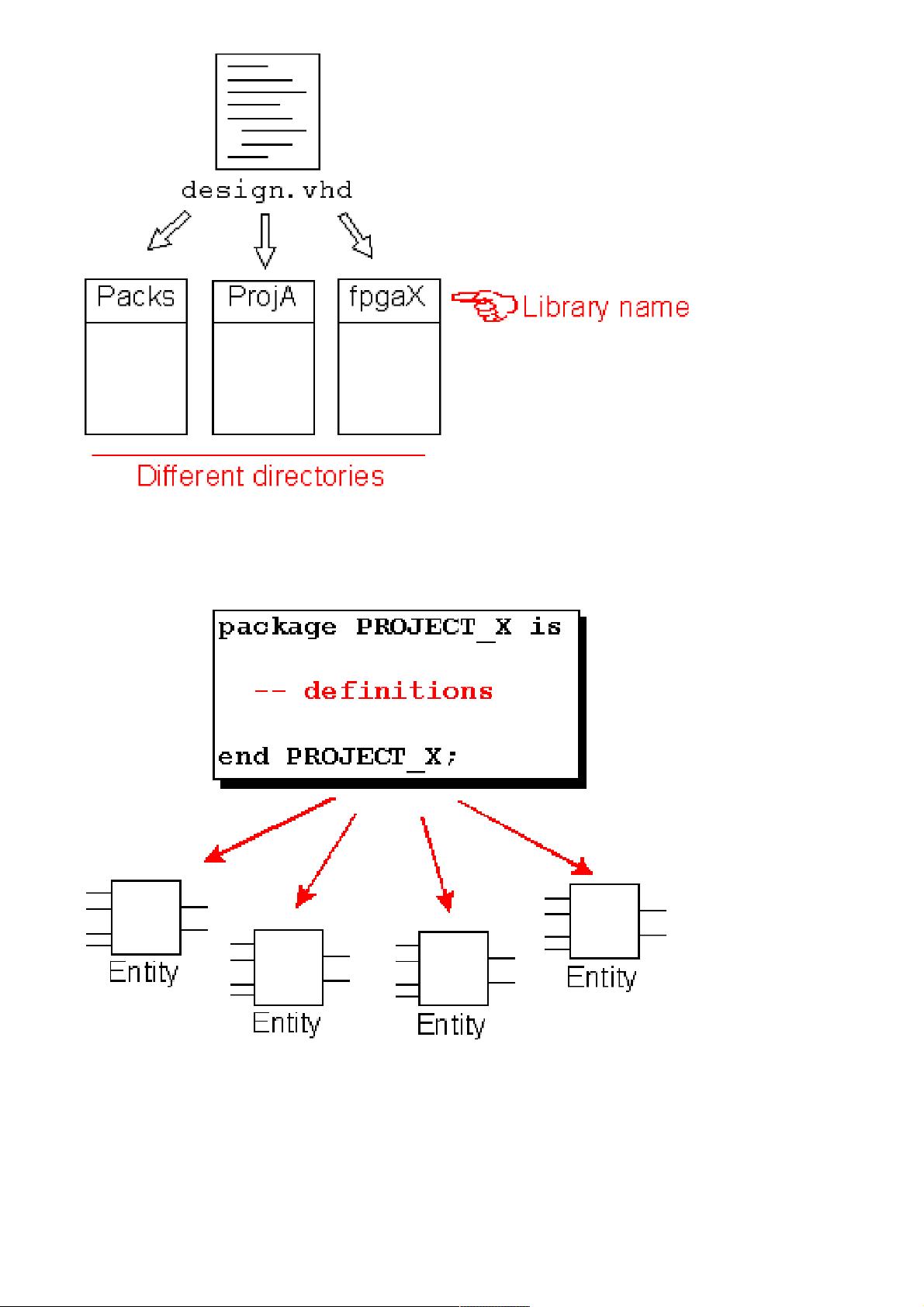

- Package(包):它是一个组织和复用代码的容器,可以定义信号、常数、数据类型、元件声明、函数和过程。Package可以进一步分为库级别的包(无独立端口)和包体(拥有独立端口)。

- Configuration(配置):描述了电路的配置信息,如实体与构造体的关联以及层与层之间的连接关系。

- Library(库):VHDL设计中的数据集合,包含标准库(如STD和IEEE)、面向ASIC的定制库以及用户自定义库。每个库都有其特定的逻辑名称和内容。

4. **对象、操作符和数据类型**:

- VHDL中的对象包括Constant(常量,只读)、Variable(变量,可读写)和Signal(信号,可读写,延迟更新)。常量一旦定义就不能改变值,变量和信号则可以动态更新。

5. **实例化与编译**:在实际设计中,实体需要通过实例化与配置来与构造体关联,形成最终的可编译设计。整个设计过程中,包括库、包、实体、构造体等元素紧密协作,共同构建出完整的硬件描述。

总结来说,VHDL通过实体和构造体的概念,提供了一种系统的方法来描述数字电路的行为和结构。理解这些基本概念和语法结构对于学习和实践VHDL设计至关重要。在实际应用中,正确地运用包、库和配置管理可以提高代码的复用性和可维护性。

2009-08-19 上传

2021-10-07 上传

2023-09-18 上传

2024-01-21 上传

2023-12-13 上传

2023-09-07 上传

2023-04-28 上传

2023-07-31 上传

2023-07-04 上传

weixin_38711529

- 粉丝: 4

- 资源: 901

最新资源

- 社交媒体营销激励优化策略研究

- 终端信息查看工具:qt框架下的输出强制抓取

- MinGW Win32 C/C++ 开发环境压缩包快速入门指南

- STC8G1K08 PWM模块实现10K频率及易改占空比波形输出

- MSP432电机驱动编码器测路程方法解析

- 实现动静分离案例的css/js/img文件指南

- 爱心代码五种:高效编程的精选技巧

- MATLAB实现广义互相关时延估计GCC的多种加权方法

- Hive CDH Jar包下载:免费获取Hive JDBC驱动

- STC8G单片机实现EEPROM及MODBUS-RTU协议

- Java集合框架面试题精讲

- Unity游戏设计与开发资源全集

- 探索音乐盒.zip背后的神秘世界

- Matlab自相干算法GUI界面设计及仿真

- STM32智能小车PID算法实现资料

- Python爬虫实战:高效爬取百度贴吧信息