VHDL实现的8位RISC-CPU设计与仿真

"基于VHDL语言的8位RISC-CPU设计,涉及RISC架构分析,VHDL设计,以及使用MAX+PLUSⅡ进行时序仿真验证功能。"

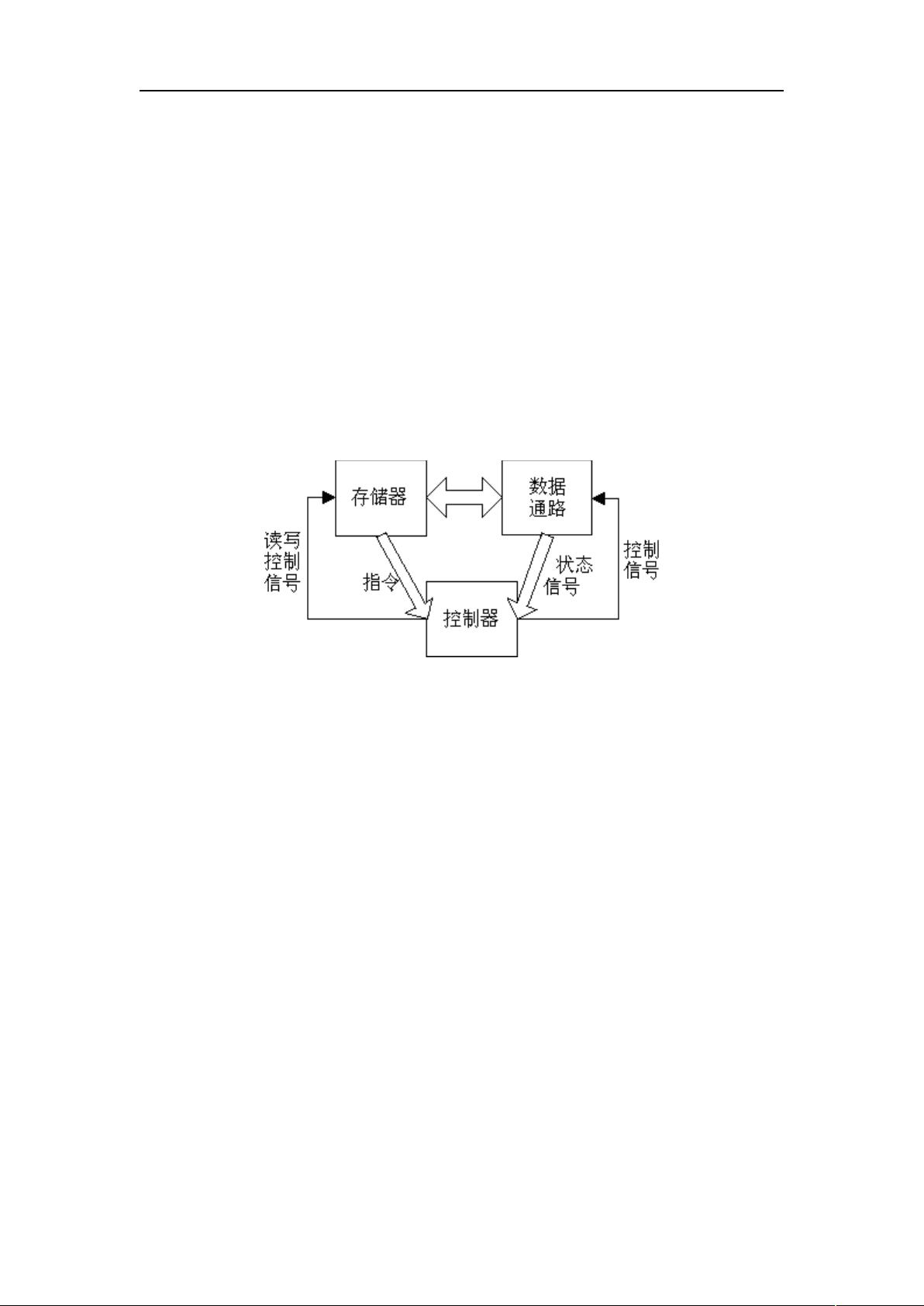

本文主要探讨了使用VHDL语言设计8位RISC-CPU的过程,这是计算机硬件设计领域的一个重要课题。RISC(精简指令集计算机)是一种优化的处理器设计哲学,其核心思想是通过减少指令集的复杂性来提高处理器的执行效率。与传统的CISC(复杂指令集计算机)相比,RISC-CPU通常具有更简单的指令集,更高的时钟频率,以及更小的电路规模。

8位RISC-CPU的设计涵盖了多个关键组件,这些组件构成了CPU的基础架构:

1. **时钟发生器**:为整个系统提供同步时钟信号,确保所有操作在正确的时间进行。

2. **指令寄存器**:存储当前正在执行的指令,为解码和执行过程提供输入。

3. **累加器**:用于临时存储计算结果,是算术逻辑单元中的重要组成部分。

4. **算术逻辑单元(ALU)**:执行基本的算术和逻辑运算,如加法、减法、逻辑与、逻辑或等。

5. **数据输出控制器**:管理数据从CPU到外部存储器或I/O设备的传输。

6. **地址多路器**:根据指令和CPU状态选择正确的内存地址,允许数据访问。

7. **程序计数器**:保持下一条要执行指令的地址,确保程序的顺序执行。

8. **状态控制器**:管理CPU的状态标志,如进位、溢出、零值检测等,这些标志用于控制程序流程。

在设计过程中,作者利用了VHDL这一硬件描述语言,它允许工程师以一种结构化的方式描述数字系统的逻辑行为。VHDL使得设计可以被综合成实际的电路,便于在FPGA(现场可编程门阵列)或ASIC(应用专用集成电路)上实现。

为了验证8位RISC-CPU设计的正确性,使用了MAX+PLUSⅡ软件平台进行时序仿真。这是一个常用的EDA(电子设计自动化)工具,可以模拟硬件设计在实际运行时的行为。通过仿真,可以观察到指令执行的波形,确保每个阶段的操作都符合预期,从而确认CPU功能的正确性。

最后,设计结果表明,8位RISC-CPU不仅成功实现了预定的功能指标,还在运行效率上有所提升,这证明了RISC架构的优势以及VHDL作为设计工具的有效性。关键词包括RISC-CPU、VHDL、MAX+PLUSⅡ、IP软核(可重用的知识产权核)和时序仿真,这些都是现代数字系统设计中的关键技术。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-04-04 上传

234 浏览量

2023-06-22 上传

2021-10-07 上传

2009-05-12 上传

2021-03-29 上传

wzc1992916

- 粉丝: 0

- 资源: 1

最新资源

- c代码-条件练习集合

- matlab由频域变时域的代码-eureca_face:EuRECA2021短期项目

- rsm

- 大三上学期实训——学生成绩管理系统,java后台,SpringMVC框架,mysql数据库.zip

- 14Oct_BatchProject:14Oct_Python批处理带有完整代码的Django网站项目

- modelo-tcc-uefs-ieee:模版乳胶Para Tratraho deConclusãode Curso de Engenharia daComputaçãoUniversidade Estadual de Feira de Santana-UEFS

- TestAssignmentForAndroidInternship

- QQ空间导出助手插件QZoneExport.zip

- cpp代码-165.4.6.3

- kafka-logsize-exporter:Python prometheus client for kafka logsize(Prometheus基于kafka logsize监控)

- hq9plus-in-perl6:用Perl 6编写的hq9 +解释器

- 基于Java的学生成绩学分制管理系统.zip

- dom4j-1.6.1.zip

- Metals_Mapping_GAM:使用广义添加剂建模进行预测性金属映射

- cpp代码-161.4.3.2

- ema-john-simple