VHDL实现多功能数字钟设计及仿真

需积分: 9 82 浏览量

更新于2024-09-21

收藏 177KB DOC 举报

"这篇文档是关于使用VHDL设计多功能数字钟的教程,涵盖了设计要求、硬件需求、设计方案以及具体的设计实现。设计包括时、分、秒计数显示,清零,小时和分钟调整功能,并有整点报时。硬件核心是EPF10K10LC84-4芯片,配有六个数码管和三个按键。设计通过秒计数、分计数、小时计数、报警、时间设置和译码等模块来实现,所有计数基于BCD码。"

在VHDL中设计一个多功能数字钟是一项综合性的任务,涉及到多个模块的协同工作。这个设计首先明确了设计要求,包括24小时循环计时、清零、调整时间和整点报时。硬件基础是EPF10K10LC84-4 FPGA芯片,配合六个数码管用于显示时间,一个时钟信号输入,以及三个按键用于清零、调整小时和分钟。

设计方案采用了自顶向下的设计方法,将系统分解为六个主要模块:秒计数模块、分计数模块、小时计数模块、报警模块、时间设置模块和译码模块。每个模块负责特定的计数或控制功能。计数过程均基于二进制编码十进制(BCD)码,以确保准确无误地显示十进制数值。

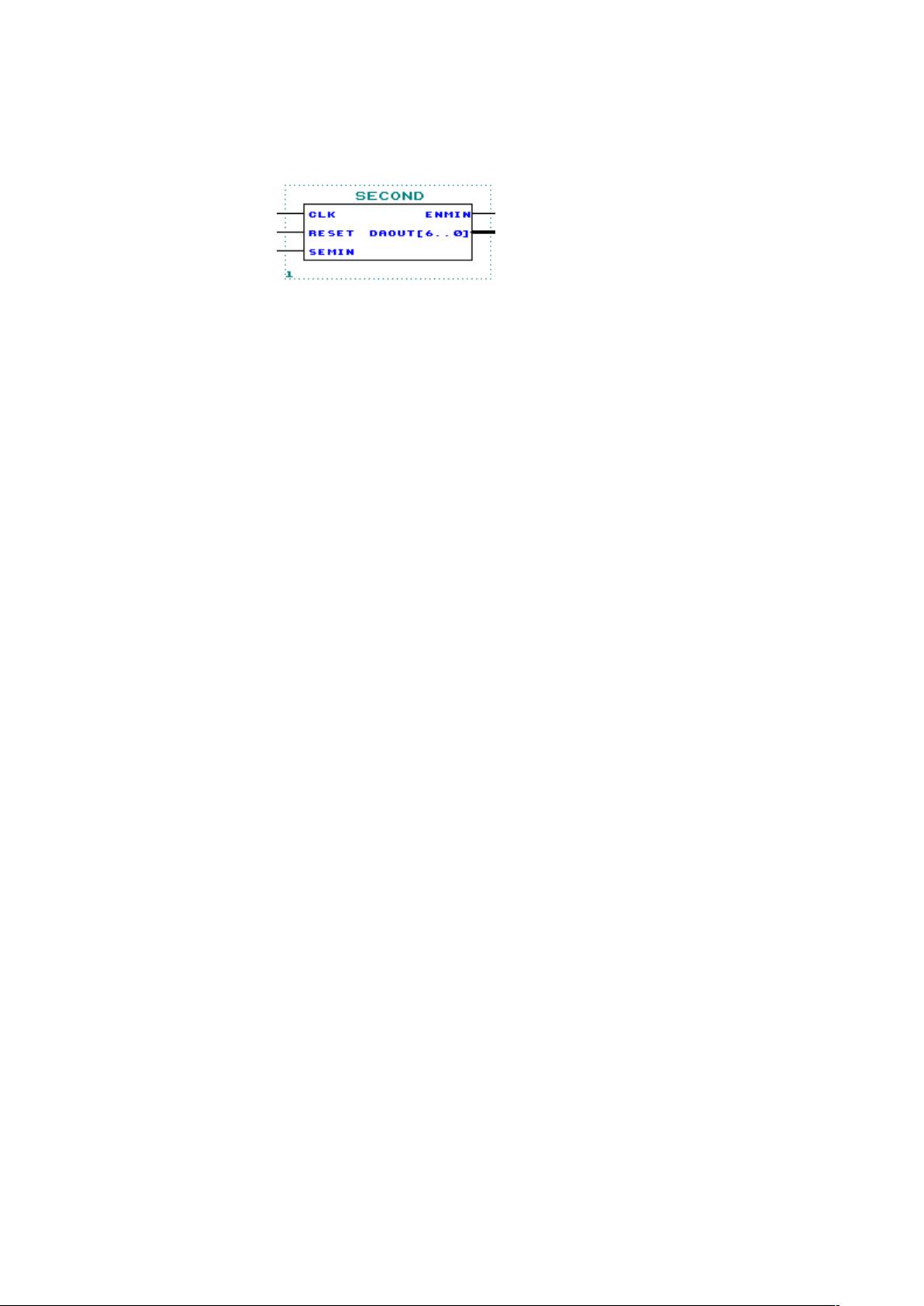

秒计数模块是整个系统的基础,其VHDL代码展示了如何处理时钟脉冲和复位信号。在这个过程中,当秒计数达到59(16#60#),会触发分计数器更新,并清零秒计数。同时,还包含了一个条件语句来处理分钟和小时的调整。

分计数模块和小时计数模块的工作原理类似,每当相应的计数器满值时,它们会触发上一级的计数器。报警模块则负责实现整点报时功能,可能通过点亮特定的LED或者产生声音信号。

时间设置模块允许用户通过按键来调整小时和分钟,而译码模块的作用是将BCD码转换为适合数码管显示的格式,确保时间正确地在显示屏上呈现。

这个VHDL多功能数字钟设计不仅展示了数字逻辑设计的基本原理,还演示了如何利用VHDL实现复杂的时序逻辑系统,是学习FPGA设计和VHDL编程的一个优秀实例。设计者需理解每个模块的功能,以及它们如何通过VHDL代码进行交互,才能成功实现这样一个多功能的数字钟。

2010-11-29 上传

2019-01-14 上传

2010-12-28 上传

2010-01-06 上传

2008-12-02 上传

2010-01-06 上传

2010-01-06 上传

2009-09-17 上传

点击了解资源详情

zzm3999

- 粉丝: 1

- 资源: 2

最新资源

- 简洁的中国画背景中国风下载PPT模板

- BioBioChile-crx插件

- Nucleotide-Sequence-generator:随机DNA:dna:核苷酸生成器和反向互补查找器:microscope:

- 2_displacement_strain_analysis

- python学习

- Convolution:该程序找到两个离散序列的线性卷积-matlab开发

- Ejercicio2-LluviaPalabras-Java

- Python库 | viztracer-0.3.1-cp37-cp37m-manylinux2010_x86_64.whl

- kdmhmfrshx

- 行业分类-设备装置-电机转子嵌绝缘纸机.zip

- mysql-5.7-linux安装包及安装过程

- Earthworm-Web.github.io:这是Earthworm-Web的后台管理存储库

- 绿色田园风光自然风景下载PPT模板

- Better Eenadu E-Paper-crx插件

- plotmultix(varargin):绘制具有多个 x 轴的图-matlab开发

- Saltar Modal de La Nación-crx插件