VHDL实现的数字时钟设计与分析

版权申诉

107 浏览量

更新于2024-06-26

1

收藏 1.76MB PDF 举报

"基于VHDL的数字时钟设计"

这篇文档主要介绍了如何使用VHDL设计一个数字时钟,涵盖了数字时钟的工作原理、设计任务、系统总体方案设计、VHDL模块电路设计以及仿真与调试过程。

1. 数字时钟的工作原理

数字时钟的核心是通过计数器来实现时间的递增。它由3个主要部分组成:秒计数器(60进制)、分计数器(60进制)和小时计数器(24进制)。秒计数器以1Hz的频率工作,由高频率的晶振信号分频得到。每当秒计数器到达最大值(59秒),会触发进位信号,推动分计数器增加;同样,分计数器满59分钟后也会推动小时计数器。当小时计数器达到23时59分59秒,会重置为0,开始新的一天。此外,系统还提供中断信号给CPU(如NIOS),用于更新和显示时间。

1. 设计任务

设计任务要求实现以下功能:

a) 在七段数码管上连续显示时、分、秒。

b) 实现进位机制,即个位满十进一,十位满五进一,小时按照24小时制计数。

c) 整点报时,通过扬声器在整点时发出声音。

d) 时间设置,允许通过按键手动调整秒和分,同时支持清零和暂停功能。

e) LED灯循环点亮,与时钟计数同步。

2. 系统总体方案设计

设计采用自顶向下的模块化方法,底层模块用VHDL编写,顶层通过原理图进行集成。设计包含7个底层模块:秒、分、时计数器,按键去抖动模块,按键控制模块,时钟分频模块和数码管显示模块。

3. VHDL模块电路设计

- 分频模块(pinlv):生成1Hz的时钟信号。

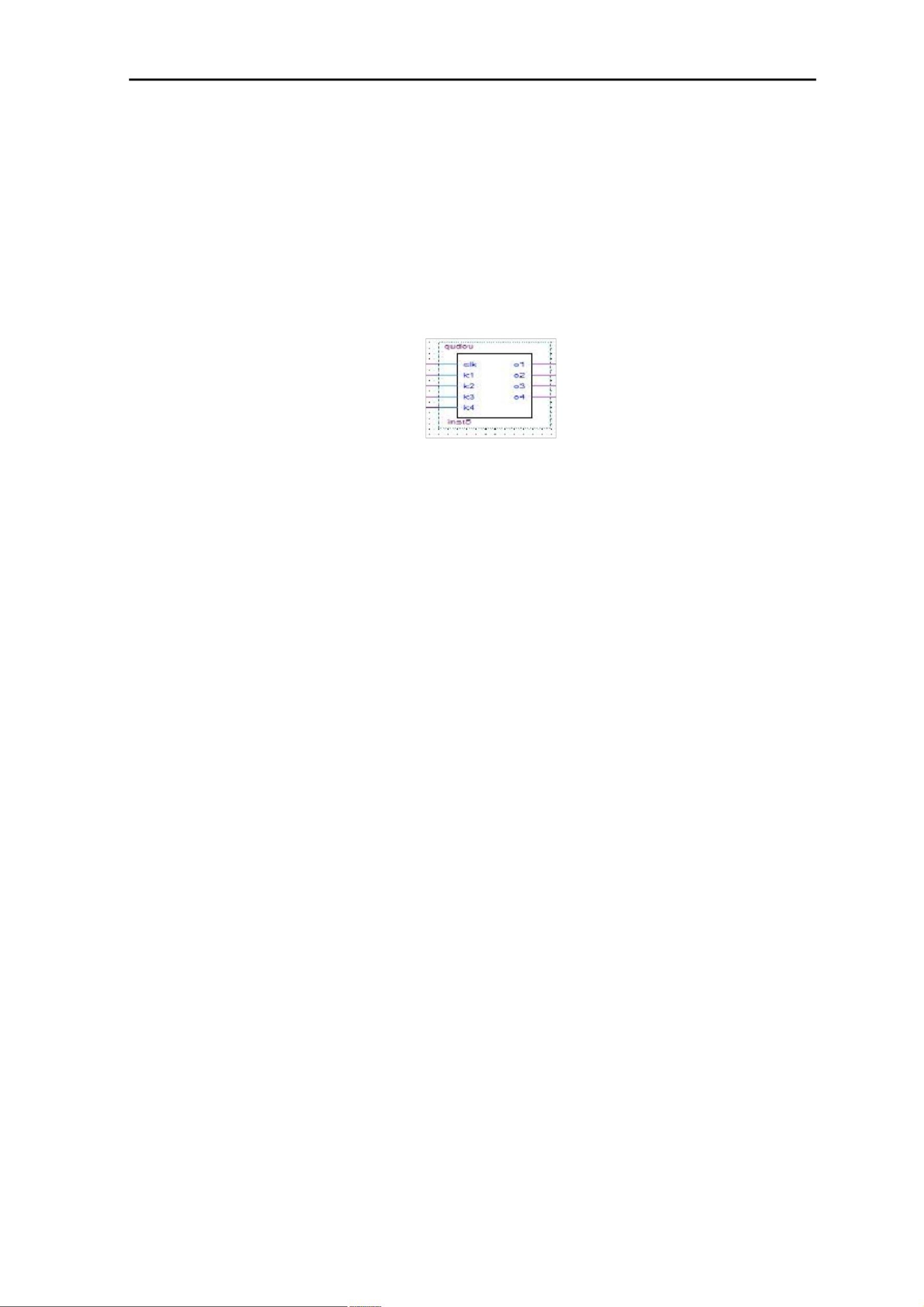

- 去抖动模块(qudou):处理按键输入,消除快速连续按下产生的抖动。

- 按键控制模块(self1):解析按键输入,实现时间设置和控制功能。

- 六十进制转换模块(cantsixty):处理秒和分的进位逻辑。

- 时计数模块(hourtwenty):实现24小时制计数。

- 组合模块:整合秒、分、时的计数结果,准备显示。

- 数码管显示模块:将计数结果转换为七段数码管可显示的形式。

4. 仿真与调试

这部分涉及数字时钟的系统级仿真,以验证各模块功能的正确性,并进行必要的调试,确保所有功能符合设计要求。

总结,该文档详细阐述了一个基于VHDL的数字时钟设计,涵盖了从基本工作原理到具体实现的各个层面,提供了清晰的模块划分和设计流程,是学习VHDL和FPGA设计的实用案例。

2022-07-04 上传

2023-05-21 上传

124 浏览量

2023-04-27 上传

140 浏览量

102 浏览量

247 浏览量

hhappy0123456789

- 粉丝: 76

最新资源

- 初学者的在线编辑器小插件案例

- UIAlertController自适应弹窗与内存使用调用教程

- 深度学习中的nf_distillation技术:核心知识提纯与应用

- 清华大学课程设计:32位RISC Cache流水线CPU设计与仿真

- 品红项目:基于JSP技术的宣传网站与信息管理

- CDH6.3.2环境下集成Flink1.13 parcel包指南

- SE2实习软件项目:前端演示与前端开发更新

- 电子应用开发资源合集:awesome-electron

- 全面覆盖多领域物理单位转换工具

- 泛微E-cology E8版Java二次开发Jar包解析

- Kubernetes部署前的准备动作指南

- 全新版大学英语综合教程4压缩包解析与学习指南

- 如何实现模仿Google的拖拽网页布局

- Unity3D游戏开发教程全集:6本必读指南

- Android开发必备:7款实用源码应用下载

- 基于WebRTC的浏览器内容分发网络协调器