Xilinx ISE中MODELSIM仿真入门教程

MODELSIM仿真是一种广泛应用于Xilinx ISE工具集中的关键技术,它旨在帮助初级硬件开发者理解和设计数字电路的行为。本文档详细介绍了MODELSIM仿真过程,包括以下几个主要知识点:

1. **概述**:

MODELSIM是Xilinx提供的一个高级别硬件描述语言(HDL)仿真器,用于验证Verilog或 VHDL设计。它允许开发人员在实际硬件实施前测试和调试逻辑设计。

2. **技术流程**:

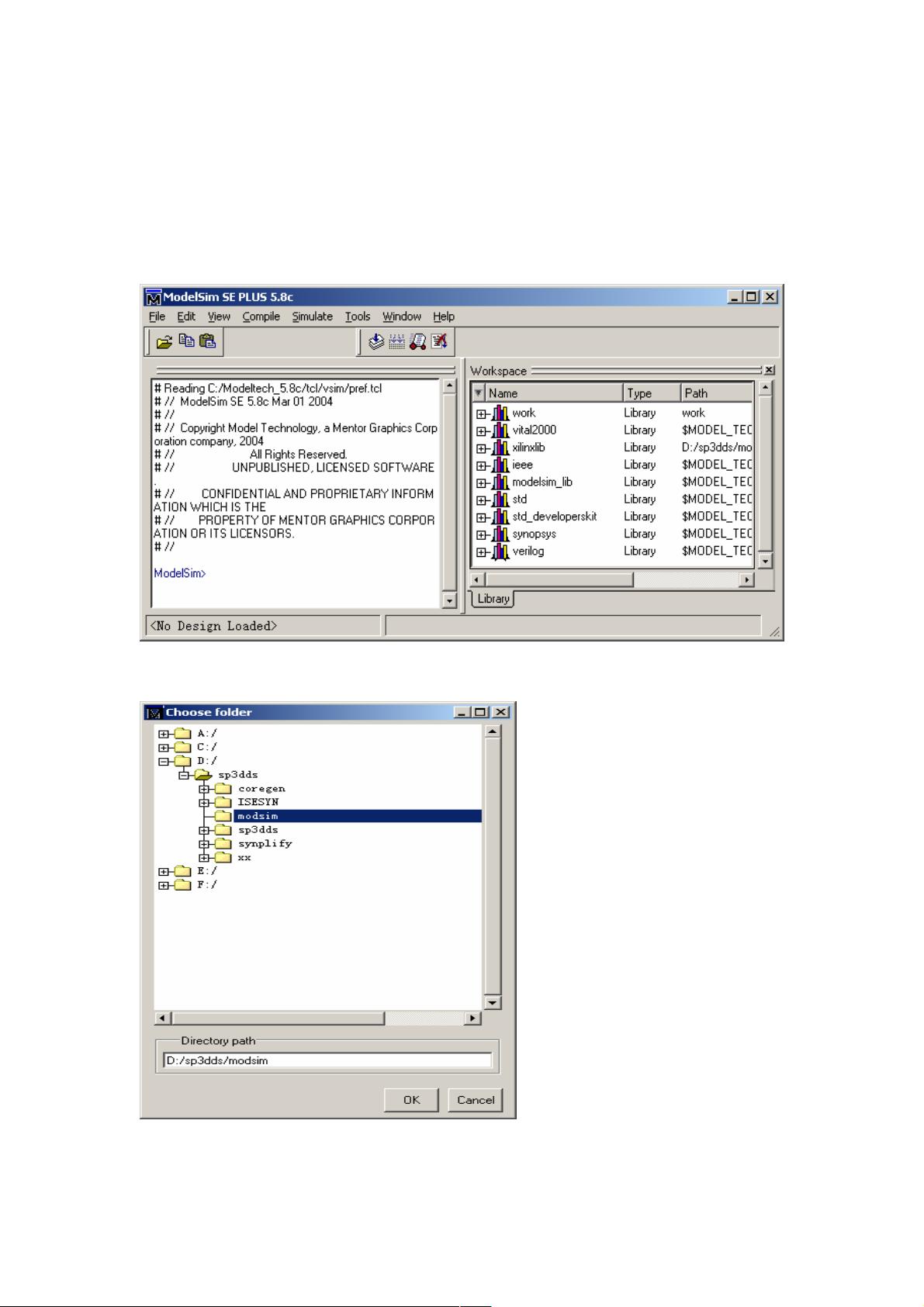

- **项目初始化**:创建新项目,设置WORKSPACE和LIBRARY。

- **设计导入**:将XILINX IP CORE(如IPB)添加到项目中,并确保库文件正确加载。

- **源代码管理**:使用VHDL或Verilog编写设计,遵循COMPLIETHISFILE和COMPILE步骤确保代码合规。

- **编译和综合**:通过MODELSIM的编译功能,将VHDL或Verilog源代码转化为可模拟的电路模型。

- **设计集成**:将设计集成到主设计中,如定义寄存器和信号连接(如wire GSR, GTS)。

- **设置测试bench**:创建一个测试环境来驱动设计并观察其行为,通常包含模拟输入和断言(ASSERT)语句。

- **仿真执行**:使用simulate命令启动仿真,检查设计是否按照预期工作。

3. **特定操作**:

- **变量声明与赋值**:例如,声明wire类型的GSR和GTS,以及reg类型的GSR_int和GTS_int,用于处理模拟信号和状态机。

- **逻辑连接**:使用assign语句弱连接GSR和GTS,这可能涉及到硬件级别的复用。

4. **错误处理**:

在仿真过程中,可能遇到“dOK”和“dNOT OK”状态,表示仿真成功或失败,这提示开发者检查和修复错误。

5. **IP CORE管理**:

对于IP CORE的集成,使用ADD指令将其包含到项目中,并确保连接到正确的ST3XILINX库。

6. **调试技巧**:

提供了如何使用wire和reg变量进行调试的示例,以及弱连接(weak)的概念,有助于模拟信号在仿真中的处理。

通过这篇文章,初学者可以掌握MODELSIM在Xilinx ISE工具链中的应用,从设计创建、代码编写到调试的整个流程,从而提高硬件设计和验证的效率。

117 浏览量

128 浏览量

919 浏览量

2022-09-23 上传

146 浏览量

点击了解资源详情

点击了解资源详情

187 浏览量

650 浏览量

bingyu1942

- 粉丝: 0

最新资源

- 编程技巧:从新手到专家的进阶指南

- 基于.NET 2.0的面向对象编程基础指南

- Ubuntu环境下配置GNU交叉工具链arm-linux-gcc 3.4.4

- 深入探索Bash Shell脚本编程指南

- 十天精通C#版ASP.NET实战教程

- OSWorkflow 2.8 中文手册:工作流深度解析

- Hibernate入门与实战指南

- Bindows用户手册:构建富Web应用程序

- 数据库系统概论第四版答案详解

- 探索MATLAB中创新的俄罗斯方块新玩法

- C语言编程关键概念与技巧解析

- Hibernate 3.2官方文档详解:入门与配置

- 设计模式解析:从简单工厂到抽象工厂

- UML与设计模式:理解和应用

- Java高级成像编程指南

- JAVA面试:BS与CS模式深入解析