Verilog HDL深度解析:硬件描述语言教程

下载需积分: 5 | PDF格式 | 1.73MB |

更新于2024-07-23

| 18 浏览量 | 举报

"本资源为Verilog HDL的超详细讲解教程PDF,涵盖了数字信号处理、计算、程序、算法及硬线逻辑的基本概念,旨在帮助读者深入理解和掌握Verilog HDL这种硬件描述语言,用于描述数字系统的结构和行为。教程可能涉及Verilog的发展历史、语法特性、设计流程以及在 FPGA 和 ASIC 设计中的应用。"

Verilog HDL是硬件描述语言的一种,它允许工程师以文本方式描述数字系统的结构和功能,类似于电路图、逻辑门以及复杂的逻辑功能。Verilog HDL与VHDL一起,是全球最常用的两种HDL,它们在20世纪80年代中期被开发出来,其中Verilog最初由Gateway Design Automation公司创建,后来被Cadence公司收购。

在数字信号处理领域,Verilog HDL扮演着关键角色。教程的开篇介绍了数字信号处理的基础,包括滤波、变换、加密解密等操作,这些都是基于数学运算的。这些运算可以由计算机或微处理器完成,但某些实时或高精度的需求则需要专用硬件系统,比如FPGA或ASIC。在非实时应用中,通用计算机可以处理大部分数字信号处理任务,例如在石油地质探测中,数据可以经过后期处理,时间相对宽裕。

然而,对于实时或超高速的信号处理任务,例如军用通信和雷达系统,通用微处理器因执行速度和灵活性限制无法满足需求。这种情况下,就需要用Verilog HDL设计专用的硬线逻辑电路,以确保在严格的时序约束下完成运算。与通用微处理器不同,硬线逻辑不依赖于指令执行和内存访问,而是直接通过预先定义的逻辑门阵列进行并行处理,因此速度更快。

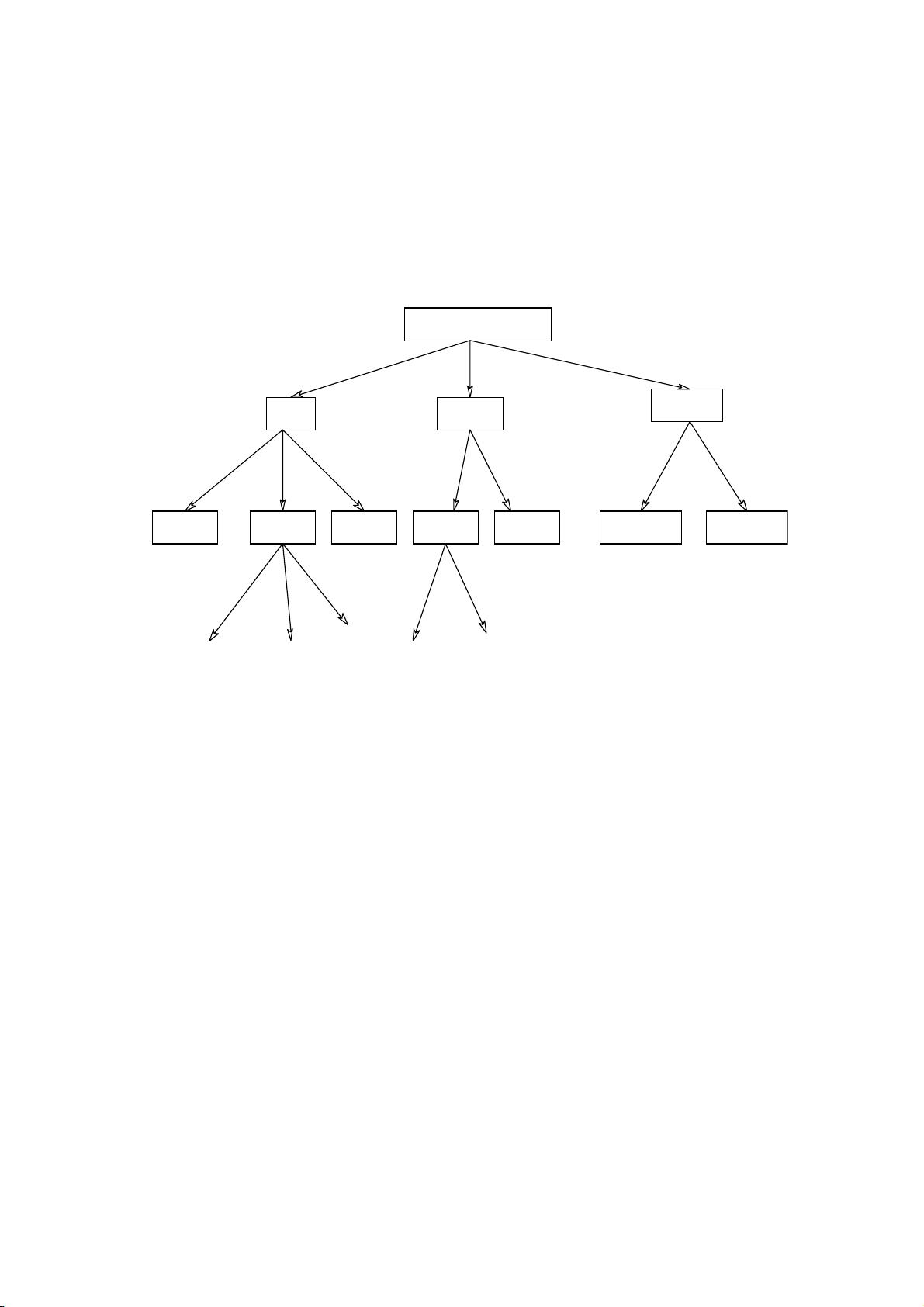

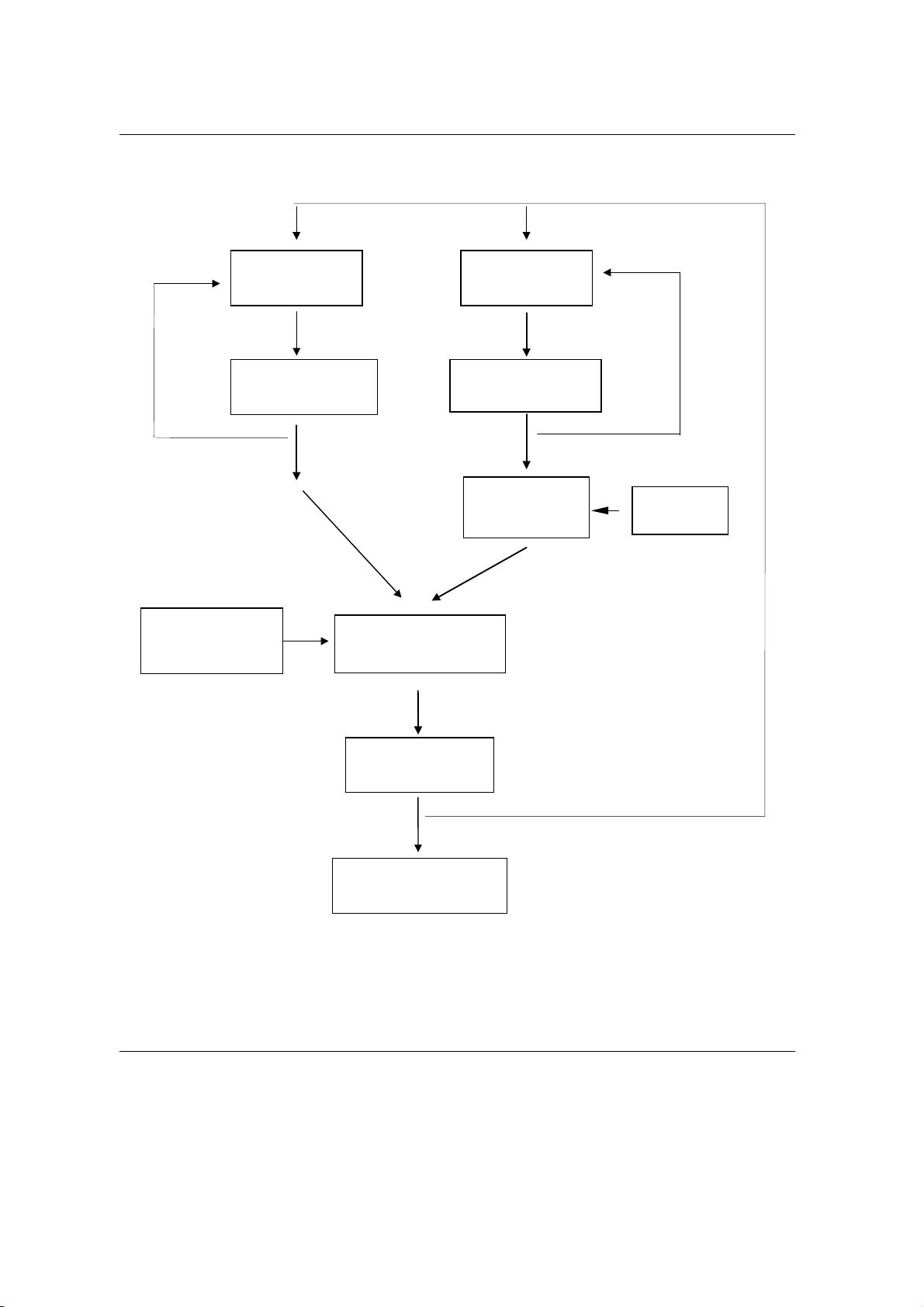

Verilog HDL教程将深入探讨如何使用该语言描述和实现这些复杂的逻辑操作。它将涵盖基本语法、模块定义、并行和顺序语句、接口设计、仿真验证以及综合流程等方面。通过学习,读者能够掌握设计数字系统的基本方法,包括创建IP核、进行系统级建模和验证,并了解如何将Verilog设计转化为实际的硬件实现。

这个Verilog HDL详细教程适合电子工程、计算机科学和相关领域的学生、工程师以及研究人员,旨在提供全面的知识,帮助他们在数字系统设计中运用Verilog HDL这一强大的工具。通过学习,读者不仅可以理解数字信号处理的基本概念,还能熟练运用Verilog HDL进行硬件设计和优化。

相关推荐

sinat_15914713

- 粉丝: 0

- 资源: 5

最新资源

- StudentManagement:JAVA+MySQL数据库设计完成的学生管理系统,界面使用的Java Swing

- 凡诺企业网站管理系统PHP版-PHP

- Unity独数游戏《sudoku-2017》

- Github-Trending-Repos-Android-App:一个基于Github api的Android应用,可根据创建日期显示趋势仓库

- 重量计算器

- lathe-firmware

- 2016 bctf exploit bcloud 400.rar

- 电脑软件一键禁用WIN10自带更新和杀毒.rar

- Auto Union Type.c Tab-crx插件

- ScreenToGif.2.17.1.Setup.msi

- easyapi:for面向人类的概念验证API生成器

- nodeDatagram

- angular-user-search-github::pencil_selector:简单的Angular-CLi应用程序搜索github用户

- jQuery基于CSS3文字动画特效特效代码

- omnetpp-5.5.1-src-windows.zip

- BabyShop:一个简单的电子商务网站,我们可以在其中租用一些婴儿用品。 有关更多信息,请浏览自述文件