Verilog层次设计:彩灯控制器详解与实现

版权申诉

本篇文档主要介绍了关于西南交通大学电子工程实验中的一个项目——彩灯控制器的设计与实现。首先,实验的预习思考题旨在引导学生对即将进行的实验有一个初步的理解和思考。接下来,关键部分包括:

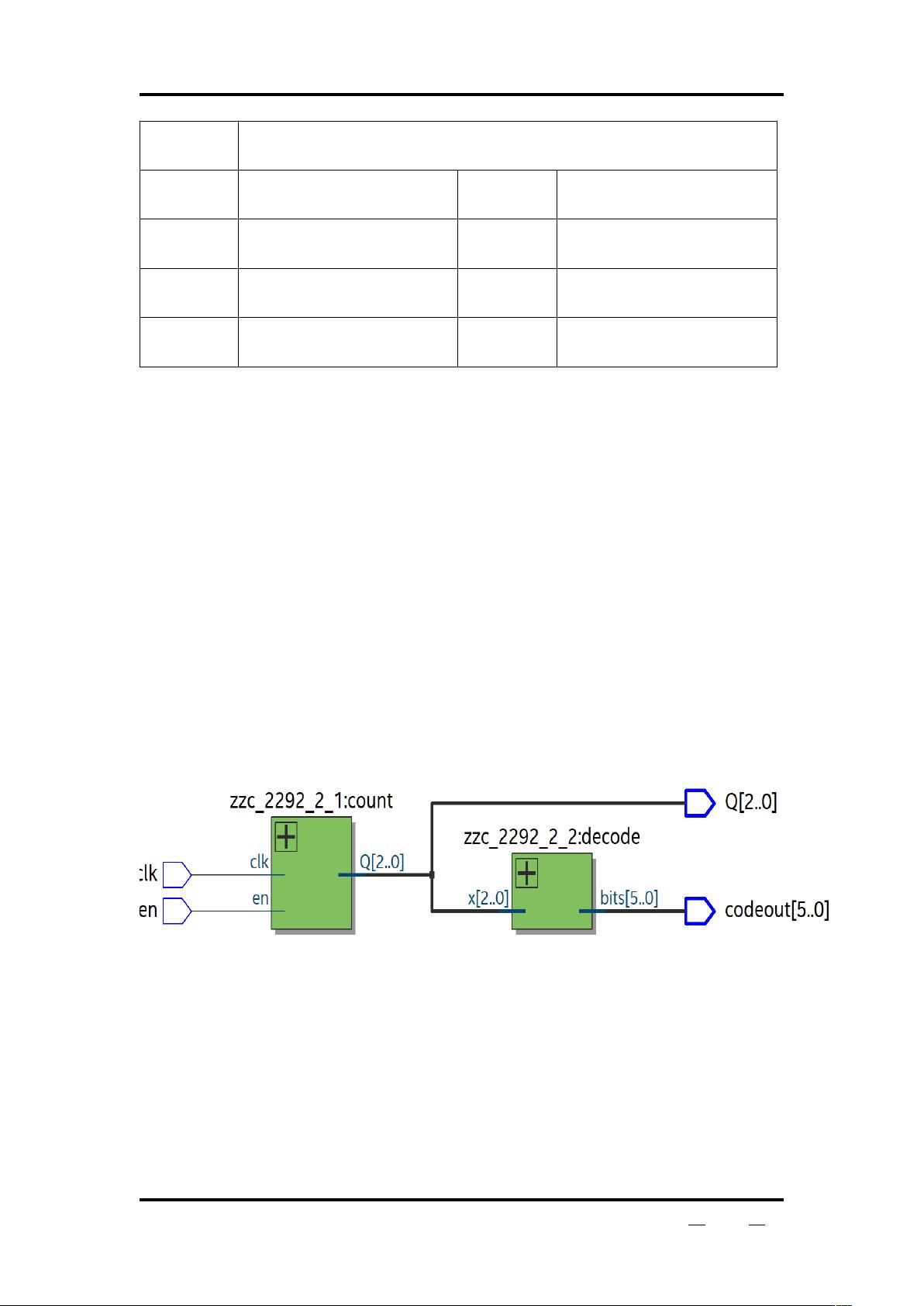

1. 实验电路图:这是一个Verilog模块设计,包含`zzc_2292_2`模块,它接受时钟信号`clk`、使能信号`en`以及控制信号`Q`和`codeout`。该模块内部还包含了两个子模块,`zzc_2292_2_1`作为计数器,用于根据`en`信号控制Q的状态变化;`zzc_2292_2_2`作为译码器,根据输入的`Q`值生成相应的`codeout`代码。

2. 状态图:展示了模块之间的工作状态转换,有助于理解整个系统的逻辑流程,比如计数器何时启动和停止,以及译码器如何响应不同的输入值。

3. 流程图:通过图形化的方式展示计数器和译码器的操作步骤,直观地展现了系统的工作原理,即根据输入的编码信号,计数器逐位递增,当计数达到特定值时,触发译码器生成相应的彩灯控制信号。

4. 程序代码:给出了核心模块的详细Verilog代码,包括计数器和译码器的实现,以及`zzc_2292_2`模块的整体结构。代码中使用了条件语句和案例结构,展示了数据处理和逻辑运算的具体实现。

5. 仿真波形图:这部分展示了通过仿真得到的电路行为,包括输入和输出信号的时间序列,便于理解和验证电路的正确性。

6. 引脚分配表:列出了电路中信号的实际连接,以便于在实际硬件上进行布局,确保信号传输的准确无误。

7. 实验现象及原始数据记录:记录实验过程中观察到的灯亮模式和输入输出数据,作为后续数据分析的基础。

8. 实验数据整理与分析:对收集的数据进行统计和分析,可能包括不同代码输入对应的实际灯效,以及可能存在的误差或异常情况。

9. 遇到的问题与总结:在实验过程中遇到的困难,解决方案,以及实验后的反思和学习心得,这些都能帮助学生提升实践能力和问题解决能力。

10. 报告模板说明:明确了报告的结构和格式要求,强调了实验前后各个环节的完成时间,并提醒可能需要添加附页的情况。

在整个过程中,层次化的文件设计方法使得整个彩灯控制器的设计和调试变得清晰且易于管理,这对于理解和掌握数字逻辑设计的基本原理和实践操作具有重要意义。

2022-07-01 上传

2009-09-10 上传

2010-05-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-05-14 上传

2010-03-04 上传

六不过不改

- 粉丝: 22

- 资源: 56

最新资源

- ema-for-mei-js:TypeScript中MEI的EMA实现(同构)

- cplusplus-helloworld:这是我的第一个C ++项目

- ng-bootstrap-loading:角度页面的加载蒙版显示功能

- johaneous.github.io:韦伯斯特无删节词典(免费的En-En-Cht词典)

- 超级万年历记录时间过程与节气,纪念日的C++版本的实现

- api-cng

- 基于Docker的MySQL+Bind9-dlz一主多从高可用DNS方案.zip

- node-webapp-step1:用于学习外语学习网络应用程序开发

- CalDash:CS294 Web应用程序

- 个人档案袋:个人档案库

- quickplot:这是quickplot模块的测试版,是pandas,matplotlib和seaborn的包装,用于快速创建漂亮的Viz进行分析

- DlvrMe-API

- azuredemoapp

- test2-solutions:CMP237 测试 2 实践解决方案

- emsi-devops:这是霍尔伯顿学校项目的资料库

- Finite-State-Machine-Model:延续2018年夏季开始的项目,其中Graeme Zinck和我在Ricker博士的带领下制作了Finite State Machines的专业模型,以实施理论并为正在进行的研究提供了试验平台。 允许生成FSM,并执行多项操作(例如“产品”和“并行组合”),并且目前已集成了U结构以用于进一步分析。 目前正在为Mount Allison大学的Ricker博士开发此工具。