2023 ISSCC: 1.8GHz 12b Pre-Sampling Pipeline ADC with Reference ...

需积分: 2 55 浏览量

更新于2024-06-26

2

收藏 50.08MB PDF 举报

在2023年的国际固态电路会议上(ISSCC),一篇题为"A1.8GHz 12b Pre-Sampling Pipelined ADC with Reference Buffer and OP Power Relaxations"的论文引起了关注。这篇研究专注于设计和实现一款高性能的12位pipeline ADC(逐次比较型模拟到数字转换器),其工作频率达到1.8GHz,旨在满足下一代6G通信系统对高速和低噪声信号处理的需求。

首先,论文的动机部分强调了在快速发展的无线通信技术背景下,对于高速ADC的需求。1.8GHz的采样率使得该ADC能够在单个通道上提供足够的系统速度和信号噪声比(SNDR),这对于多路时间交织(TI)架构来说是至关重要的,因为这可以支持更高的数据传输速率而保持信号质量。

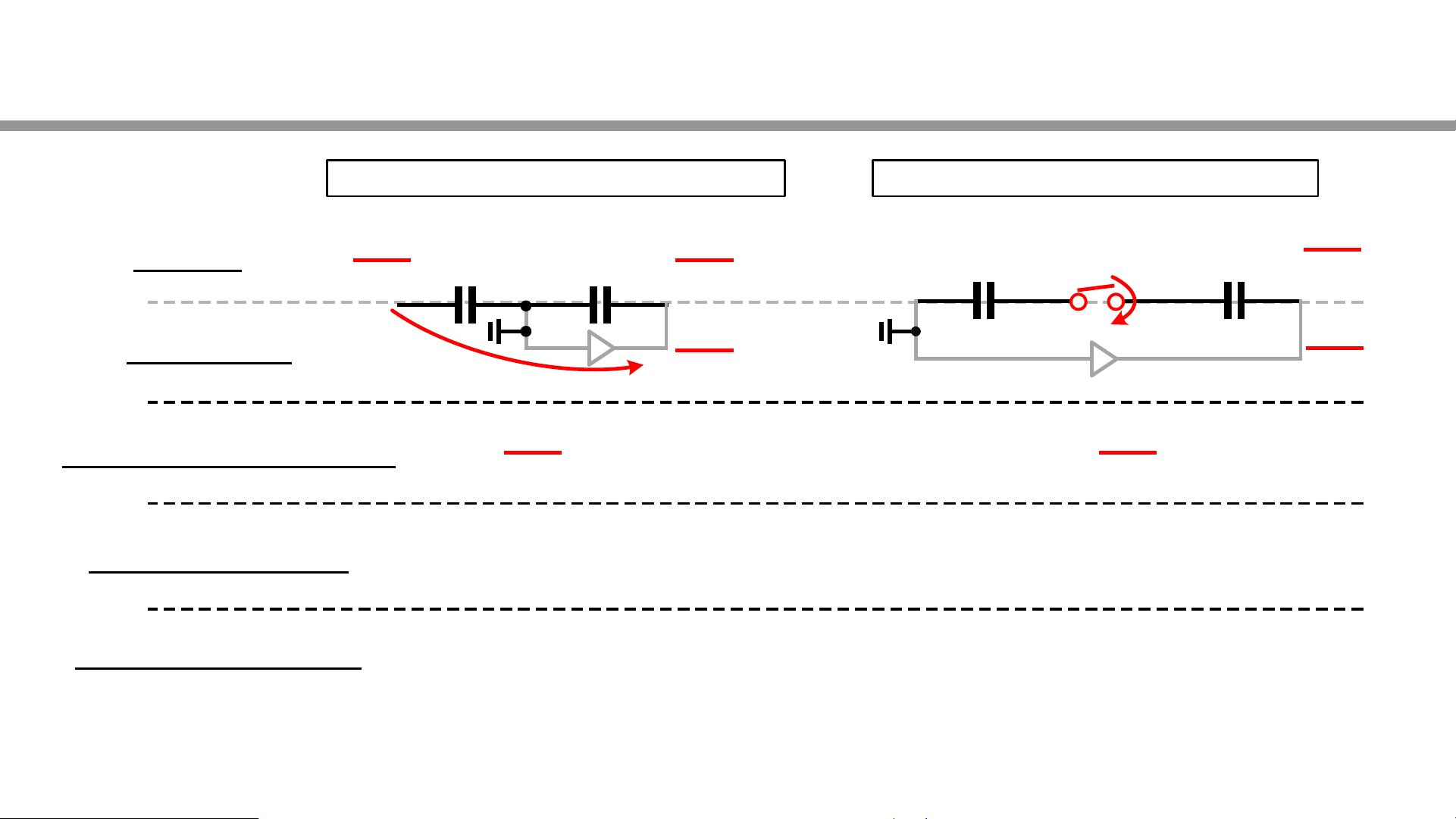

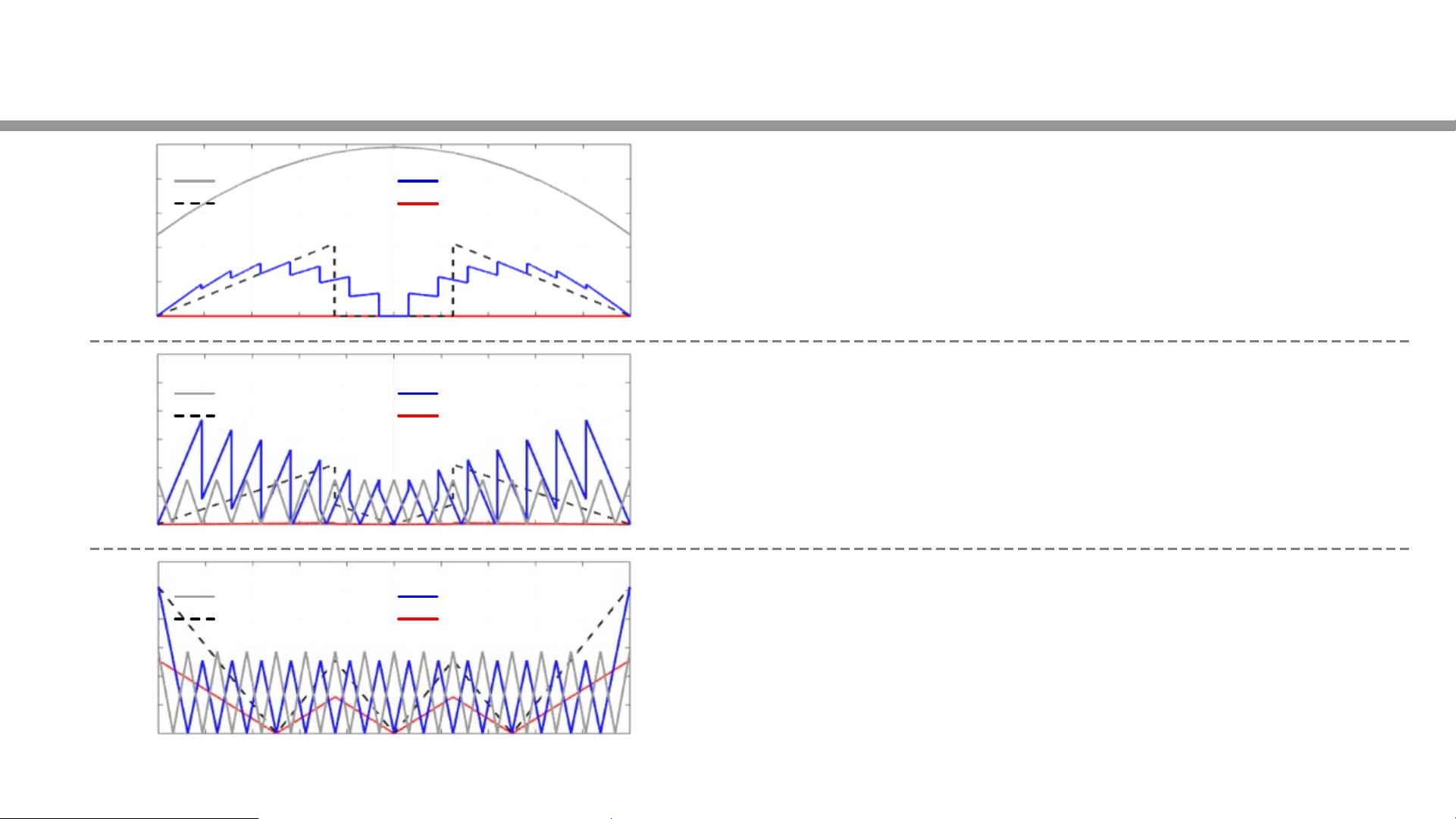

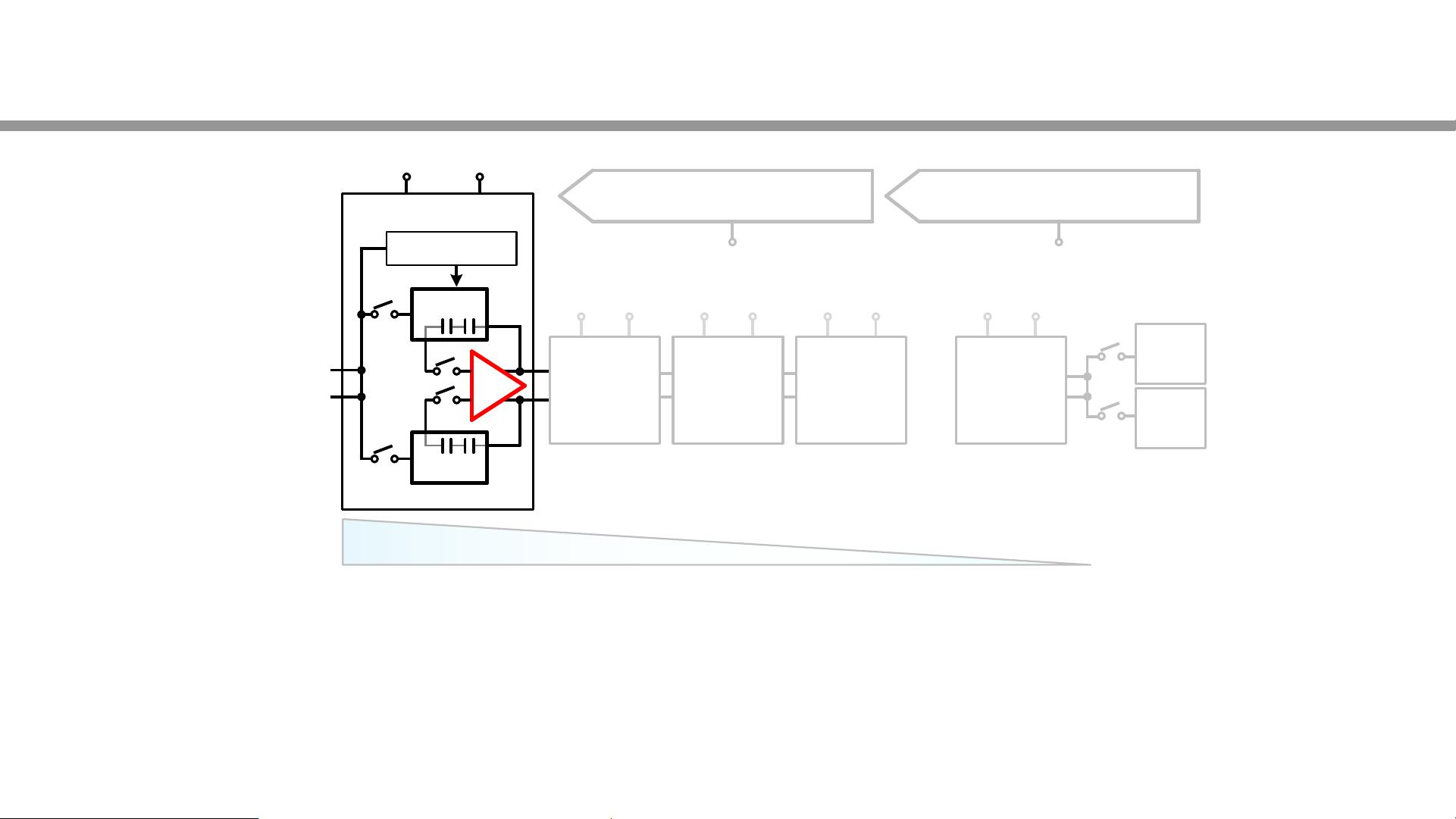

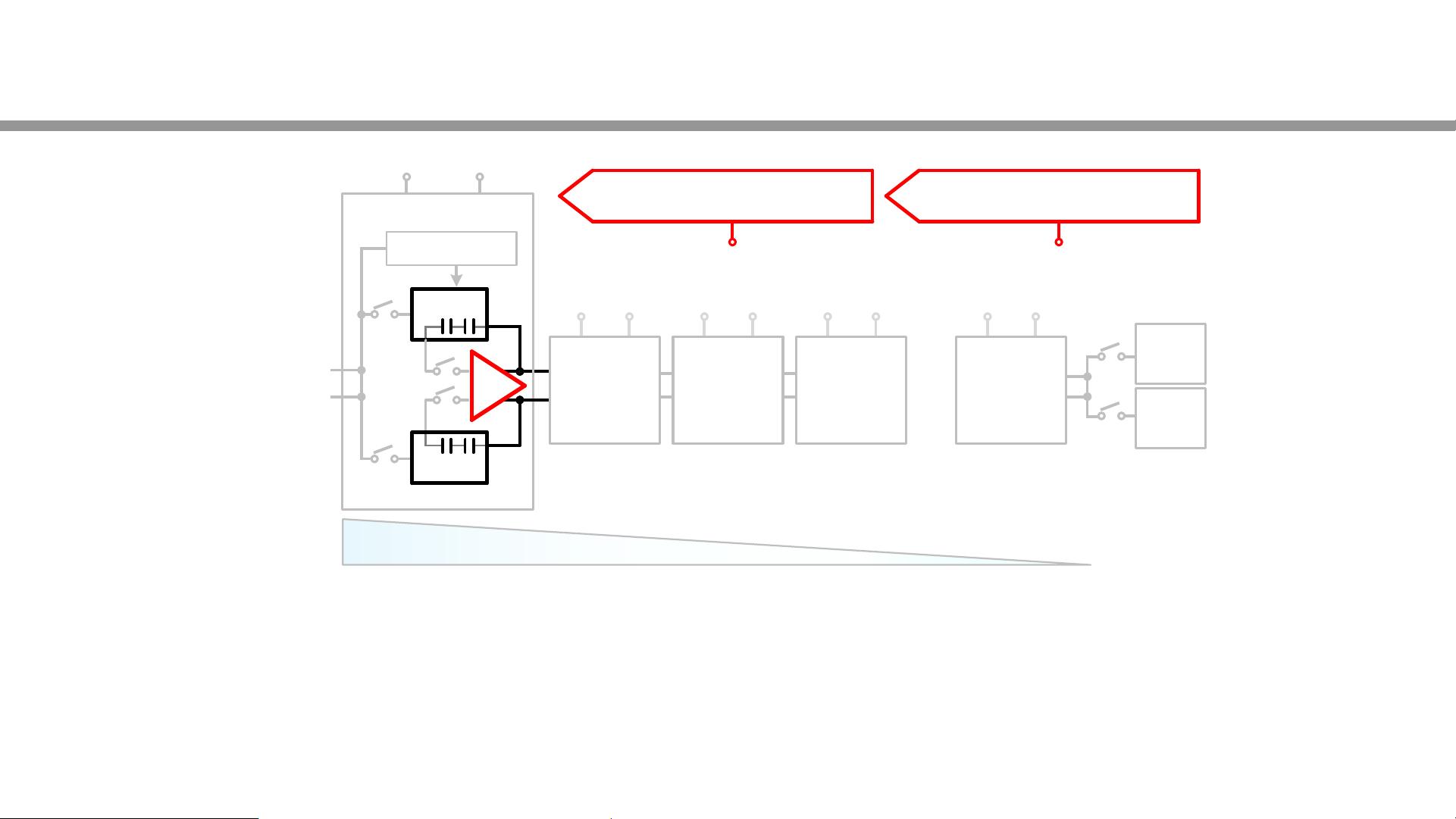

作者们采用了预采样pipeline架构,这种架构通过在转换之前进行预处理来提高转换效率。预采样ADC的特点是能够降低量化噪声,从而提升整体性能。为了进一步优化,他们引入了参考缓冲器,这有助于稳定输入信号并减少电源消耗。同时,他们还探讨了操作点(OP)功率管理策略,这在高压、高速应用中显得尤为重要,因为它能够在保证性能的同时,降低功耗。

论文的实施部分详细介绍了设计过程,包括电路的详细结构、模块化设计以及关键元件的选择。这可能涉及到模拟前端、数字前端、以及模数转换器核心部分的设计优化。测量结果显示了该ADC在实际应用中的性能,包括线性度、信噪比、功耗等关键指标,并进行了与现有SAR( Successive Approximation Register)架构和其他低噪声闭合反馈pipeline ADC的对比。

结论部分总结了研究的主要发现,讨论了他们的设计如何在速度和效率之间取得了良好的平衡,以及它在实际应用中如何优于竞争者。此外,论文还可能对未来的研究方向和挑战提出了思考,比如如何进一步减小功耗或提高集成度,以适应不断增长的系统需求。

ISSCC2023的这篇论文展示了一项前沿的12位1.8GHz预采样pipeline ADC设计,其通过创新的参考缓冲和操作点功率管理,为满足6G通信的高速、低噪声需求提供了关键技术。它不仅提供了详细的技术实现,还展示了在高性能ADC设计领域的最新进展和挑战。

387 浏览量

2023-03-16 上传

2023-03-16 上传

393 浏览量

2024-11-06 上传

2024-11-06 上传

2024-11-08 上传

2024-10-27 上传

2024-11-08 上传

netshell

- 粉丝: 11

- 资源: 185

最新资源

- RomeroHeavy

- kotlin-deep-copy-helper:轻松复制和修改不可变的复杂对象树。 通过序列化,具有杰克逊库

- UnidreamLED.zip

- fansky:饭斯基-第三方饭否客户端

- 易语言学习-WEB客户支持库2.3支持对json解析(支持静态).zip

- 15个家电图标 .sketch素材下载

- nodejs-examples:来自各种Node.js书籍的代码示例

- 好泰州分类信息网站

- HTML-QUIZ-Registration-Form:该存储库包含使用中级HTML标记创建的测验注册表单

- Renaissance

- 疲劳驾驶测试Demo.rar

- qt-读写HID库文件

- Navicat_Premium_15.0.16.rar

- pact-consumer-swift:用于创建协议的Swift ObjeciveC DSL

- RangeMedium

- 中国货源网址站