VHDL设计基础:第三章详解逻辑电路构建

需积分: 9 180 浏览量

更新于2024-08-01

收藏 1.79MB PPT 举报

本资源是关于VHDL编程语言设计基本逻辑电路的教程,针对VHDL语言的结构和应用进行了深入讲解。章节内容主要集中在以下几个方面:

1. **VHDL基础陈述总结**:这部分首先回顾了VHDL中的顺序赋值语句,如IF、CASE和LOOP,这些语句仅限于进程、过程和函数中使用,分别用于条件选择、循环控制和空操作。IF和CASE用于根据条件执行不同的行为,LOOP用于重复执行某段代码,而NULL则用于CASE语句中的空处理。

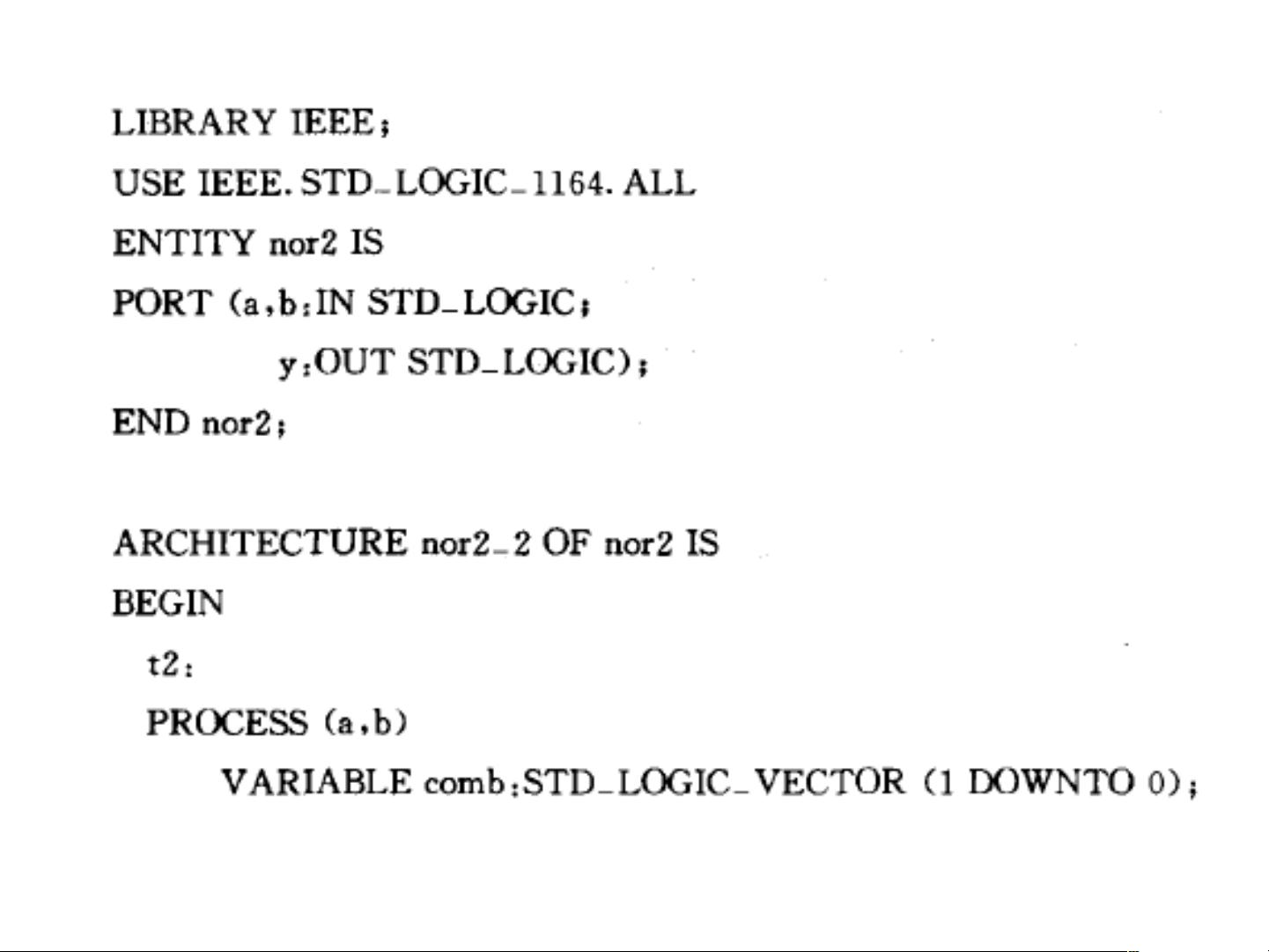

2. **并发赋值语句**:重点介绍了PROCESS语句,强调敏感信号表的重要性,以及如何通过WAIT语句处理无敏感信号的情况。BLOCK语句有助于提高代码的可读性。并行信号赋值语句包括简单信号赋值、WHEN…ELSE语句的选择结构,以及选择信号赋值的详细用法,通过例程展示了这些语句的实际应用。

3. **设计组件**:元素例化语句用于在层次化设计中引入和实例化预先定义的模块。生成语句则支持在指定范围内复制代码块,通常用于循环结构。

4. **子程序(Subprogram)**:VHDL中的子程序包括函数(FUNCTION)和过程(PROCEDURE)。函数接受参数并返回单个值,而过程可以返回零个或多个值,调用时作为一条语句。

5. **库和包(Library and Package)**:这部分讲解了如何利用VHDL的库和包管理功能,以便组织和重用代码,提高设计的模块化程度。

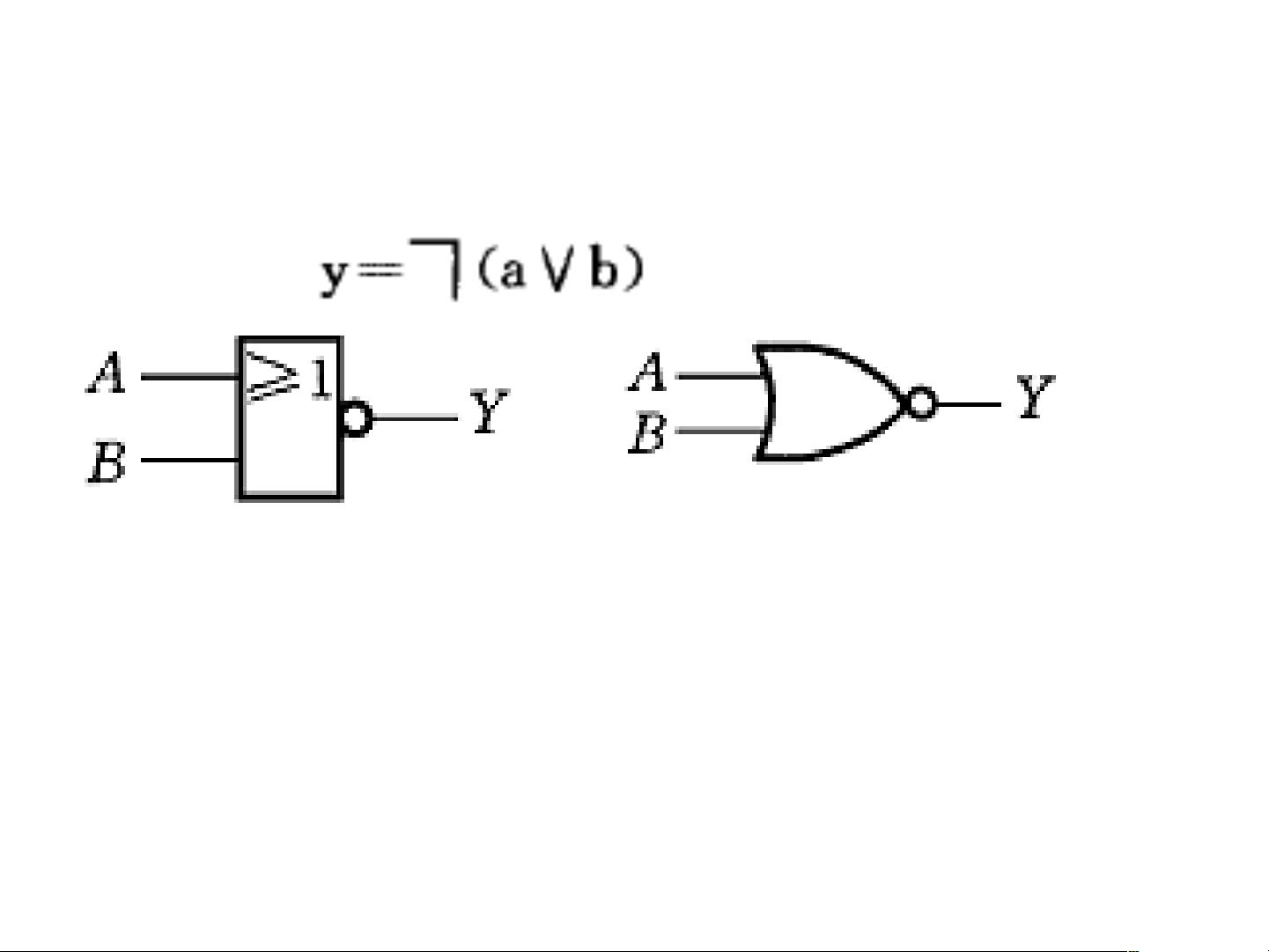

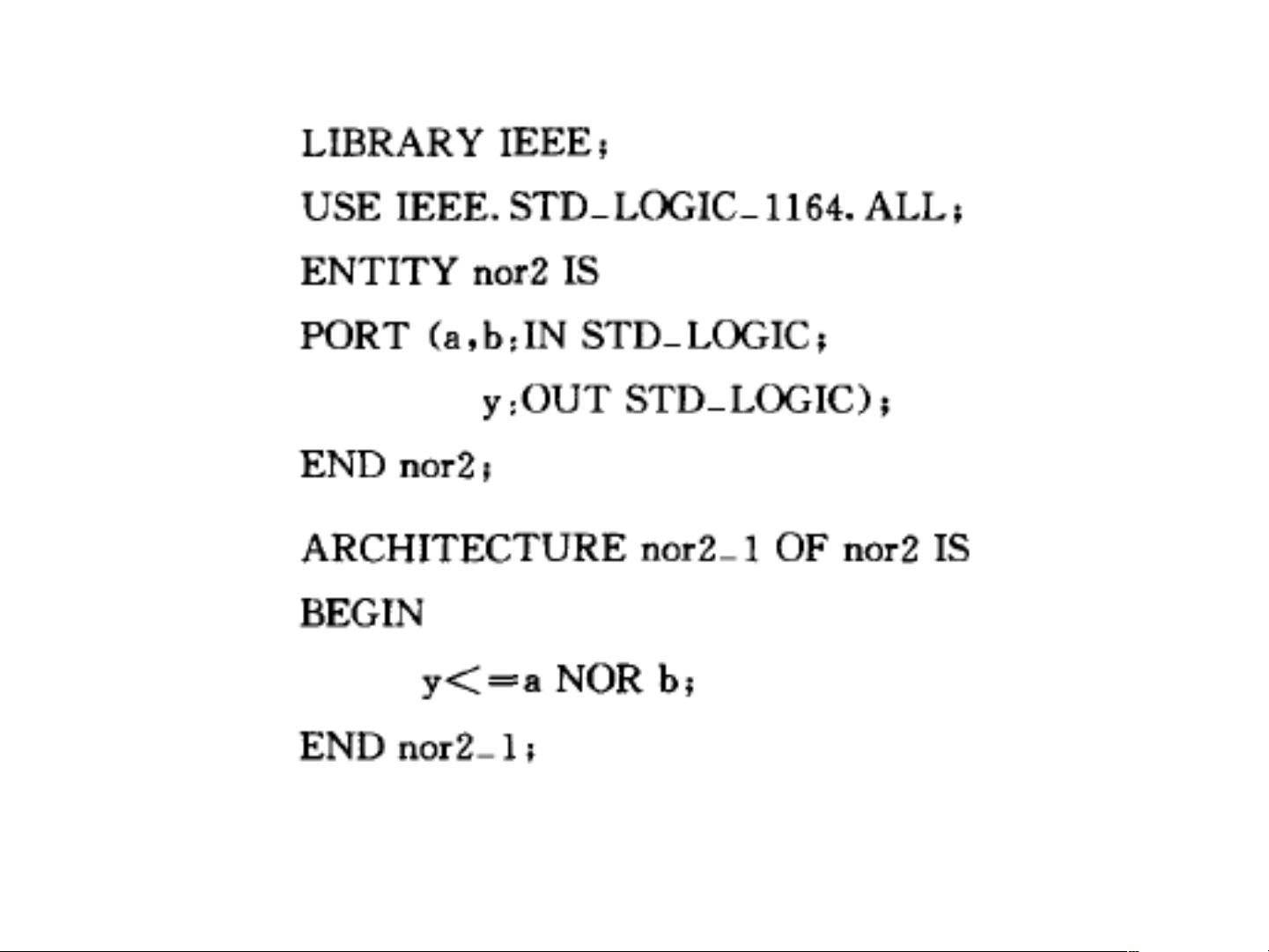

6. **VHDL应用于组合逻辑电路(Combinational Circuits)**:学习者在此阶段将所学应用于实际的逻辑电路设计,通过VHDL描述组合逻辑结构,例如门电路、编码器、译码器等。

通过这个章节,读者将深化对VHDL语言的理解,并掌握如何运用它来设计和实现基本的数字电路,这对于学习者来说是一个重要的实践环节,能够帮助他们为后续的复杂系统设计打下坚实的基础。

442 浏览量

2022-06-26 上传

2022-06-19 上传

125 浏览量

2021-09-17 上传

2022-06-28 上传

2021-09-17 上传

dou19890806_

- 粉丝: 3

最新资源

- 实用机器学习与数据挖掘技术

- ASP.NET 2.0+SQL Server实战:从酒店管理到连锁配送系统

- STL源码深度剖析:侯捷著《TheAnnotatedSTLSource》

- Java编程规范详解与实践指南

- Windows Socket IO模型详解:从select到IOCP

- 提升WinXP性能与效率的10大操作技巧

- MODBUS协议详解:串行链路与TCP/IP通信

- SSH配置指南:初学者必读

- Oracle入门指南:从开发到管理

- C#实战:NUnit 2版《Pragmatic Unit Testing》2007年专业指南

- Excel2003函数大全:从基础到高级应用

- 满智EMSFLOW工作流开发与应用指南

- ASP+ACCESS构建的在线图书销售系统毕业设计

- HTML基础知识:文字与段落格式控制

- HTML入门:超文本标记语言基础教程

- JAVA技术框架与应用接口综述