CRC硬件电路详解与Verilog实现

需积分: 9 22 浏览量

更新于2024-09-13

收藏 1.15MB PDF 举报

本资源是一份关于循环冗余校验(Cyclic Redundancy Check, CRC)硬件电路实现的详细资料,涵盖了CRC16的具体计算方法、电路结构以及优化策略。CRC是一种广泛应用于数据传输错误检测的算法,它通过在数据后面附加一段固定长度的校验码来检测数据在传输过程中是否发生错误。

在CRC的实现部分,资料首先介绍了CRC16的生成多项式,如x16+x15+x2+1,这种16位的CRC算法可以检测单个错误、双位错误以及小于16位的突发错误。CRC的计算过程是基于一系列的寄存器(register),每个寄存器由一个公共时钟驱动,通过异或门(XOR gates)实现加法操作。初始值设置为16'hFFFF,即十六进制的65535,这有助于后续的计算。

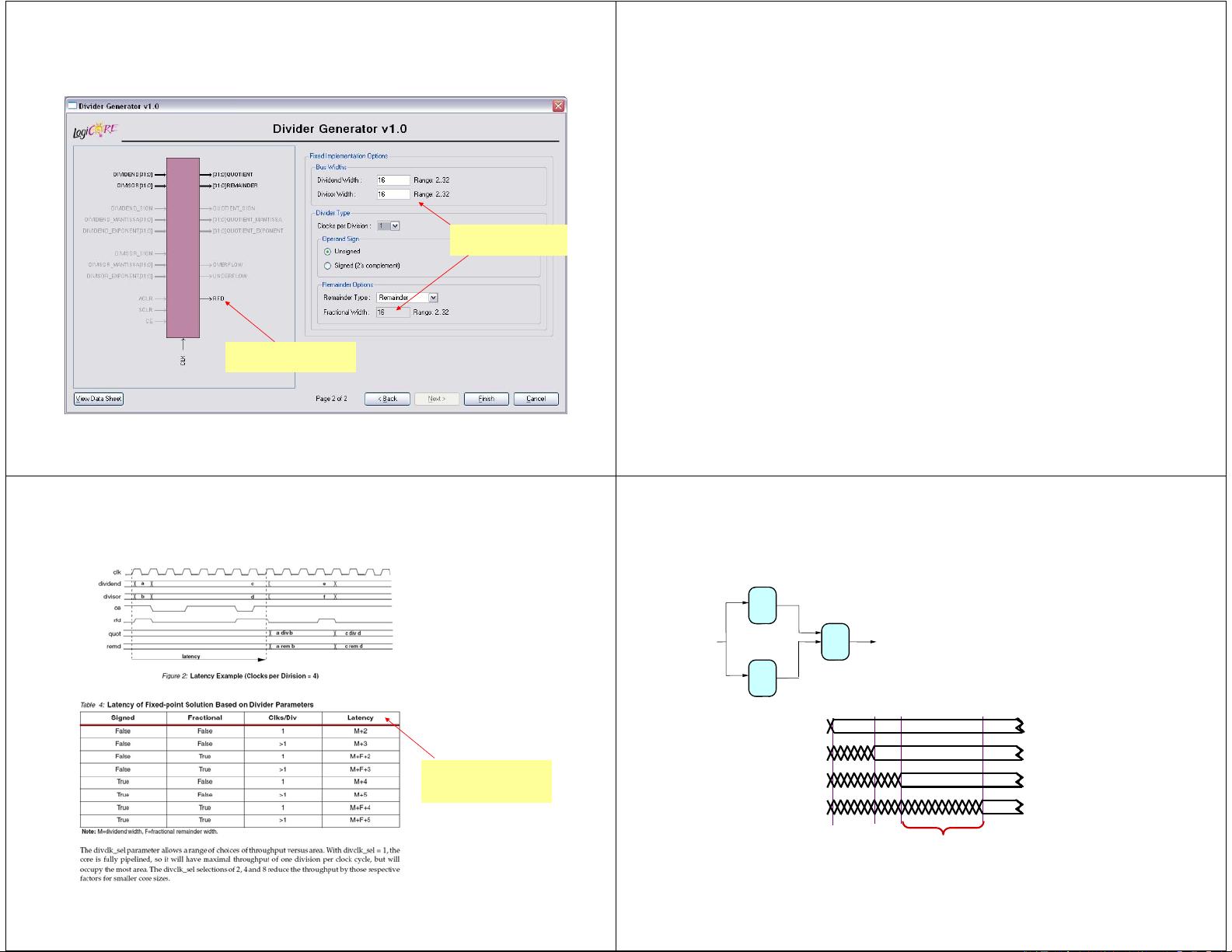

电路设计方面,资料提到使用序列除法器(Sequential Divider)的概念,当除数和被除数都是N位时,可以通过构建一个逐位处理的电路,每次进行一次单次减法操作,并重复N次完成整个计算。这种方法适用于无符号数运算,如果涉及有符号数,需要额外处理符号位。

资料还提及了流水线(Pipelining)技术,通过将计算步骤分解并行化,可以提高CRC计算的吞吐量(Throughput),从而提升整体性能。流水线可以减少延迟(Latency),使得数据处理更快速。此外,资料提到了重新定时(Retiming)技巧,这是优化电路的一种手段,通过调整逻辑门的布局和时序,可以改善电路的性能。

最后,资料还提到了Verilog编程语言中的数学函数,虽然具体没有详细列出,但可以推测这些函数可能用于描述CRC电路的逻辑行为和实现细节。Verilog是硬件描述语言,常用于编写和仿真数字电路,包括CRC的相关逻辑电路。

总结来说,这份资料提供了CRC16的实现原理、硬件电路设计方法、以及针对性能优化的策略,包括流水线和Verilog编程的应用。对于从事嵌入式系统设计、通信协议开发或数字信号处理等领域的人来说,这份资料是非常实用的参考资料。

115 浏览量

2022-03-14 上传

2009-12-22 上传

2019-08-29 上传

2022-01-18 上传

2019-12-01 上传

2021-03-19 上传

2021-11-27 上传

2008-01-31 上传

John智

- 粉丝: 0

- 资源: 1

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查