基于EDA技术的FPGA电子钟设计与VHDL实现

需积分: 7 2 浏览量

更新于2024-07-25

收藏 1.09MB DOC 举报

"这篇毕业设计论文主要探讨了使用EDA技术构建电子钟的过程,涉及了EDA的基本概念,FPGA的原理及应用,以及VHDL硬件描述语言的介绍。"

在电子设计自动化(EDA)领域,EDA技术是现代电子系统设计的核心工具。它整合了CAD、CAM、CAT和CAE的功能,通过硬件描述语言如VHDL,使得设计者能够在计算机上进行逻辑设计、优化、布局布线和仿真等一系列工作,大大提高了设计效率和准确性。EDA不仅简化了设计流程,还降低了设计成本,使得复杂电子系统的开发变得更加便捷。

FPGA(现场可编程门阵列)是EDA技术中的关键组件,它提供了高度灵活的可编程能力。与传统的ASIC相比,FPGA允许设计者在产品上市后仍能进行功能修改和优化,适应不断变化的市场需求。FPGA有多种配置模式,如并行主模式、主从模式、串行模式和外设模式,这使得它们能够适应不同的应用场景和系统架构。

VHDL,全称为Very High Speed Integrated Circuit Hardware Description Language,是广泛使用的硬件描述语言。它包含实体、构造体、配置、包集合和库五个主要组成部分,分别用于描述系统的外部接口、内部结构、元件装配、共享资源和预编译程序包。VHDL的强大之处在于其支持结构、数据流和行为的混合描述,使得设计者可以用过程语句来表达行为,用数据流描述来体现电路的逻辑,从而涵盖了从高层次系统模型到低层次电路细节的各种设计层面。

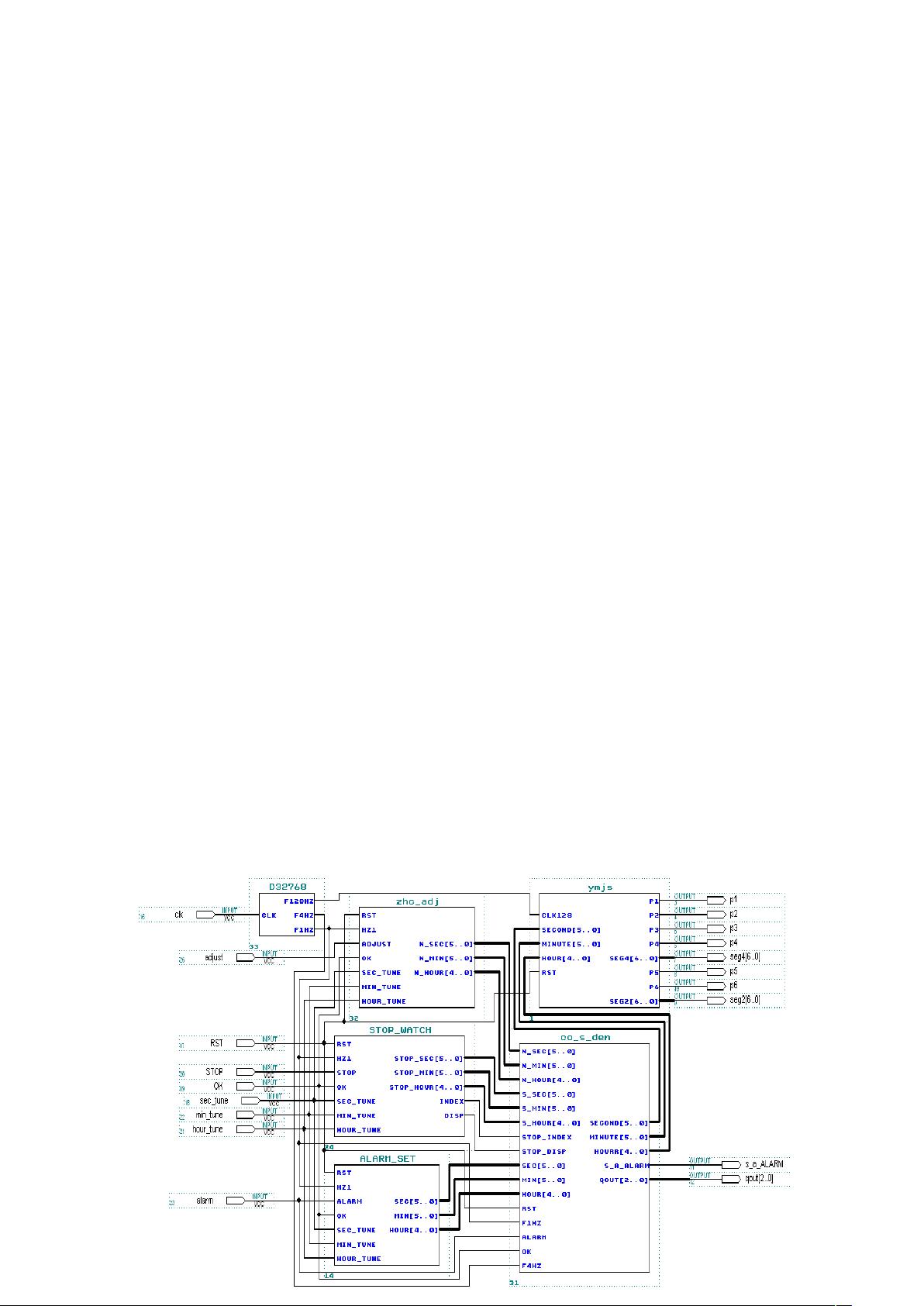

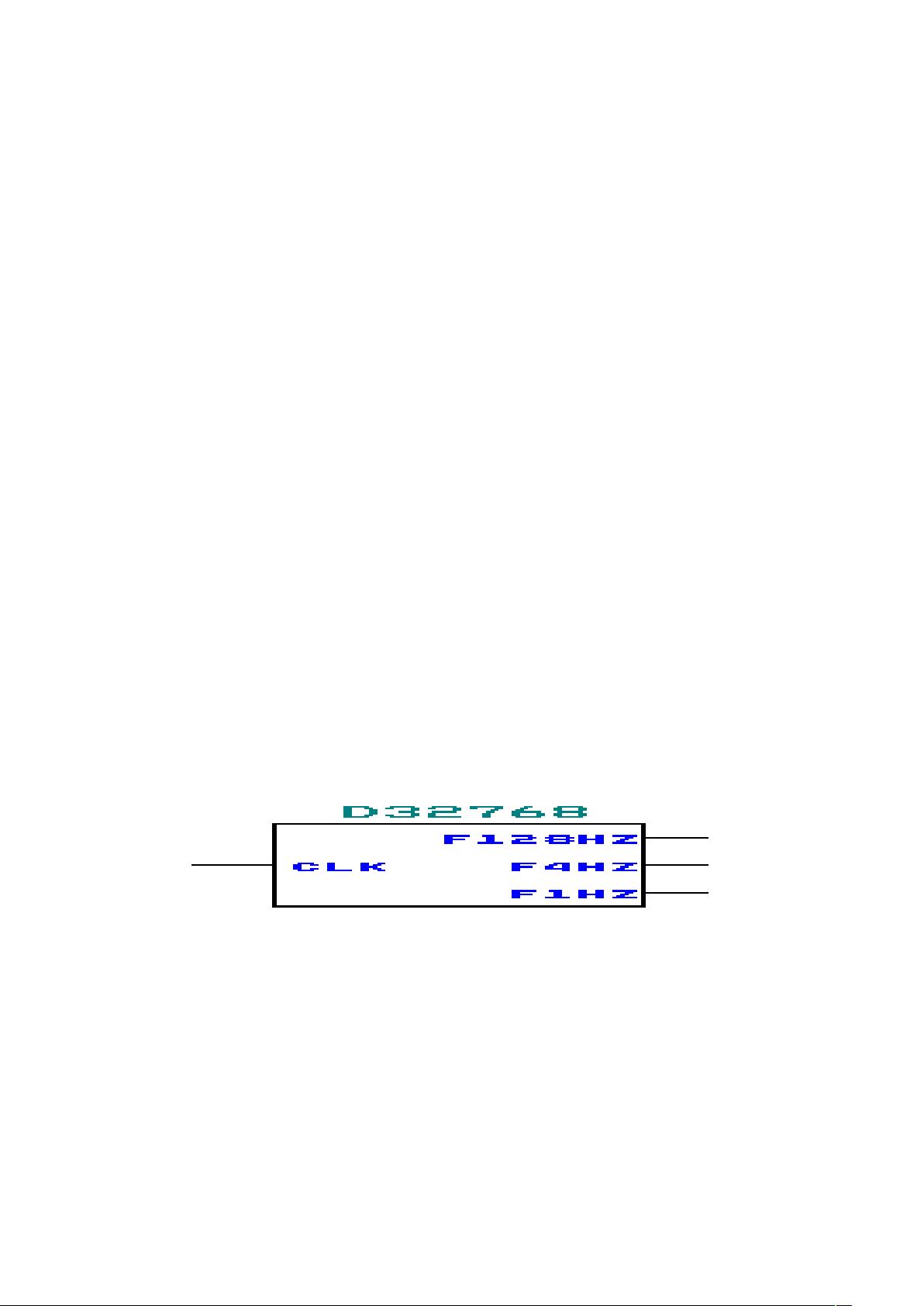

在构建电子钟的过程中,设计者首先需要定义电子钟的系统需求,包括时间显示、计时功能等,并用VHDL编写描述这些功能的代码。接着,使用EDA工具进行逻辑综合,将VHDL代码转化为FPGA可以理解的逻辑门级表示。然后,通过布局布线将逻辑门分配到FPGA的具体逻辑单元中。最后,将配置数据烧录到FPGA中,实现电子钟的硬件运行。

这篇毕业设计论文深入探讨了基于EDA技术的FPGA电子钟设计,涵盖了从理论到实践的全过程,旨在让学生理解和掌握电子系统设计的关键技术和方法。通过这样的项目,学生不仅可以学习到硬件描述语言VHDL的使用,还能了解到FPGA的工作原理及其在实际应用中的配置和编程技巧,为未来从事电子设计工作打下坚实基础。

180 浏览量

2022-05-04 上传

萧旷_a6s

- 粉丝: 0

- 资源: 1

最新资源

- snake-js:带有Javascript和HTML5的Snake

- badges-and-schedules:熨斗学校实验室

- ArtCenterGame

- mywonkysounds:SoundManger 2 音板! 我的声音!

- birdinginvermont.com

- Usso:sso统一登录系统

- Design-Algorithm-Homework

- MonadicRP:GHC Haskell中的相对论编程

- monolithic-sample

- vue-shop:Vue + Element UI电商后台管理系统演示

- Neurotypical-mode:一种Chrome扩展程序,可关闭除Microsoft Stream或Manaba之外的所有选项卡

- observ-conference:实验

- module-blog-graph-ql:Magento 2 Blog GraphQL扩展。 为Magefan博客模块提供GraphQL端点

- Excel模板00现金日记账.zip

- Naive-Bayes-Classifier

- SmartFactory