5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

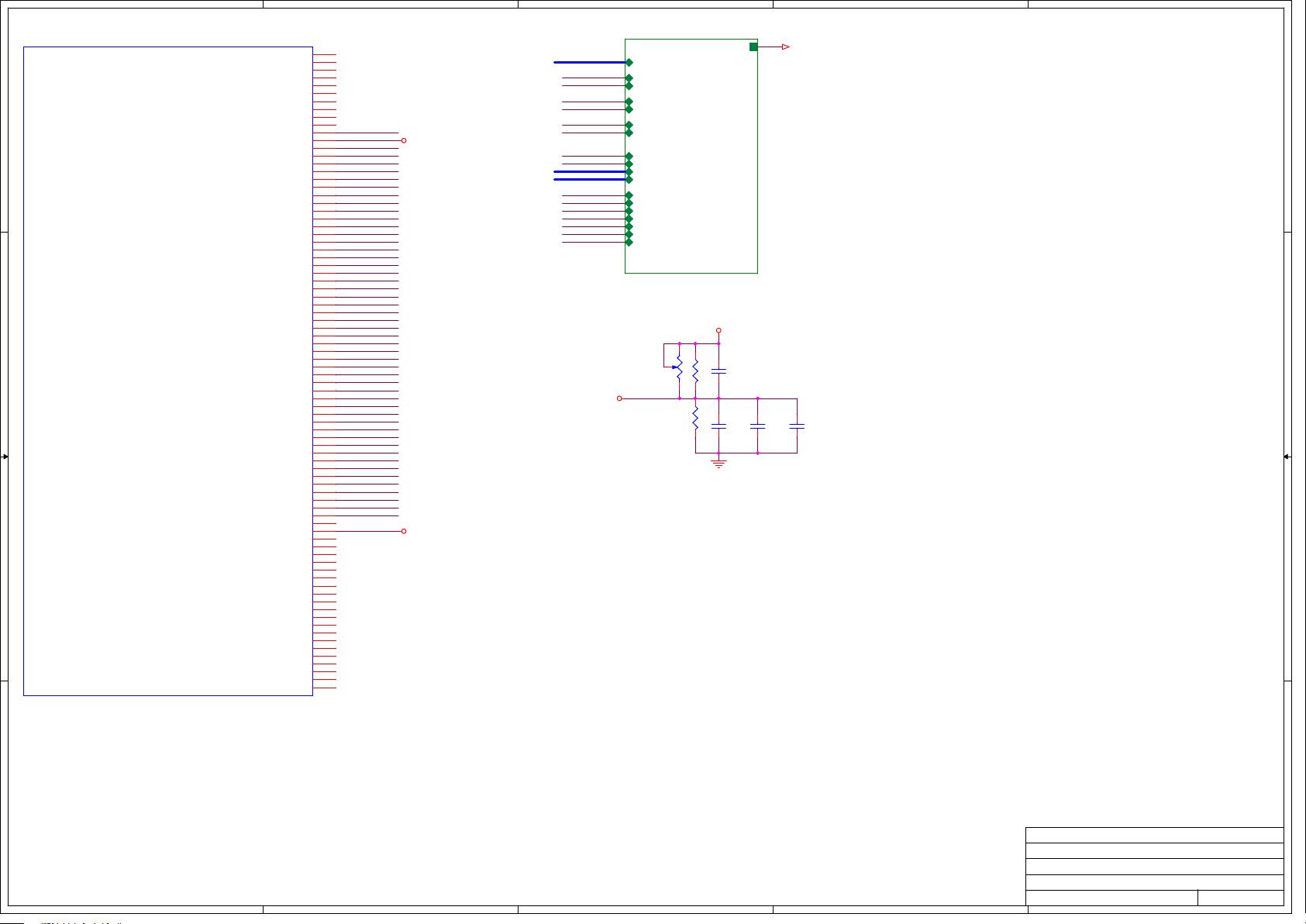

A_DDR3_VREF

D1V5

A_DDR3_VREF

GND

D1V5

A_DDR3_VREF

REV:

Date:

Sheet of

Title:

File:

Friday, January 07, 2022

3 22 A0

深圳市紫光同创电子有限公司

P02I50AS01_A0

03.PGL50G_FBG484_BANK1_DDR3_x16

REV:

Date:

Sheet of

Title:

File:

Friday, January 07, 2022

3 22 A0

深圳市紫光同创电子有限公司

P02I50AS01_A0

03.PGL50G_FBG484_BANK1_DDR3_x16

REV:

Date:

Sheet of

Title:

File:

Friday, January 07, 2022

3 22 A0

深圳市紫光同创电子有限公司

P02I50AS01_A0

03.PGL50G_FBG484_BANK1_DDR3_x16

R21

1.69K

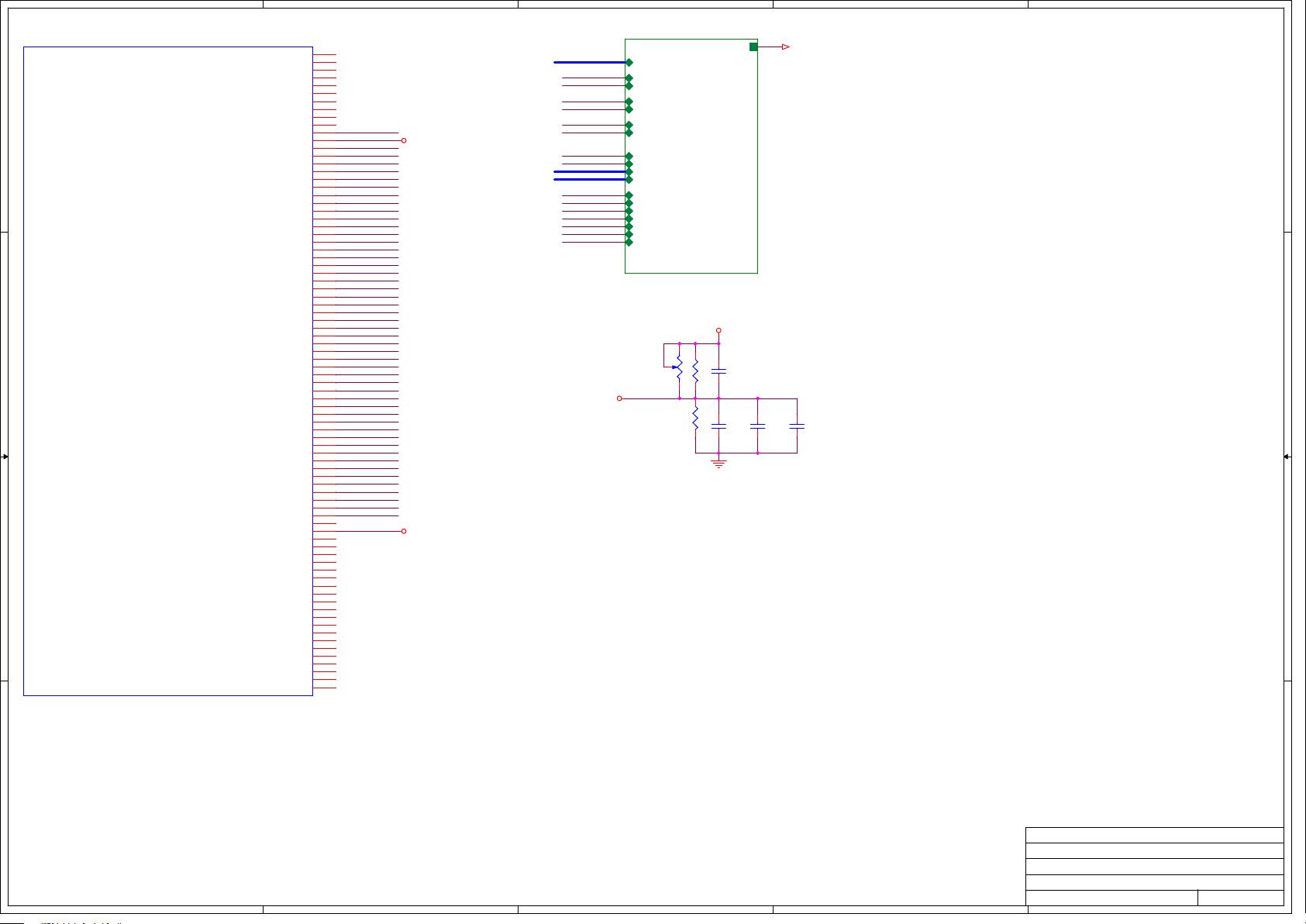

U1-2

PGL50G_FBG484

DIFFI_B1_0P/ADR25/DQ0_B1/DQ0_B1_GATE_OUT

C19

DIFFI_B1_0N/ADR24/VREF_B1/DQ0_B1/DQ0_B1_GATE_IN

B20

DIFFI_B1_1P/DQ0_B1

G16

DIFFI_B1_1N/DQ0_B1

G17

DIFFI_B1_2P/DQS0_B1

F16

DIFFI_B1_2N/DQS0#_B1

F17

DIFFI_B1_11P/DQ1_B1

B21

DIFFI_B1_11N/DQ1_B1

B22

DIFFI_B1_12P/DQ1_B1

A20

DIFFI_B1_12N/DQ1_B1

A21

DIFFI_B1_13P//DQ2_B1

H16

DIFFI_B1_13N/VREF_B1/DQ2_B1

H17

DIFFI_B1_14P/ADR23/DQ2_B1

D19

DIFFI_B1_14N/ADR22/DQ2_B1

D20

DIFFI_B1_15P/ADR21/DQS2_B1

F18

DIFFI_B1_15N/ADR20/DQS2#_B1

F19

DIFFI_B1_16P/ADR19/DQ2_B1

D21

DIFFI_B1_16N/ADR18/DQ2_B1

D22

DIFFI_B1_17P/ADR17/DQ2_B1

C20

DIFFI_B1_17N/ADR16/DQ2_B1

C22

DIFFI_B1_18P/ADR15/DQ2_B1

G19

DIFFI_B1_18N/ADR14/DQ2_B1

F20

DIFFI_B1_19P/ADR13/DQ2_B1/DQ2_B1_GATE_OUT

H19

DIFFI_B1_19N/ADR12/DQ2_B1/DQ2_B1_GATE_IN

H18

DIFFI_B1_20P/ADR11/DQ3_B1

E20

DIFFI_B1_20N/ADR10/DQ3_B1

E22

DIFFI_B1_21P/ADR9/DQ3_B1

J17

DIFFI_B1_21N/ADR8/DQ3_B1

K17

DIFFI_B1_22P/ADR7/DQS3_B1

F21

DIFFI_B1_22N/ADR6/DQS3#_B1

F22

DIFFI_B1_23P/ADR5/DQ3_B1

H20

DIFFI_B1_23N/ADR4/DQ3_B1

J19

DIFFI_B1_24P/DQ3_B1

G20

DIFFI_B1_24N/DQ3_B1

G22

DIFFI_B1_25P/GCLK11/PLL1_CLK8/PLL4_CLK0/PLL5_CLK0/DQ3_B1

K20

DIFFI_B1_25N/GCLK10/PLL1_CLK9/PLL4_CLK1/PLL5_CLK1/DQ3_B1

K19

DIFFI_B1_26P/GCLK9 /PLL1_CLK10/PLL4_CLK2/PLL5_CLK2/DQ3_B1/DQ3_B1_GATE_OUT

H21

DIFFI_B1_26N/GCLK8/PLL1_CLK11/PLL4_CLK3/PLL5_CLK3/DQ3_B1/DQ3_B1_GATE_IN

H22

DIFFI_B1_27P/GCLK7/PLL2_CLK0/PLL3_CLK0/DQ4_B1

M20

DIFFI_B1_27N/GCLK6/PLL2_CLK1/PLL3_CLK1/DQ4_B1

L19

DIFFI_B1_28P/GCLK5/PLL2_CLK2/PLL3_CLK2/DQ4_B1

J20

DIFFI_B1_28N/GCLK4/PLL2_CLK3/PLL3_CLK3/DQ4_B1

J22

DIFFI_B1_29P/ADR3/XTAL_A/DQ4_B1

K21

DIFFI_B1_29N/ADR2/XTAL_B/DQ4_B1

K22

DIFFI_B1_30P/ADR1/DQS4_B1

L20

DIFFI_B1_30N/ADR0/DQS4#_B1

L22

DIFFI_B1_31P/BFCS_N/DQ4_B1

M21

DIFFI_B1_31N/BFOE_N/DQ4_B1

M22

DIFFI_B1_32P/BFWE_N/DQ4_B1

N20

DIFFI_B1_32N/BLDC/DQ4_B1

N22

DIFFI_B1_33P/BHDC/DQ5_B1/DQ4_B1_GATE_OUT

P21

DIFFI_B1_33N/DQ5_B1/DQ4_B1_GATE_IN

P22

DIFFI_B1_34P/DQ5_B1

R20

DIFFI_B1_34N/DQ5_B1

R22

DIFFI_B1_35P/DQS5_B1

T21

DIFFI_B1_35N/DQS5#_B1

T22

DIFFI_B1_36P/DQ5_B1

U20

DIFFI_B1_36N/DQ5_B1

U22

DIFFI_B1_37P/DQ5_B1

V21

DIFFI_B1_37N/DQ5_B1

V22

DIFFI_B1_38P/DQ5_B1

M19

DIFFI_B1_38N/VREF_B1/DQ5_B1

N19

DIFFI_B1_39P/DQ5_B1/DQ5_B1_GATE_OUT

K16

DIFFI_B1_39N/DQ5_B1/DQ5_B1_GATE_IN

J16

DIFFI_B1_40P/DQ6_B1/DQ6_B1_GATE_OUT

M16

DIFFI_B1_40N/DQ6_B1/DQ6_B1_GATE_IN

L15

DIFFI_B1_41P/DQ6_B1

P19

DIFFI_B1_41N/DQ6_B1

P20

DIFFI_B1_42P/DQS6_B1

W20

DIFFI_B1_42N/DQS6#_B1

W22

DIFFI_B1_43P/DQ6_B1

L17

DIFFI_B1_43N/DQ6_B1

K18

DIFFI_B1_51P/DQ7_B1

U19

DIFFI_B1_51N/DQ7_B1

V20

DIFFI_B1_52P/DQ7_B1

M17

DIFFI_B1_52N/DQ7_B1

M18

DIFFI_B1_53P

P17

DIFFI_B1_53N

N16

DIFFI_B1_54P

P18

DIFFI_B1_54N

R19

DIFFI_B1_55P/AWAKE_1

T19

DIFFI_B1_55N/DOUT_BUSY

T20

DDR3_X16_A

DDR3_x16

DDR3_DQ[15..0]

DDR3_DQS1_P

DDR3_DQS1_N

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DM1

DDR3_DM0

DDR3_A[14..0]

DDR3_BA[2..0]

DDR3_CLK_P

DDR3_CLK_N

DDR3_WE

DDR3_RAS

DDR3_CAS

DDR3_ODT

DDR3_CS

DDR3_CKE

DDR3_RESET

VCCDDR

R22

1K

C2

100nF

25V

10%

C818

100nF

25V

10%

C817

100nF

25V

10%

C1

100nF

25V

10%

R20

5K

A_DDR3_DQ[15..0]

A_DDR3_A[14..0]

A_DDR3_BA[2..0]

A_DDR3_RESET

A_DDR3_CKE

A_DDR3_ODT

A_DDR3_CAS

A_DDR3_RAS

A_DDR3_W E

A_DDR3_CLK_P

A_DDR3_CLK_N

A_DDR3_DM1

A_DDR3_DM0

A_DDR3_DQS0_P

A_DDR3_DQS0_N

A_DDR3_DQS1_P

A_DDR3_DQS1_N

A_DDR3_DQ14

A_DDR3_DQ15

A_DDR3_DQ13

A_DDR3_DQS1_P

A_DDR3_DQS1_N

A_DDR3_DQ12

A_DDR3_RESET

A_DDR3_A13

A_DDR3_A14

A_DDR3_A11

A_DDR3_CKE

A_DDR3_A12

A_DDR3_A8

A_DDR3_A9

A_DDR3_A10

A_DDR3_A4

A_DDR3_W E

A_DDR3_BA2

A_DDR3_A7

A_DDR3_A2

A_DDR3_BA0

A_DDR3_BA1

A_DDR3_A0

A_DDR3_A1

A_DDR3_CLK_P

A_DDR3_CLK_N

A_DDR3_A3

A_DDR3_ODT

A_DDR3_A5

A_DDR3_A6

A_DDR3_RAS

A_DDR3_CAS

A_DDR3_DM1

A_DDR3_DM0

A_DDR3_DQ4

A_DDR3_DQ5

A_DDR3_DQ6

A_DDR3_DQ7

A_DDR3_DQS0_P

A_DDR3_DQS0_N

A_DDR3_DQ2

A_DDR3_DQ3

A_DDR3_DQ0

A_DDR3_DQ1

A_DDR3_DQ8

A_DDR3_DQ9

A_DDR3_DQ10

A_DDR3_DQ11

A_DDR3_CS

A_DDR3_CS