数字化时钟设计:计数器与动态显示

本篇文档主要介绍了数字钟设计的实验项目,它旨在通过EDA技术来实现一个功能丰富的电子钟。实验分为三个关键部分:

1. 计数部分:这是核心组件,利用两个模60的加法计数器来分别计算分钟和秒钟,确保精确的计时。这两个计数器负责实时更新并显示时间,确保时间单位的连续性。同时,还有一个可转换为12或24小时制的小时计数器,这允许用户根据需求选择不同的时间显示模式。

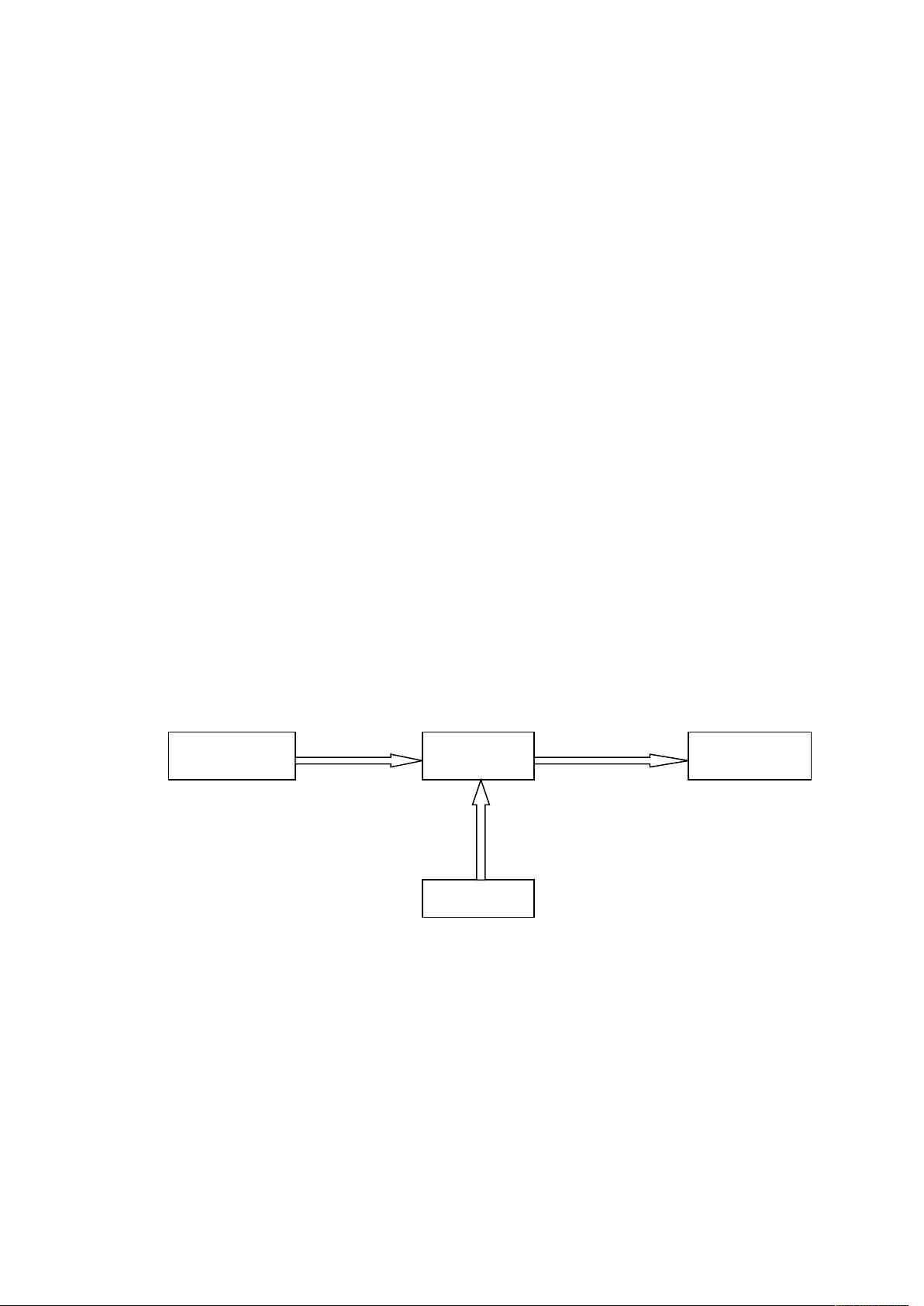

2. 状态切换控制电路:这部分电路的作用是管理不同操作状态的切换,比如计时、调时、调分、调秒以及调整小时制式。通过一个功能键,用户能够轻松地在这些模式之间切换,提高了用户体验的灵活性。

3. 动态数码管扫描电路:由于实验箱没有提供1Hz的时钟脉冲,需要设计一个分频器来确保稳定的数码管显示。分频器将高频时钟信号降低到1Hz,以便于精确驱动数码管显示每一个小时、分钟、秒的动态变化。

在整个设计过程中,学生需要熟悉EDA技术开发流程,如使用Quartus II集成开发环境进行编程和设计,并且掌握PH-1V型实验装置的操作。实验的目标是实现动态扫描显示,即时间的即时更新,以及用户交互功能,如调节时间和切换显示模式。

实验设计中涉及的编程语言如Verilog或 VHDL,以及相关的硬件描述语言,展示了理论知识与实践操作的结合,对于理解和应用数字逻辑设计有着重要意义。通过这个实验,参与者不仅锻炼了硬件设计能力,也加深了对计数器、状态机和时序逻辑的理解。

这个数字钟设计实验是一个综合性的项目,涵盖了数字逻辑设计、状态机控制、频率变换等多个知识点,是学习者提升电子系统设计技能的重要实践平台。

183 浏览量

2011-07-04 上传

2010-11-29 上传

2024-01-13 上传

2024-06-04 上传

2023-12-09 上传

2023-05-11 上传

2023-05-28 上传

2023-06-07 上传

chewbee88

- 粉丝: 0

- 资源: 5

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析